(51) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Процессор | 1986 |

|

SU1332328A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для опроса и сбора аналоговойиНфОРМАции C СЕТОчНОй элЕКТРОМОдЕли | 1979 |

|

SU809215A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1354192A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968813A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

1 -

Изобретение относится к вычисли тельной технике, в частности к apиф метическим устройствам, и может быть использовано в высокопроизводительных ЭВМ.

Известно устройство для вычйсле- ;ния значений тригонометрических функций , содержащее регистры, элементы И, ИЛИ, преобразователи прямого кода в дополнительный, последователь-.„ ные комбинационные сумматоры, блоки выдачи, триггеры, двоичный счетчик, блок сравнения, счетчик итераций, дешифратор, блок задания констант, блок управления. Для вычисления зна- ,5 чений тригонометрических функций используется последовательный принцип обработки информации по итерационным формулам 1 i

Недостатком устройства является 20 низкое быстродействие и ограниченные Функциональные возможности.

Известно также устройство для вычисления значений синуса и косинусе

которое содержит счетчик аргумента, формирователь кода начальногр приращения, регистр приращений, накапливающий сумматор, дешифратор, коммутатор кодов, блок вычисления кода угла, блок выдачи информации, блок сравнения. В устройстве формируется текущий код угла и соответствукяцее значение функций по поступающей на вход последовательности импульсов, При совпадении текущего и заданного кодов угла на выход устройства поступает .соответствующий код значения тригонометрической функции С2.

Недостатком указанного устройства является низкое быстродействие и oi- раниченные функциональные возможности.

Наиболее близким является устройство для вычисления полинома, содержащее блок памяти, блок управления, входной коммутатор два коммутатора, три регистра, три группы входных и две группы выходных регистров. две группы элементов И, два преобразователя кодов частичных произведений в двухрядный код, сумматор и регистр результата. ; Выход блока памяти соединен с пер :Bbw входом входного коммутатора, . второй и третий входы входного коммутатора соединены с третьим и четвертым выходами блока управления, первый выход которого соединение вхо дом блока памяти. Первый выход входного коммутатора соединен с информационным входом первого регистра и информационными входами регистров второй группы входных регистров. Вто рой выход входного ..коммутатора соединен с информационными входами второго итретьего регистров.;Выходы первого, второго регистров соединены с первым и вторым входами первого коммутатора, третий вход которого соединен с выходами регистров первой группы входиь1х регистров. I. Выходы регистров второй группы входных регистров соединены с первым входом второго коммутатора, второй вход которого .соединен с выходом третьего регистра. Выходы регистров третьей группы входных регистров соединены с третьим входом второго коммутатора. Информационные- вхо- / ды рЬгистррв первой и третьей групп входных регйстров соединены со ответственно с выходом первого выходного коммутатора и третьим выходом второго выходного-коммутатора. К перво.му, второму и третьему входам первой группы элементов И подключены соответствующие выходы первого коммутатора. К первому, второму и треть ему входам второй группы элементов И подключены соответствующие ыходы второго коммутатора. Четвертые входы первой и второй группы элементов И соединены с первыми выходами соответственно второго и первого коммутаторов. Четвертые выходы первого и второго коммутаторов соединены с вхо дом второго преобразователя кода час тичных произведений в двухрядный код Выходы первой и второй групп .элементов И соединены с входами соответственно первого и второго преобразователей кода частичных произведений в двухрядный код, выходы которых соединены с информационными входами регистров соответственно первой и второй групп выходных регистров. Первые входы первого и второго выходных коммутаторов соединены с выходами регистров соответственно первой и второй групп выходных регистров. Второй выход второго выходного коммутатора соединен с информационными входами регистров второй группы входных регистров. Первый -выход второго выходного коммутатора соединен с входом сумматора, выход которого подключен к информационному входу регистра результата. К управляющим входам регистра результата, первого, второго, третьего регистров, к управляющим входам регистров первой, второй. третьей групп входных и первой, второй групп выходных регистров подключен девятый выход блока управления, второй и шестой выходы которого сое- . динены соответственно с третьим и четвертым входами второго выходного коммутатора. Пятый выход блока управления соединен с вторыми входами первого и второго выходных коммутаторов. Седьмой, восьмой, десятый, одиннадцатый и двенадцатый выходы блока управления соединены соответственно с четвертыми, пятыми, шестыми седьмыми и восьмыми входами первого и второго коммутаторов. Блок управления содержит генератор импульсов, элемент ИЛИ, счетчик и двадцативосьмивыходной элемент задержки. При этом выход генератора импульсов соединен с входом элемента задержки и первым входом элемента ИЛИ, второй, третий и четвертый входы которого соединены соответственно с четвертым, пятым и четырнадцатым выходами элемента задержки. Выход элемента ИЛИ соединен с первым входом счетчика, второй вход которого соединен с двадцать восьмым выходом элемента задержки, выход счетчика подключен к первому выходу блока управления и первому, шестому и пятнадцатому выходам элемента задержки. Второй выход блока управления соединен с двадцать седьмым выходом элемента задержки, третий - с вторым, четвертый - с шестым, одиннадцатым и шестнадцатым выходами элемента задержки, пятый с двенадцатым, семнадцатым, двадцать первым, двадцать третьим и двадцать пятым, шестой - с седьмым, седьмой с третьим, восьмой - с восьмым и тринадцатым, девятый - с двадцать восьмым, десятый - с восемнадцатым. одиннадцатый - с шестнадцатым, двадцатый выход блока управления сое- ; динен с двадцатым, двадцать вторым и двадцать четвертым выходами элемента задержки. Работа прототипа основана на параллельном вычислении двух частей полинома по схеме Горнер причем промежуточные результаты вычислений используются в виде двухрядного кода СЗ. Недостатком прототипа являются ограниченные функциональные возможности, ввиду невозможности выполнения им арифметических операций сложения вычитания, умножения и деления. Цель изобретения - расширение функциональных возможностей устройства путем обеспечения возможности . выполнения арифметических операций сложения, вычитvaния, умножения и деления. Поставленная цель достигается тем, что вычислительное устройство, содержащее блок памяти, входной коммутатор, два коммутатора, два выходных коммутатора, три регистра, три группы входных и две группы выходных регистров, две группыэлементов И, дв преобразователя кода частичных произведений в двухрядный код, сумматор регистр результата, причем выходы блока памяти соединены с- одноименны-. ми входами первой группы входов входного коммутатора, первая группа выходов которого соединена с одноименными входами первого регистра и входных ре гистров второй группы, вторая группа выходов входного коммутатора соединена с одноименными входами второго и третьего регистров, выходы первого выходного коммутатора соединены с вхо дами входных регистров первой группы выходы первого, второго регистров и входных регистров первой группы подключены к соответствующим входам первой, второй и третьей трупп входов перво го коммутатора,выходы первой,второй и третьей групп выходов которого соединены соответственно с первыми, вторыми и третьими входами соответствующих элементов И первой группы, выходы входных регистров вто,рой группы, выходы третье го регистрам выходы входных регистров третьей групЪы соединены с одноименными входами соответственно первой, второй и трет ей групп входов второго коммутатора, выходы первой, второй и третьей грулп ВЫХОДОВ которого соединены соответственно с первыми, вторыми и т етьими входами одноименных элементов И второй группы, выходы четвертой группы вь ходов первого и второго коммутаторов соединены с четвертыми входами соответственно элементов И второй группы и элементов И первой группы, выходы пятой группы выходов первого, второго коммутаторов и выходы элементов И второй группы подключены к соответствующим входам второго преобразователя кодов частичных произведений в двухрядный код, выходы которого соединены с одноименными входами выходных регистров второй группы, выходы элементов И первой группы соединены с бходами первого преобразователя кодов частичных произведений в двухрядный код, выходы которого соединены с одноименными входами выходных регистров первой группы, выходы выходных регистров первой и второй групп соединены с одноименными входами первой группы входов первого и второго выходных коммутаторов соответственно, выходы первой группы выходов второго выходного коммутатора соединены с одноименными входами сумматора, выходы второй группы выходов этого коммутатора подключены к одноименным входам входных регистров второй группы, выходы третьей группы - к одноименным входам входных регистров третьей группы, выходы первой группы выходов сумматора соединены с одноименными входами регистра результата, выходы которого подключены к шине результата устройства, содержит блок управления, преобразователь двухрядного, кода в дополнительный двухрядный код, преобразователь двоичного кода в дополнительный код, четвертый регистр, третий коммутатор, причем выходы четвертой группы выходов второго выходного коммутатора соединены с одноименными входами преобразователя двухрядного кода в дополнительный двухрядйый код, выходы которого-соединены с одноименными входами входных регистров второй группы, входы первой группы входов третьего коммутатора соединены с соответствующими выходами четвертого регистра, входы которого подключены к одноименным выходам первой группы выходов сумматора, выходы третьего коммутатора подключены к одноименным входам преобразователя двоичног9 кода 1 8 дополнительный код, выходы которого подключены к соотве тствующим входам регистра результата, первая входная шина устройства соединена с входами второй группы входов входного коммутатора, вторая входная шина устройства - с входами четвертой группы входов входного коммутатора, третья входная .шина устройства соединена с первой группой входов блока управления, четвертая входная шина устройства - с первым входом блока управления, пятая входная шина устройства с вторым входом блока управления, шестая входная шина устройства - с третьим вxoдo J блока управления, первый выход сумматора подключен к четвертому входу блока .управления, первый выход блока управления подключен к второму входу первого выходного ком мутатора, второй выход блока управления подключен к второму входу третьего коммутатора, выходы первой группы выходов блока управления соответственно соединены с входами первой груп пы входов первого коммутатора, выхоп ды второй группы выходов блока управления соединены соответственно с входами первой группы входов входного коммутатора, выходы третьей группы вьг)ходов блока управления подключены к одноименным входам блока памяти, выходы четвертой группы выходов блока управления соединены с одноимен ными входами первой группы входов вто цого коммутатора, выходы пятой группы выходов блока управления соответст венно соединены с входами первой груп пы входов второго выходного коммутаi , . Кроме того, блок управления содержит регистр адреса констант, постоянную память, группу элементов задержки, регистр адреса микрокоманд, регистр кода операции, дешифратор, первый j второй и третий элементы задержки, элемент .ИЛИ-НЕ, элемент равнозначности, элемент неравнозначности, пять элементов И, три элемента НЕ, три трехвходовых элемента И, элемент ИЛИ, триггер знака результата, причем выходы регистра адреса микрокоманд соединены с одноименными входами первой группы входов постоянной памяти, первые семь выходов постоянной памяти образуют адресную группу и соответственно соединены с входами груп пы элементов задержки, выходы которой соединены с одноименными входами регистра адреса микрокоманд, восьмой выход постоянной памяти является первым выходом блока управления, выходы постоянной памяти с девятого по пятнадцатый образуют первую группу выходов, с шестнадцатого по восемнадцатый - вторую группу выходов блока управления, с девятнадцатого по двадцать первый выходы постоянной памяти соединены с входами регистра адреса констант, выходы которого и двадцать второй выход постоянной памяти образуют третью группу выходов блока управления, пятнадцатый выход постоянной памяти и ее выходы с двадцать третьего по двадцать седьмой образуют четвертую группу выходов блока управления, выходь с двадцать восьмого по тридцать первый постоянной памяти - пятую группу выходов блока управления, тридцать второй выход постоянной памяти является вторым выходом блока управления, тридцать третий, тридцать четвертый и тридцать пятый выходы постоянной памяти соединены соответственно с входами третьего, второго и первого элементов задержки, входы регистра кода операции и регистра адреса микрокоманд образуют первую группу входов блока управления, первый вход блока управления соединен с вторым входом элемента ИЛИ, второй вход блока управления - с вторыми входами элемента равнозначности и элемента неравнозначности, с выходом третьего элемента НЕ, с вторым входом пятого элемента И и первым входом третьего трехвходового элемента И, третий вход блока управления - с первыми входами элемента равнозначности и элемента неравнозначности, четвертый - с входом .второго элемента НЕ и с третьим вхогдом третьего трехвходового элемента И, выход первого элемента задержки соединен с первым входом элемента ИЛИ, выход которого подключен к второму вхоДу постоянной памяти, выход второго элемента задержки соединен с первым входом первого элемента И, выход которого подключен к первому управляющему входу регистра адреса микрокоманд, выход третьего элемента задержки соединен с вторым входом первого трехвходового элемента И, выход которого подключен к второму управляющему входу регистра адреса микрокоманд, выход элемента неравнозначности соединен с первым входом второго элемента И и с вторым входом четвертого элемента И, выход элемента равнозначности соединен с первым входом третьего элемента И, выходы второго и третьего элементов И соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ, выход которого подключен к втррому входу первого элемента И, к первому входу первого трехвходового элемента И , к входу первого элемента НЕ, к второму входу второго трехвходового элемента И и к второму входу третьего трехвходового элемента И, выход второго элемента НЕ соединён с третьими входами первого и второго трехвходовых элементов И, выходьг .регистра кода операций соединены с соответствующими входами дешифратора , первый выход дешифратора соединен с вторым входом третьего эле;мента И, второй выход дешифратора ,с вторым входом второго элемента И, третий выход дешифратора - с пёрвым входом четвертого элемента И, выходы :четвертого, пятого элементов И, второго и третьего трехвходовых элементов И соединены с входом триггера знака результата, выход первого элемента НЕ соединен с первым входом пятого элемента И, выход третьего элемента НЕ соединен с первым входом второго трехвходового элемента И.

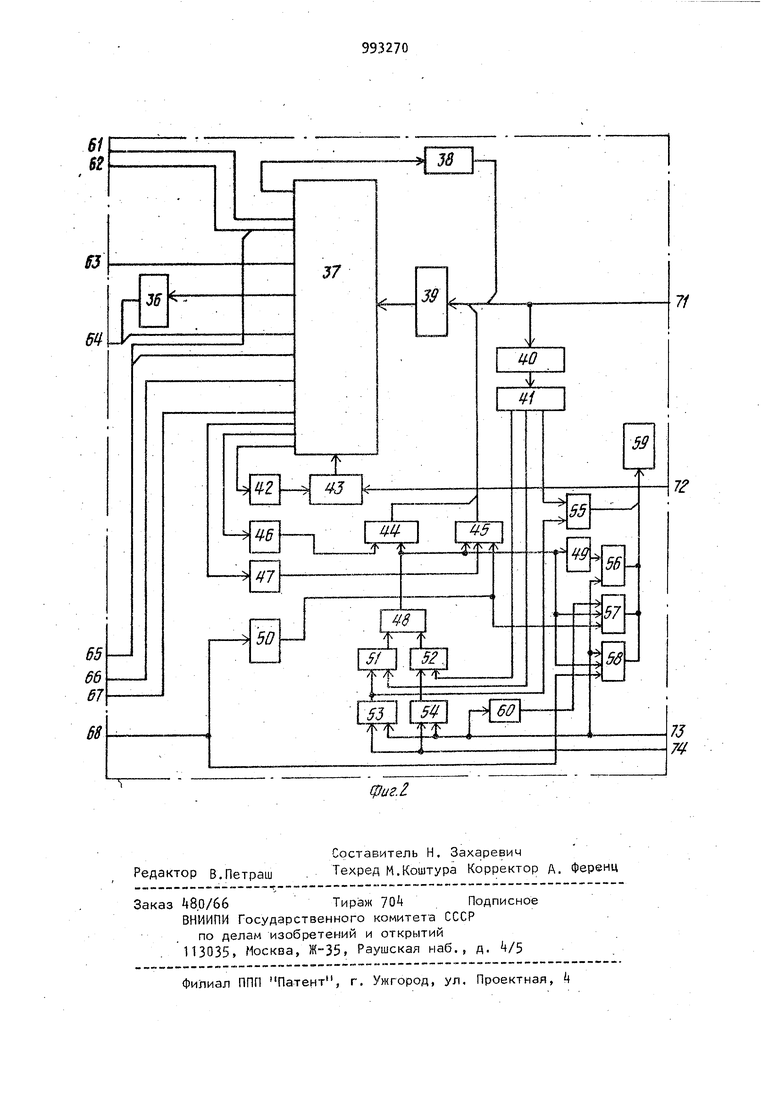

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - структурная схема блока управления.

Устройство содержит входной коммутатор 1, блок 2 памяти, первый 3 и второй регистры, первый 5 и второй 6 входные регистры первой группы 7 входных регистров, первый 8-и второй 9 входные регистры второй группы 10 входных регистров, третий регистр 11, первый 12 и второй 13 входные регистры третьей группы-1 входных регистров, первый 15 и второй 16 коммутаторы, первую 17 и вторую 18 группы элементов И, первый 19 и второй 20 преобразователи кода частичных произведений в двухрядный код, первый 21 и второй 22 выходные регистры первой группы 23 выходных регистров, первый 2 и второй 25 выходные регистры второй группы 26 выходных регистров, первый 27 и второй 28 выходные коммутаторы, преобразователь 29 двухрядного кода в доолнительный двухрядный код, сумматор 30, четвертый регистр 31 коммутатор 32, преобразователь 33 кода

в дополнительный код, регистр 3 результата, блок 35 управления, регистр 36 адреса констант, постоянную память 37, группу 38 элементов задержки, регистр 39 адреса микрокоманд, регистр lO кода операции, дешифратор , первый элемент 2 задержки, элемент ИЛИ k3, первый элемент И kk, первый трехвходовый элемент И 45, второй 46 и третий 7

элементы задержки, элемент ИЛИ-НЕ Ц8, первый и второй 50 элементы НЕ, второй 51 и третий 52 элементы И, элементы 53 неравнозначности, . элемент 5 равнозначности, четвертый 55 и пятый 5б элементы,И, второй 57 и третий 58 трехвходовые элементы И, триггер 59 знакарезультата третий элемент НЕ 60.

Блоки устройства соединены следующим образом. Первый выход 61 блока 35 управления подключен к второму входу первого выходного коммутатора 27, выходы которого соединены с входами входных регистров 5 и 6 первой группы 7 входных регистров. Первая группа 62 выходов блока 35 управления подключена к одноименным входам четвертой группы первого коммутатора 15, перв.ая, вторая и третья группы входов которого подключены соответственно к выходам первого регистра 3 второго регистра и к выходам первого и второго входных регистров 5 и 6 первой группы 7 входных регистров. Вторая группа 63 выходов блока 35 управления подключена к входам второй группы входного коммутатора 1 , первая гругтпа входов которого соединена с выходами блока 2 памяти, а входы последнего подключены к третьей группы 64 выходов блока 35 управления. Четвертая группа 65 выходов блока 35 управления соединена с четвертой группой

входов второго коммутатора 1б, первая, вторая и третья группы входов которого подключены соответственно к выходам входных регистров 8 м 9 второй группы 10 входных регистров, выходу третьего регистра 11, выходам входных регистров 12 и 13.третьей группы 14 входных регистров. Пятая группа 66 выходов блока 35 управления подключена к второй группе входов второго выходного коммутатора 28 третья группа выходов которого подключена к входам входных регистров 12 и 13 третьей группы входных ре гистров. Второй выход 67 блока 35 уп равления соединен с вторым входом коммутатора 32 выходы которого подключены к входам преобразователя 33 кода в дополнительный код, соединенного выходами с входами регистра 3 результата. Первая, вторая и третья группы выходов первого 15 и второго 16 коммутаторов подключены к соответствующим входам соответственно первой 17 и второй 18 групп элементов И, четвертые входы которых соединены с четвертыми группами выходов соответственно второго 16 и первого 15 коммутаторов. К входам второго преобразователя 20 кодов частичных произведений в двухрядный код, соединенно го выходами с входами регистров второй группы 26 выходных регистров, подключены пятые группы выходов первого 15 и второго 16 коммутаторов и выходы элементов И второй группы 18 элементов И. Выходы регистров второй группы 26 выходных регистров подключены к первой группе входов второг о выходного коммутатора 28, вт рая группа выходов которого соединена с входами регистров второй группы 10 входных регистров. Четвертая группа выходов .второго выходного ком мутатора 28 соединена с входами преобразователя 29 двухрядного кода в дополнительный двухрядный код, выходы которого подключены к входам регистров второй группы 10 входных регистров. К входам первого преобразователя 19 кодов частичных произведений в двухрядный код, соединенна го выходами с входами регистров первой группы выходных регистров 23, подключены выходы элементов И первой группы 17 элементов И. .Выходы регистров первой группы 23 выходных регистров соединены с первой группой входов первого выходного коммутатора 27. Первая группа выходо входного коммутатора 1 подключена к входам первого регистра ,к входам регистров второй группы 10 входных ре гистров. Вторая группа выходов входного коммутатора 1 подключена к входам второго k и третьего 11 регистров. Первая группа выходов второго выходного коммутатора 28 подключена к входам сумматора 30, первая группа выходов которого соединена с входами , четвертого регистра 31 и регистра З результата. Выходы четвертого регистра 31 подключены к первой группе входов коммутатора 32. Вторая группа выходов сумматора соединена с пятым входом 68 блока 35 управления. Первая 69 и вторая 70 входные шины устройства соединены соответственно с третьей и четвертой группами входов входного коммутатора 1. Третья 71, четвертая 72, пятая 73, шестая 7А входные шины устройства соединены соответственно с первым, вторым, третьим и четвертым входами блока 35 управления. Выход регистра 3 результата подключен к шине 75 результата устройства. Первая группа входов .блока 35 управления (.фиг.2) подключена к входу регистра 39 адреса микрокоманд и входам регистра 0 кода операции, выходы которого подключены к входам дешифратора 1. Выходы регистра 39 адреса микрокоманд подключены к первой группе входов постоянной памяти 37 первые семь выходов которой образуют адресную группу ( 0,) , соединенную с входами элементов задержки группы. 38, выходы которой соединены с входами, регистра 39 адреса микрокоманд. Восьмой выход (Q.Q) ПОСТОЯННОЙ памяти 37 подключен к первому выходу 61 блока 35 управления. С девятого . по пятнадцатый (Qg- (1| выходы постоянной памяти 37 объединяются в первую группу 62 выходов блока 35 управления , с шестнадцатого по восемнадцатый (( Cl|g) выходы постоянной памяти 37 объединяются во вторую группу 63 выходов блока 35 управления. Девятнадцатый, двадцатый и двадцать первый (, Q20 -21 выходы постоянной памяти 37 подключены к соответствующим входам регистра 36 адреса констант, выход которого вместе с двадцать вторым (() выходом пос.тоянной памяти 37 образует третью группу (k выходов блока 35 управления. Пятнадцатый выход (Q.5 постоянной памяти 37 вместе с группой выходов с двадцать третьего по двадцать седьмой (Q23 21 образуют четвертую группу б5 выходов блока 35 управления. С двад(ать восьмого по 13Э9 тридцать первый выходы ((igQ- Q) по стоянной памяти 37 образуют пятую группу 66 выходов блока 35 управления. Тридцать второй выход (Q по стоянной памяти 37подключён к второму выходу 67 блока 35 управления. Тридцать третий (Qgj), тридцать четвертый ((1з4) тридцать пятый (Qa«rb выходы постоянной памяти 37 подключе ны к входам соответственно первого k2, второго А6 и третьего 7 элементов задержки. Выход первого элемента 2 задержки подключен к первому входу элемента ИЛИ 43 выход которого соединен с вторым входом постоянной памяти 37. Второй вход блока 35 управления соединен с вторым входом элемента ИЛИ k3. Выход второго элемента Л6 задержки соединен с первым входом первого элемента И , второй Е(ход которого соединен с выходом элемента ИЛИ-НЕ А8, с первым входом первого трехвходового элемента И 5 с входом первого элемента НЕ АЭ, с вторыми входами второго 57 и третьего 58 трехвходовых элементов И. Выход третьего элемента 47 задержки подключен к второму входу первого трехвходового элемента И третий вход которого соединен с выходом второго элемента НЕ 50 и с третьим входом второго трехвходового элемента И 57. Выходы первого элемента И kk и первого трехвходового элемента И 5 подключены к первому управляющему входу регистра 39 адреса микрокоманд. Первый и второй выходы дешифратора k подключены к вторым входам соответственно третьего 52 и второго 51 элементов И, выходы которых подключены к входам элемента ИЛИ-НЕ Третий .выход дешифратора 1 соедине с первым входом четвертого элемента И 55, второй вход которого соединен с аыходом элемента 53 неравнознач ости и с первым входом второго элемента И 51. Выход элемента 5 равнозначности соединен с первым входо третьего элемента И 52. Третий вход блока 35 управления соединен с вторыми входами элемента 5 равнозначности и элемента 53 неравнозначност с вторым входом пятого элемента И § с первым входом третьего трехвходового элемента И 5В и с вхбдом треть го элемента НЕ 60, выход которого оединен с первым входом второго трехвходового элемента И 57. Четвер тый вход блока 35 управления соединен с первыми входами элемента 53 неравнозначности и элемента 5 равнозначности. Пятый вход блока 53 управления соединен с первым входом второго элемента НЕ 50 и с третьим входом третьего трехвходового элемента И 58. ВыхрД первого элемента НЕ 9 соединен с первым входом пятого элемента И 56. Выходы четвертого 55 и пятого 56 элементов И, второго 57 и третьего 58 трехвходовах элементов И подключены к входу триггера 59 знака результата. Устройство работает следующим образом. Функционирование предлагаемого устройства при вычислении ;г1олинома показано на примере вычисления синуса. Вычисление происходит аналогично прототипу. Функция синуса представляется в виде полинома одиннадцатой степени, состоящего из двух частей, вычисляемых одновременно по схеме Горнера 54ПА-А С -.А(С.+А2С2) + -ьА Сз+А2(с -ьА2с). В исходном состоянии в блоке 2 памяти размещены коэффициенты полинома, все регистры и триггер знака результата установлены в нуль. На первую группу входов блока 35 управления поступает код операции, который записывается в регистр 39 адреса микрокоманд и в регистр 40 кода операции. На первую группу входов входного коммутатора 1 поступает аргумент А. На второй вход блока 35 поступает сигнал начала операции, по которому производится чтение первой микрокоманды микропрограммы вычисления синуса по адресу, определенному кодом операции. По первой микрокоманде производится прием аргумента А в первый регистр 3 и во входной регистр второй группы 10 входных регистров и формирование в регистре 36 адреса констант адреса соответствующий констант. По микрооперациям адресной группы ( Q.), задержанным в группе 38 элементов задержки, в регистре адреса микрокоманд формируется адрес следующей микрокоманды. По -микрооперации (Qj , задержанной в перBOM элементе 42 задержки, производит ся чтение следующей микрокоманды. Весь процесс вычисления функции синуса состоит из подготовительного этапа, двух итераций первого вида, одной итерации второго вида, трех итераций третьего вида и заключитель ного этапа. Функционирование устройства в режиме выполнения операции деления про исходит в соответствии с микропрогра мой. Для реализации операций деления используется итерационный алгоритм деления по выражениям )д,, (-«kob i-l ( -1) АО п Ti TV/I гТн Uon где i 1,2,... - номер итерации; ,с - приближенное значение частного, полученного в i-м шаг итерации; -у,- - произведение приближенного значения обратной величины делителя на делитель в i-м шаге итерации. .В исходном состоянии все регистр и триггер знакарезультата установлены в нуль. На первую группу входо блока35 управления поступает код о раций деления, на третью и четвертую группы входов блока 35 управ ления подаются коды знаков дели мого и делителя соответственно, на третью и четвертую группы входов входного коммутатора 1 - модули делимого А и делителя В. На второй вход блока 35 управления поступает сигнал начала операции, по которому производится считывание первой микрокоманды микропрограммы деления по адресу, определяемому кодом операции. По этой микрокоманде делимое А записывается в первый регистр 3, а, делитель В - во входной регистр второй группы 10 входных регистров.. По второй и трет ьей микрокомандам делитель В из регистра второй ,группы 10 входных регистров через второй преобразователь 20 кода частичных произведений в двухрядный кодзаписывается в регистр второй группы 26 выходных регистров, а затем в ре;Гистр третьей группы 14 входных ре;Гистров и после преобразования в преобразователе 29 двухрядного кода в дополнительнь|й двухрядный код в регистры второй группы 10 входных регистров. По четвертой микрокоманде на элементы И первой группы 17 элементов И подаются дели(1ое А и дополнительный код делителя -В)доп, а на элементы И второй группы 18 элементов И подаются дополнительный код делителя {-В)доп и делитель В. В регистры первой группы 23 выходных регистров записывается двухрядный код произведения oto А- ( а в регистры второй группы 2б выходных регистров - двухрядный код произведения () Мик ооперации пятой микрокоманды обеспечивают передачу cip из регистров первой группы 23 выходных регистров в регистры первой группы 7 входных регистров, а регистров второй группы 26 выходных регистров в регистры третьей группы 14 входных регистров,и после преобразования в преобразователе 29 двухрядного кода в дополнительный двухрядный код (- Q)допЗаписывается в регистры второй группы 10 входных регистров. На этом заканчивается подготовительный этап и начинается итерационный процесс вычислений:. В первой иГтерации на элементы И первой группы 17 элементов И подаются сА и ( аГо)доп 3 на элементы И второй группы 18 элементов И подаютС ( )АОП ИЗГо. В регистрах первой группы 23 выходных регистров записывается двухрядный код произведения oi (То)доп регистрах второй группы 2б выходных регистров - двухрядный код произведения gfi (Уо которые затем переписываются соответственно в регистры первой группы 7 входных регистров и в регист-. ры третьей группы 14 входных регистров, а после преобразования двухрядного кода произведения -у в двухрядный дополнительный код (-i/доп ° записывается в регистры второй группы 10 входных регистров. Все последующие итерации выполняются аналогично первой. Число итераций определяется необходимой точностью вычисления частного. Так, для получения частного с точностью (( 2 требуется выполнить не более m logo итераций. Например, для сЛ 2 требуется выполнит не более четырех итераций. В устройстве точность выполнения операции 1799 деления выбрана равной Z, что соответствует трем итерациям. После выполнения трех итераций результат деления регистров первой группы 7 входных регистров поступает чёрез второй преобразователь кода частичных произведений в двухрядный код, в регистры второй группы 26 выходных регистров, затем суммируется и записывается в регистр ЗА результата. Знак частного определяется в блоке 35 управления как сумма по модулю два делимого и делителя. При операции деления на третьем выходе дешифратора 41 появляется сигнал, который разрешает прохождение сигнала с выхода элемента 53 неравхозначности и запись его в триггер 59 знака результата. Особенностью выполнения операции деления в предлагаемом устройстве является параллельное вычисление значений и у и использование этих промежуточных даннь1х в виде двухрядного кода, что значительно уменьшает время выпрлнения операции деления. При выполнении олерации умножения устройство работает в соответствии с микропрограммой. В исходном состоянии все регистры и триггер знака ре зультата содержат нулевую информацию. По первой микрокоманде сомножители заносятся в первый регистр 3 и в регистр второй группы 10 входных регистров. Во второй микрокоманде содержимое этих регистров через второй коммутатор 16 подается на элемен ты И второй группы 18 элементов И. Полученное произведение в виде двух рядного кода записывается в регистр второй группы 2б выходных регистров По третьей микрокоманде двухрядный код суммируется и результат записывается в регистре 3 результата. Знак произведения формируется знало гично тому, как описано при выполнении операции деления. Операции сложения и вычитания вы полняются в соответствии с микропро граммой. Для выполнения операций-ис пользуется алгоритм сложения и вычитания прямых кодов. В исходном состоянии все регистры и триггер знака результата установлены в нуль. По первой микрокоманде первое слагаемое или уменьшаемое поступает в первый регистр 3, вт рое слагаемое или вычитаемое приниается в регистр второй группы 10 ходных регистров. В блоке 35 управения формируется снгнал ,д(.ЗнЛ-Эи8УЗнА-ЗнА)уV (Ъ ( ЗиЛ - Эн8 V ЗнА-ЗиВ), где Чл,. сигнал, который формируется на первом выходе дешифратора 1 при выполнении операции сложения; (J. - сигнал, который формируется на втором выходе дешифратора 1 при выполнении операции вычитания; yu - сигнал на выходе элемента ,ИЛИ-НЕ Ц8. Если 1, то п,о микрооперации (Q345 регистре адреса микрокоманд совместно с микрооперациями адресной группы ( 0.:)/формируется адрес второй МК. Если/14: 0, то по микрооперациям адресной группы (О.- Q) формируется адрес четвертой микрокоманды ., По второй микрокоманде содержимое второй группы 10 входных/регистров через второй преобразователь 20 кода частичных произведений в двухрядный код записывается в регистры второй группы 26 выходных регистров и затем по третьей микрокоманде преобразуется в дополнительный код в преобразователе 29 двухрядного кода в дополнительный двухрядный код и записывается в регистры второй группы 10 входных регистров. По четвертой микрокоманде содержимое первого регистра 3 и регистров второй группы 10 входных регистров через второй коммутатор 16 подается на второй преобразователь 20 кода частичных произведений в двухрядный код и записывается в регистры второй группы 26 выходных регистров. По пятой микрокоманде двухрядный код суммируется и сумма записывается в четвертом регистре 31 и в регистре 3 результата. Если/х. и перенос(11) из старшего разряда сумматора 30 равен нулю ), по микрооперации (Цзз)в регистре 39 адреса микрокоманд формируется адрес шестой микрокоманды, по которой через коммутатор 32 и преобразователь 33 кода в дополнительный код записывается прямой код результата на регистр 3 результата с регистра 31. Знак результата определяется из условий ГЗ и А, если/ij, 3 и Р « (з и А, если /й-рд П 1. Таким образом, предлагаемое устройство, кроме вычисления полиномов, позволяет выполнять основные арифметические операции: сложение, вычитание, умножение и деление. При этом аппаратурные затраты увеличиваются всего на 5-7. Формула изобретения 1. Вычислительное устройство чсодержащее блок -памяти, входной коммут тор, два коммутатора, два выходных коммутатора, три регистра, три групп входных и две группы выходных регист ров, две группы элементов И, два пре образователя кода частичных произведений в двухрядный код, сумматор, регистр результата, причем выходы бл ка памяти соединены с одноименными входами первой группы входов входного коммутатора, первая группа выходов которого подключена к одноимен ным входам первого регистра и входам входных регистров второй труппы, вто рая группа выходов входного коммутатора соединена с одноименными входами BTOJDoro и третьего регистров, выходы первого выходного коммутатора подключены к входам входных регистров первой группы, вы «;оды первого, ;второго регистров и входных регистров первой группы подключены к соотч етствующим входам первой, второй третьей групп входов первого комj yTaTopa, выходы первой, второй и третьей групп выходов которого сое динены соответственно с первыми, вто рыми и третьими входами соответствующих элементов И первой группы, вы ходы входных регистров второй группы выходы третьего регистра и выходы входных регистров третьей группы сое динены с одноименными входами соответственно первой, второй и третьей групп входов второго коммутатора, вы ходвьпервой, второй и третьей групп выходов которого соединены соответственно с первыми, вторыми и третьими входами одноименных элементов И второй группы, выходы четвертой груп пы выходов первого и второго коммута торов соединены с четвертыми входами соответственно элементов И второй группы и элементов И первой группы, выходы пятой группы выходов.первого, второго коммутаторов и выходы элементов И второй группы подключены к соответствующим входам второго преобразователя кодов частичных произведений в двухрядный код, выходы которого подключены к одноименным входам выходных регистров второй группы, выходы элементов И первой группы соединены с входами первого преобразователя кодов частичных произведений в двухрядный код, выходы которого соединены с одноименными входами выходных регистров первой группы, выходы выходных регистров первой и второй групп соединены с одноименнымивходами первой группы входов первого и второго .выходных коммутаторов соответственно, выходы первой группы выходов второго выходного коммутатора подключены к одноименным входам сумматора, выходы второй груп пы выходов этого коммутатора подключены к одноименным входак входных регистров второй группы, выходы третьей группы - к одноименным входам входных регистров третьей группы, выходы первой группы выходов сумматора соединены с одноименными входами регистра результата, выходы которого подключены к шине результата устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства, путем выполнения им операций сложения, вычитания, умножения и деления, оно содержит блок управления, преобразователь двухрядного кода в дополнительный двухрядный код, преобразователь двоичного кода в дополнительный код, четвертый регистр, тре-г тий Коммутатор, причем выходы четвертой группы выходов второго выходного коммутатора соединены с одноимец ными входами преобразователя двухряд- ного кода в дополнительный двухрядный код, выходы которого соединены с одноименными входами входных регистров второй группы, входы первой группы входов третьего коммутатора подключены к соответствующим выходам четвертого регистра, входы которого подключены к одноименньйМ выходам первой группы выходов сумматора, выходы третьего коммутатора подключены к одноименным входам преобразователя двоичного кода в дополнительный код. 2199 выходы которого подключены к соответствующим входам регистра результата, первая входная шина устройства соединена с входами второй группы входов входного коммутатора, вторая.входная шина устройства - с входами четвертой группы входов входного коммутатора, третья входная шина устройства, соединена с первой груп пой входов блока управ;ления, четвертая входная шина устройства - с первым .входом блока управления, Литая входная шина устройства - с ВТОРЫМ входом блока управления, шеста входная шина устройства - с третьим входом блока управления, первый выход сумматора подключен к четвертому входу блока управления, первый выход бло ка управления подключен к второму входу первого выходного коммутатора, второй выход блока управления подключен к втЬромувходу третьего - ком мутатора, выходы первой группы выходов блока управления соответствен но соединены с входами первой группы входов первого коммутатора, выходы второй группы выходов блока управления соединены соответственно с входами первой группы входов входного коммутатора выходы третьей группы выходов блока управления подключены к одноименным входам блока памяти, выходы четвертой группы выходов блока управления соединены с одноименными входами первой группы входов второго коммутатора, выходы пятой группы выходов блока управления соответственно соединены с входами первой группы входов второго выходного коммутатора. .2. Устройство по п.1, о т ли чающееся, тем, что блок управления содержит регистр адреса констант, постоянную память, группу элементов задержки, регистр адреса микрокоманд, регистр кода операции; дешифратор, первый, второй и третий 1 элементы задержки, элемент ИЛИ-НЕ эле элемент равнозначности, элемент неравнозначности, пять элементов И, , три элемента НЕ,три трехвходовыхэлеме та И,элемент ИЛИ,триггер знака резуль тата,причем выходы регистра адреса ми

рокоманд соединены с одноименными входами первой группы входов постоянной памяти, первые семь выходов постоянной памяти образуют адресную группу и соответственно соединены с входами группы элементов задержки.

равляющему входу регистра адреса микрокоманд, выход третьего элемента 55 задержки соединен с вторые входом первого трехвходового элемента И, выход которого подключен к второму уп- . равляющему входу регистра адреса миквыходы которой соединены с одноименными входами регистра адреса микрокоманд , восьмой выход постоянной памяти является-первым выходом блока управления, выходы постоянной памяти с девятого по пятнадцатый образуют первую группу выходов, с шестнадцатого по восемнадцатый - вторую группу выходов блока управления, с девятнадцатого по двадцать .первый вы- . :Ходы постоянной памяти соединены с входами регистра адреса констант, выходы которого и двадцать второй выход постоянной памяти образуют третью группу выходов блока управления, пятнадцатый .выход постоянной памяти и ее выходы с двадцать третьего по двадцать седьмой образуют четвертую группу выходрб блок управления, вы-; ходы:с двадцать восьмого по тридцать первый постоянной памяти - пятую группу выходов блока управления, тридцать второй выход постоянной памяти является вторым выходом блока управления, тридцать третий, тридцать четвертый и тридцать пя1ый выходы постоянной памяти соединены соответственно с входами третьего, второго и первого,элементов задержки, входы регистра кода операции и регистра адреса микрокоманд образуют первую группу входо.в блока управления, первый вход блока управления соединен с вторым входом элемента ИЛИ, второй вход блока управления с вторыми входами элемента равнозначности и элемента неравнозначности, с выходом третьего элемента НЕ, с вторым входом пятого элемента И и первым входом третьего трехвходового элемента И, третий вход блока управления - с первыми входами элемента равнозначности и элемента неравнозначности , четвертый - с входом второго элемента НЕ и с третьим входом третьего трехвходового элемента И, выход первого элемента задержки соединен с первым входом элемента ИЛИ, выход которого подключен к второму входу постоянной памя.ти, выход второго элемента задержки соединен с первым входом первого элемента И, аыход которого подключен к первому упрокоманд, выход элемента неравнозначности соединен с первым входом второго элемента И и с вторым входом четвертого элемента И, выход элемента равнозначности соединен с первым входом третьего элемента И, выходы второго и третьего элементов И соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ, выход которого подключен к второму входу первого элемента И,к первому входу первого трехвходового элемента И, к входу первого элемента НЕ, к второму входу трехвходового элемента И и к второму входу третьего трехвходового элемента И, выход второго элемента НЕ соединен с третьими входами первого и второго трехвходовых элементов .И, выходы регистра кода операций соединены с соответствующими входами дешифратора, первый выход дешифратора соединен с вторым входом третьего

элемента И. второй выход дешифраторас вторым входом второго элемента И, третий выход дешифратора - с первым входом четвертого элемента И, выходы четвертого, пятого элементов И, второго и третьего трехвходовых элементо И соединены с входом триггера знака результата, выход первого элемента НЕ соединен с первым входом пятого элемента И, выход третьего элемента НЕ соединен с первым входом второго трехвходового элемента И.

Источники информации, принятые во внимание при экспертизе

кл. G Об F 15/31, 1980 (прототип).

Авторы

Даты

1983-01-30—Публикация

1981-04-14—Подача