Изобретение относится к цифровой вычислительной технике, в частности к полупроводниковым запоминающим устройствам,

Целью изобретения является расширение области применения запоминающего устройства (ЗУ)за счет возможности работы в режиме с повьппен- ным быстродействием.

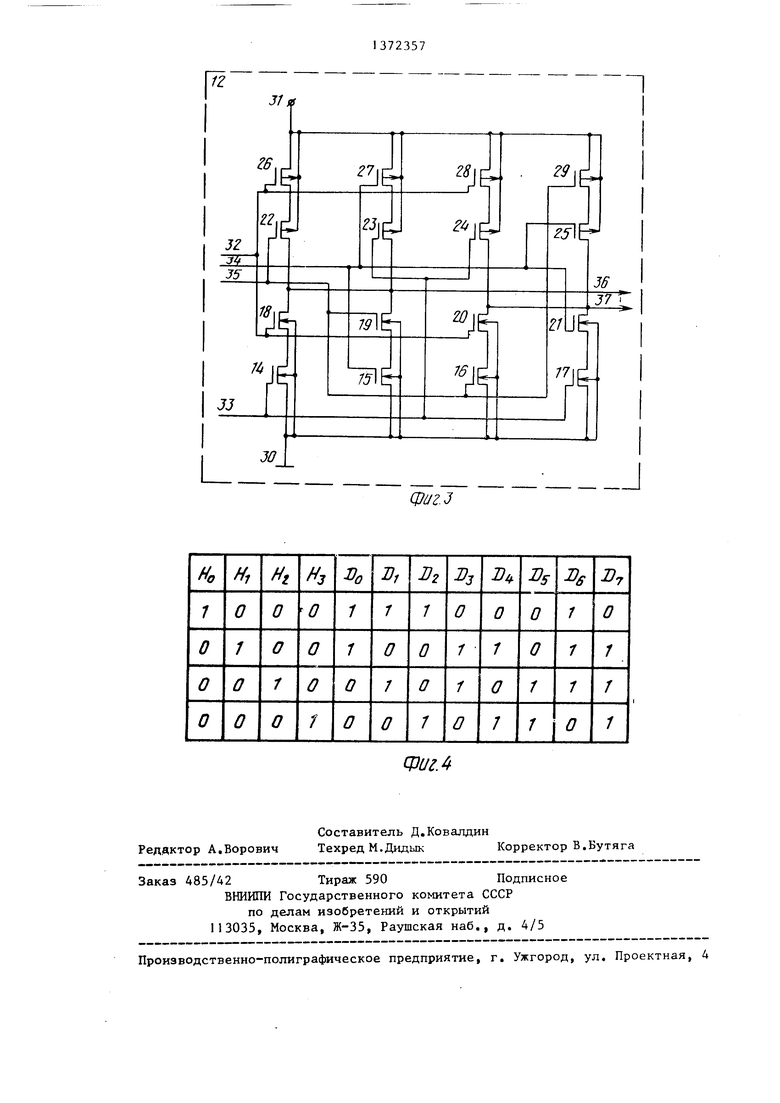

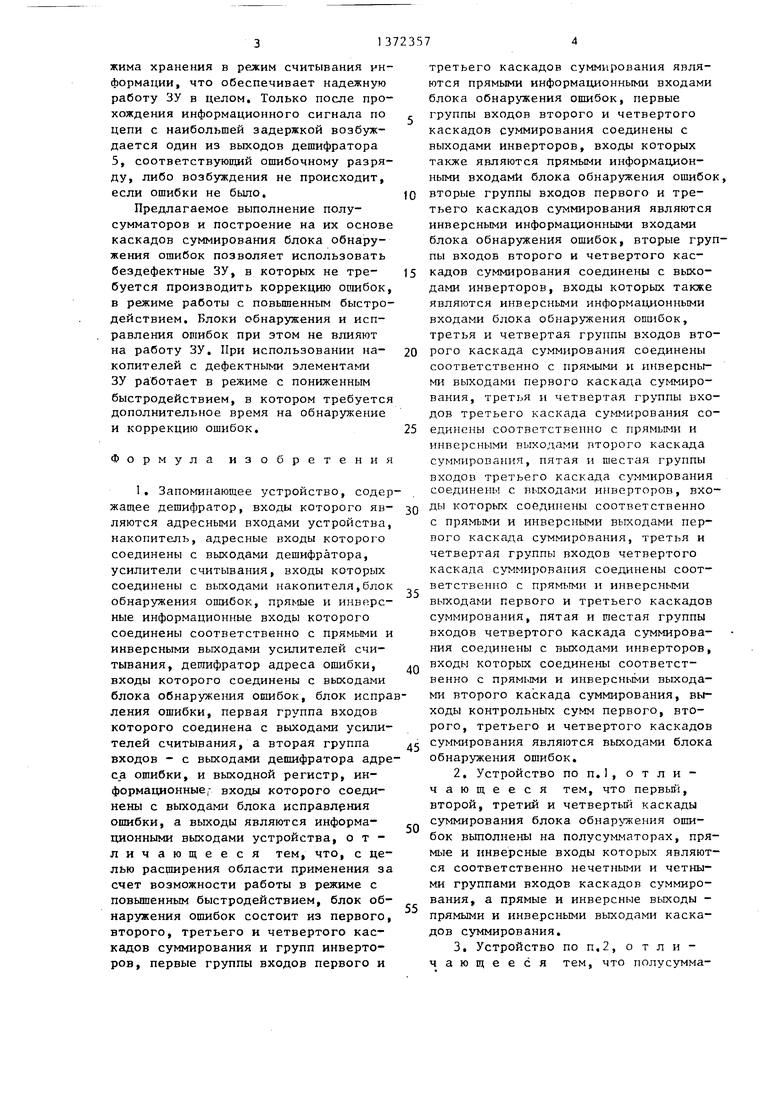

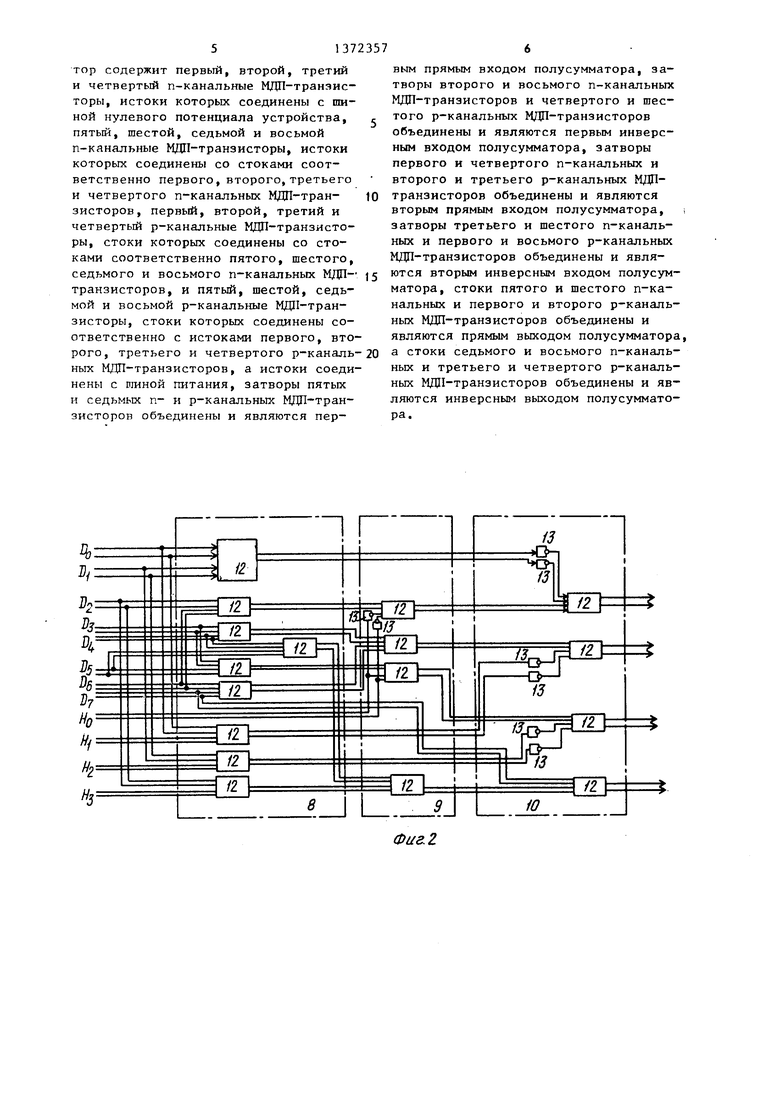

На фиг.1 представлена структурная схема ЗУ; на фиг.2 - структурная схема блока обнаружения ошибок и каскадов суммирования; на фиг.З - прин- 1щпиальная электрическая схема полу- сумматора; на фиг.4 - проверочная матрица алгоритма Хэмминга.

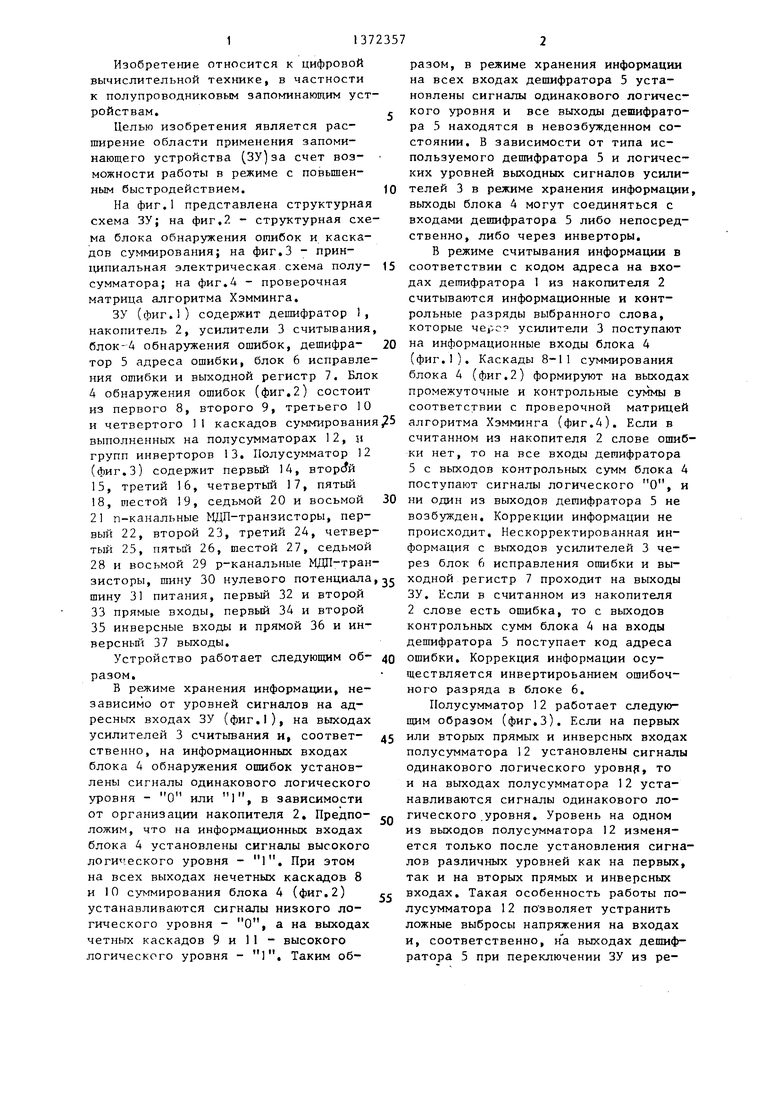

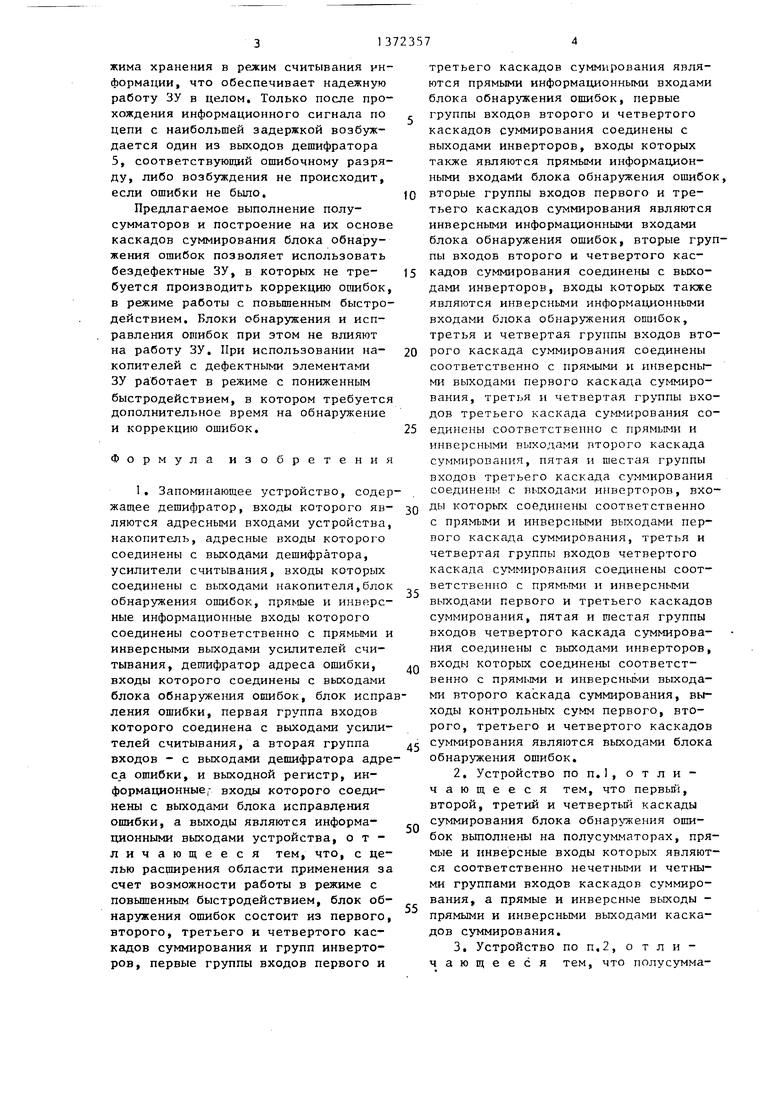

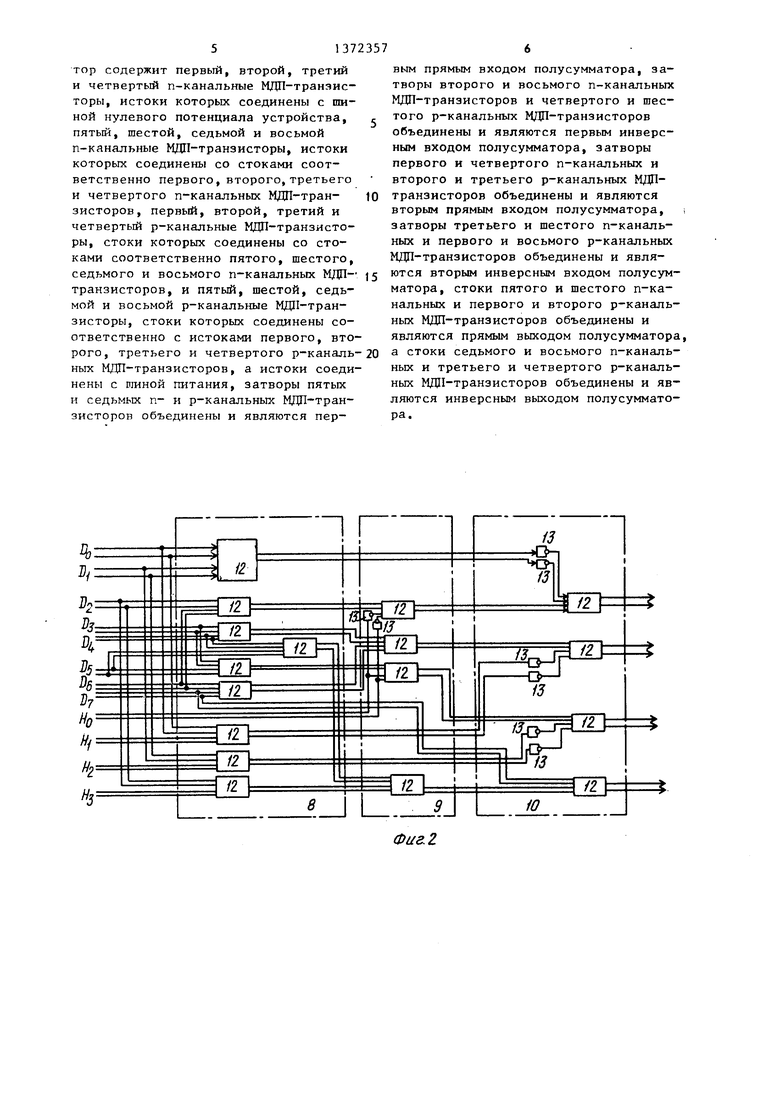

ЗУ (фиг.1) содержит дешифратор 1, накопитель 2, усилители 3 считывания блок-А обнаружения ошибок, дешифра- тор 5 адреса ошибки, блок 6 исправления ошибки и выходной регистр 7. Бло 4 обнаружения ошибок (фиг.2) состоит из первого 8, второго 9, третьего 10 и четвертого 1 1 каскадов суммировани выполненных на полусумматорах 12, и групп инверторов 13. Полусумматор 12 (фиг.З) содержит первый 1А, второй 15, третий 16, четвертый 17, пятый 18, шестой 19, седьмой 20 и восьмой 21 п-канальные ЬЗДП-транзисторы, первый 22, второй 23, третий 24, четвертый 25, пятьш 26, тестой 27, седьмой 28 и восьмой 29 р-канальные МДП-тран зисторы, шину 30 нулевого потенциала шину 31 питания, первый 32 и второй 33 прямые входы, первый 34 и второй 35 инверсные входы и прямой 36 и ин- версньй 37 выходы.

Устройство работает следующим об-

разом.

В режиме хранения информации, независимо от уровней сигналов на адресных входах ЗУ (фиг.1), на выходах усилителей 3 считывания и, соответ- ственно, на информационных входах блока 4 обнаружения ошибок установлены сигналы одинакового логического уровня - О или 1, в зависимости от организации накопителя 2. Предпо- ложим, что на информационных входах блока 4 установлены сигнашы высокого логического уровня - 1. При этом на всех выходах нечетных каскадов 8 и 10 суммирования блока 4 (фиг.2) устанавливаются сигналы низкого логического уровня - О, а на выходах четных каскадов 9 и 11 - высокого логического уровня - 1. Таким образом, в режиме хранения информации на всех входах дешифратора 5 установлены сигналы одинакового логического уровня и все выходы дешифратора 5 находятся в невозбужденном состоянии. В зависимости от типа используемого дешифратора 5 и логических уровней вькодиых сигналов усилителей 3 в режиме хранения информации выходы блока 4 могут соединяться с входами дешифратора 5 либо непосредственно, либо через инверторы.

В режиме считывания информации в соответствии с кодом адреса на входах дешифратора 1 из накопителя 2 считываются информационные и контрольные разряды выбранного слова, которые черс усилители 3 поступают на информационные входы блока 4 (фиг.1). Каскады 8-11 суммирования блока 4 (фиг.2) формируют на выходах промежуточные и контрольные суммы в соответствии с проверочной матрицей алгоритма Хэмминга (фиг.4). Если в считанном из накопителя 2 слове ошибки нет, то на все входы дешифратора 5 с выходов контрольных сумм блока 4 поступают сигналы логического О, и ни один из выходов дешифратора 5 не возбужден. Коррек1Д1и информации не происходит. Нескорректированная информация с выходов усилителей 3 через блок 6 исправления ошибки и выходной регистр 7 проходит на выходы ЗУ. Если в считанном из накопителя 2 слове есть ошибка, то с выходов контрольных сумм блока 4 на входы дешифратора 5 поступает код адреса ошибки. Коррекция информации осуществляется инвертированием ошибочного разряда в блоке 6.

Полусумматор 12 работает следующим образом (фиг.З). Если на первых или вторых прямых и инверсных входах полусумматора 12 установлены сигналы одинакового логического уровнр, то и на выходах полусумматора I2 устанавливаются сигналы одинакового логического .уровня. Уровень на одном из выходов полусумматора 12 изменяется только после установления сигналов различных уровней как на первых, так и на вторых прямых и инверсных входах. Такая особенность работы полусумматора 12 позволяет устранить ложные выбросы напряжения на входах и, соответственно, на выходах дешифратора 5 при переключении ЗУ из режима хранения в режим считывания информации, что обеспечивает надежную работу ЗУ в целом. Только после прохождения информационного сигнала по цепи с наибольшей задержкой возбуждается один из выходов дешифратора 5, соответствующий ошибочному разряду, либо возбуждения не происходит, если ошибки не было.

Предлагаемое выполнение полусумматоров и построение на их основе каскадов суммирования блока обнаружения ошибок позволяет использовать бездефектные ЗУ, в которых не тре- буется производить коррекцию ошибок, в режиме работы с повьш1енным быстродействием. Блоки обнаружения и исправления ошибок при этом не влияют на работу ЗУ, При использовании на- копителей с дефектными элементами ЗУ работает в режиме с пониженным

быстродействием, в котором требуется

дополнительное время на обнаружение

и коррекцию ошибок,

Формула изобретения

1, Запоминающее устройство, содержащее дешифратор, входы которого яв- ляются адресными входами устройства, накопитель, адресные входы которого соединены с выходами дешифратора, усилители считывания, входы которых соединены с выходами накопителя,блок обнаружения ошибок, прямые и инверсные информационные входы которого соединены соответственно с прямыми и инверсными выходами усилителей считывания, дешифратор адреса ошибки, входы которого соединены с выходами блока обнаруже1шя ошибок, блок испраления ошибки, первая группа входов которого соединена с выходами усилителей считывания, а вторая группа входов - с выходами дешифратора адреса ошибки, и выходной регистр, информационные,- входы которого соединены с выходами блока исправления ошибки, а выходы являются информа- ционными выходами устройства, отличающееся тем, что, с целью расщирения области применения за счет возможности работы в режиме с повышенным быстродействием, блок обнаружения ошибок состоит из первого, второго, третьего и четвертого каскадов суммирования и групп инверторов, первые группы входов первого и

,

5 0

5

о Q

5

5

третьего каскадов суммирования являются прямыми информационными входами блока обнаружения ошибок, первые группы входов второго и четвертого каскадов суммирования соединены с выходами инверторов, входы которых также являются прямыми информационными входами блока обнаружения ошибок, вторые группы входов первого и третьего каскадов суммирования являются инверсными информационными входами блока обнаружения ошибок, вторые группы входов второго и четвертого каскадов суммирования соединены с выходами инверторов, входы которых также являются инверсными информационными входами блока обнаружения ошибок, третья и четвертая группы входов второго каскада суммирования соединены соответственно с прямыми и инверсными выходами первого каскада суммирования, третья и четвертая группы входов третьего каскада суммирования соединены соответственно с прямыми и инверсными выходами пторого каскада суммировання, пятая н шестая группы входов третьего каскада суммирования соединены с выходами инверторов, входы которых соединены соответственно с прямыми и инверсными выходами первого каскада суммирования, третья и четвертая группы входов четвертого каскада суммирования соединены соответственно с прямыми и инверсными выxoдa ш первого и третьего каскадов суммирования, пятая и шестая группы входов четвертого каскада суммирования соединены с выходами инверторов, входы которых соединены соответственно с прямыми и инверсными выходами второго каскада суммирования, выходы контрольных сумм первого, второго, третьего и четвертого каскадов суммирования являются выходами блока обнаружения ошибок,

2,Устройство по п,1, отличающееся тем, что первый, второй, третий и четвертый каскады суммирования блока обнаружения ошибок вьтолнены на полусумматорах, прямые и инверсные входы которых являются соответственно нечетными и четными группами входов каскадов суммирования, а прямые и инверсные выходы - прямыми и инверсными выходами каскадов суммирования,

3,Устройство по п,2, о т л и - чающееся тем, что полусумматор содержит первый, второй, третий и четвертый п-канальные МДП-транзис- торы, истоки которых соединены с шиной нулевого потенциала устройства, пятый, шестой, седьмой и восьмой п-канальные МДП-транзисторы, истоки которых соединены со стоками соответственно первого, второго, третьего и четвертого п-канальных МДП-тран- зисторов, первый, второй, третий и четвертый р-канальные МДП-транзисторы, стоки которых соединены со стоками соответственно пятого, шестого, седьмого и восьмого п-канальных МДП- транзисторов, и пятый, шестой, седьмой и восьмой р-канальные МДП-транзисторы, стоки которых соединены соответственно с истоками первого, второго, третьего и четвертого р-каналь ных МДП-транзисторов, а истоки соединены с П1ИНОЙ питания, затворы пятых и седьмых п- и р-канальньгк МДП-тран- зисторон объединены и являются первым прямым входом полусумматора, затворы второго и восьмого п-канальных МДП-транзисторов и четвертого и шес- того р-канальных МДП-транзисторов объединены и являются первым инверсным входом полусумматора, затворы первого и четвертого п-канальных и второго и третьего р-канапьных МДП- 10 транзисторов объединены и являются

вторым прямым входом полусумматора, i затворы третьего и шестого п-канальных и первого и восьмого р-канапьных МДП-транзисторов объединены и явля- и ются вторым инверсным входом полусумматора, стоки пятого и шестого п-канальных и первого и второго р-канальных МДП-транзисторов объединены и являются прямым выходом полусумматора, 20 3 стоки седьмого и восьмого п-канальных и третьего и четвертого р-канальных МДП-транзисторов объединены и являются инверсным выходом полусумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Устройство для синхронизации памяти | 1983 |

|

SU1169017A1 |

| Устройство для передачи и приема дескретных сообщений | 1990 |

|

SU1786669A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1522292A1 |

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ КАНАЛЬНОГО КОДА | 2012 |

|

RU2521299C1 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2579954C2 |

| ДЕТЕКТОР ИЗЛУЧЕНИЯ | 1992 |

|

RU2032189C1 |

Изобретение относится к цифровой вычислительной технике, в частности к полупроводниковым ЗУ. Цель изобретения;, - расширение области применения ЗУ за счет возможности работы в режиме с пойыгаенным быстродействием. Поставленная цель достигается тем, что в ЗУ, содержаием дешифратор I, накопитель 2, усилители 3 считывания, блок 4 обнаружения ошибок, дешифратор 5 адреса ошибки. блок 6 исправления ошибки и выходиой регистр 7, блок обнаружения ошибок состоит из четырех каскадов 8-11 суммирования, выполненных иа полусумматорах, и групп инверторов 13. Полусумматор содержит восемь г.-канальных и восемь р-каналы1ьгх ОДП-транзисто- ров и имеет два прямых и два инверс- 11,1х входа и прямой и инверсный выходы. Конструктивное выполнение полусумматоров и построение на их основе каскадов 8-II суммирования блока 4 обнаружения ошибок позволяет использовать бездефектные ЗУ, не требующие коррекции оршбок, в режиме с повышенным быстродействием. Блоки обнаружения 4 и исправления 6 ошибок при этом не влияют на работу ЗУ. При использовании накопителей 2 с дефектными элементами ЗУ работает в режиме с пониженным быстродействием, в котором производятся проверка и коррекция считываемой информации по алгоритму Хэмминга. 2 з.п. ф-лы, 4 ил. i (Л

Hi

3

Фиа2

фиг.з

Ф/у/.

| ЭЛЕКТРИЧЕСКИЙ РАЗЪЕДИНИТЕЛЬ | 2011 |

|

RU2528613C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Орангзеб Хан, Кыстродейстпующие ЗУПВ со встроенныьш схемами исправления ошибок | |||

| - Электроника, 1983, № 18, с | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

Авторы

Даты

1988-02-07—Публикация

1986-04-01—Подача