1

Изобретение относится к запоминащим устройствам и может быть использовано в качестве буферного запоминющего устройства (БЗУ) при построен устройства обмена о

Цель изобретения - расширение области применения устройства за сче выдачи информации через определенны интервалы времени.

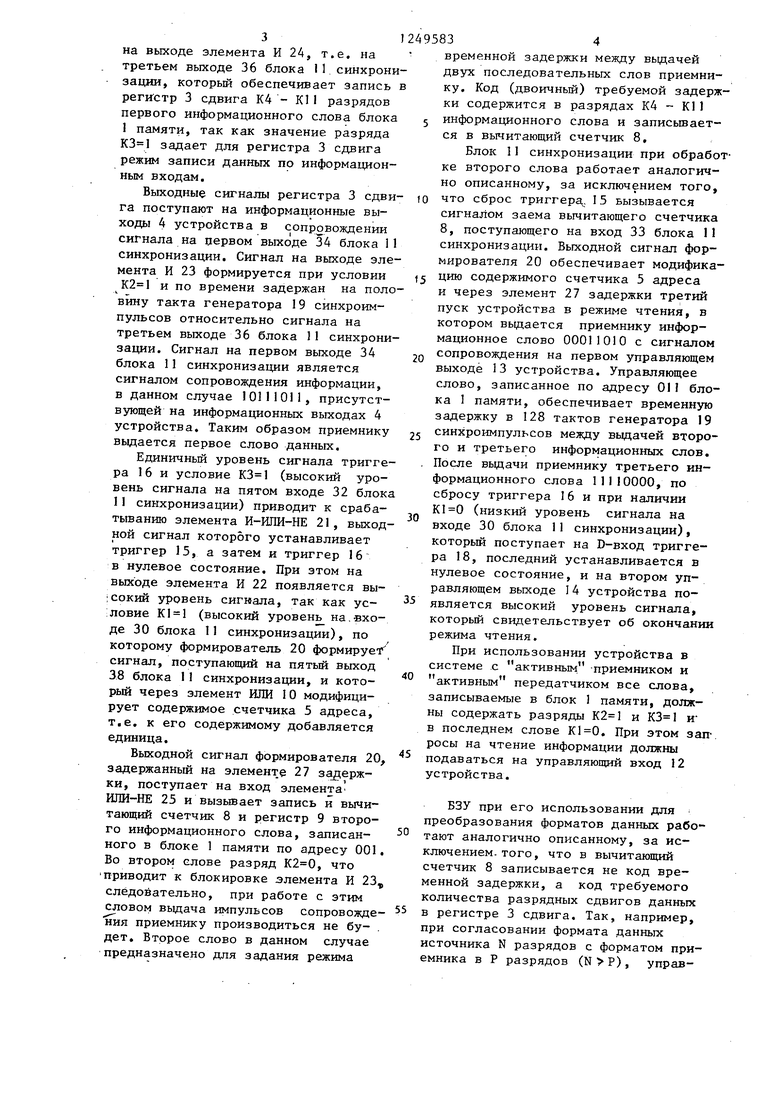

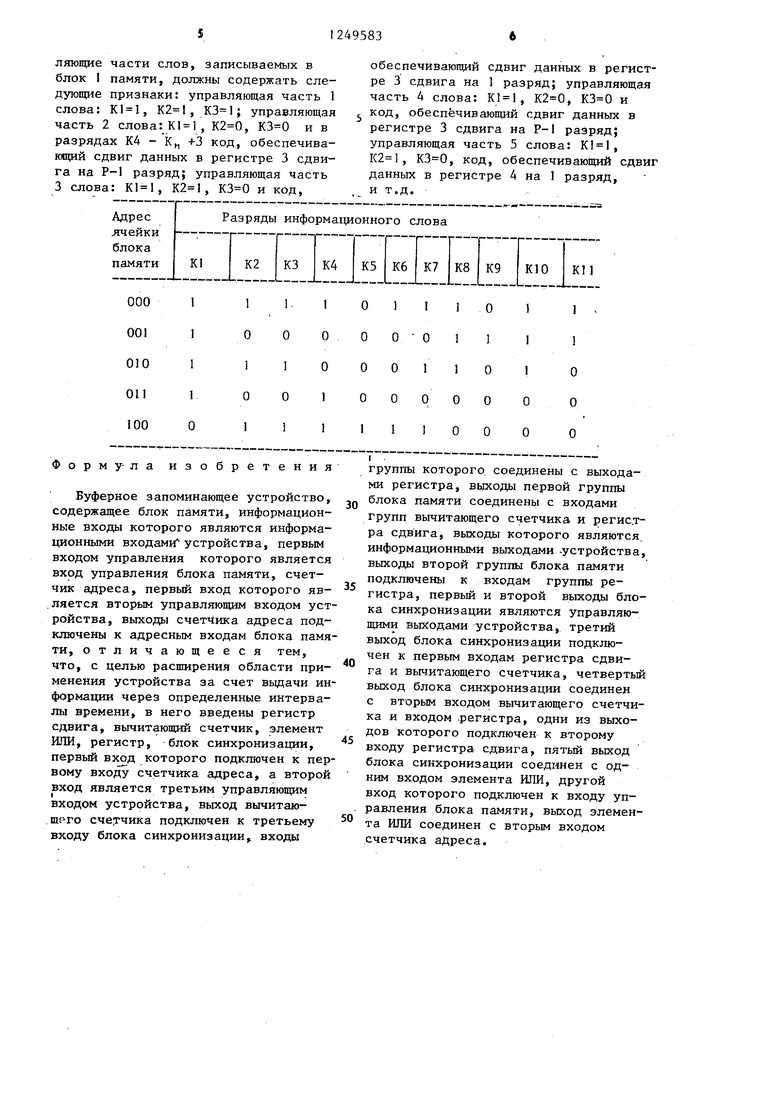

На фиг. 1 приведена структурная схема устройства; на фиг.2 - структурная схема блока синхронизации.

Устройство содержит блок 1 памяти с информационными входами 2, регистр 3 сдвига с информационными выходами 4, счетчик 5 адреса, первьй 6 и второй 7 входы управления, вычитающий счетчик 8, регистр 9, элемен ИЛИ 10 синхронизации , третий вход 12 управления, первый 13 и второй 1 управляющие выходы

Блок 11 синхронизации содержит первый 15, второй 16, третий 17 и четвертьш 18 триггеры, генератор 19 синхроимпульсов, формирователь 20, элемент И-ИПИ-НЕ 21, первый 22, второй 23 и третий 24 элементы И, элемент ИЛИ-НЕ 25, элемент НЕ 26, элемент 27 задержки, первый 28, второй 29, третий 30, четвертый 31, пятый 32 и шестой 33 входы, первый 34, второй 35, третий 36, четвертьш 37 и пятый 38 выходы.

Устройство работает следующим образомо

Перед началом работы сигналом на входе 7 устанавливаются в нулевые состояния счетчик 5 адреса и триггеры 15-17 блока 11 синхронизации а-триггер 18 блока 11 синхронизации устанавливается в единичное состояние.

в режиме записи на информационные входы 2 устройства последовательно поступают информационные слова в сопровождении сигнала на первом уйравляющем входе 6 устройства, который осуществляет запись информационного слова в блок 1 памяти по адресу, сформированному на счетчике 5 адреса. Задним фронтом сигнала на первом входе 6 управления устройства производится модификация содержимого счетчика 5 адреса, т.е. к его содержимому добавляется единица. Каждое информационное слово, записываемое в блок памяти., содержит И 3 разряда.

5

0

583

2

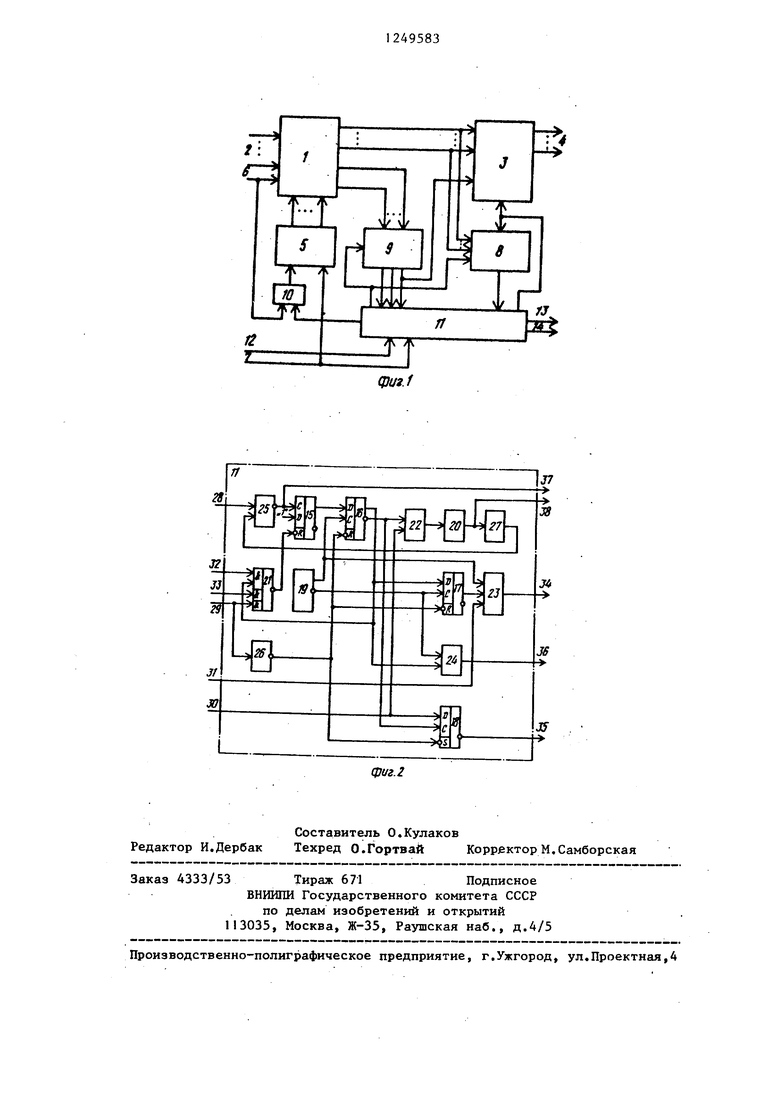

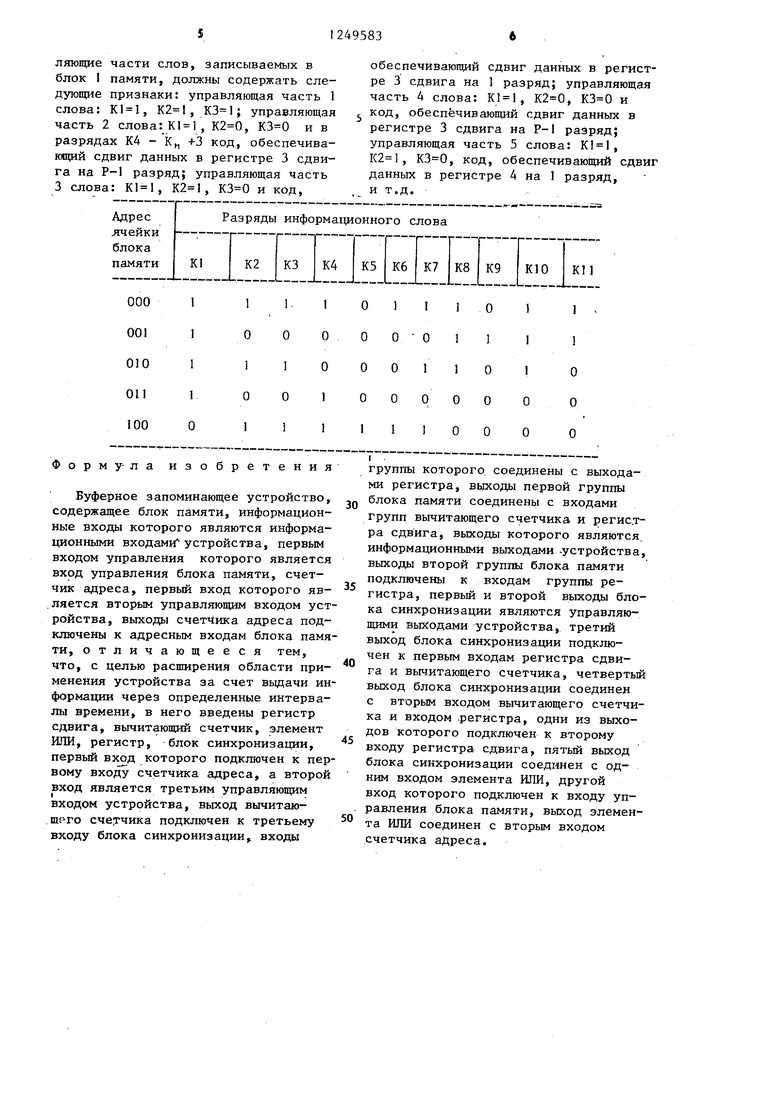

Первые три разряда К, К2 и КЗ слова (управляющая часть его) содержит код операции, выполняемой БЗУ, Разряд К1 содержит признак конца чтения, К1-0 в последнем слове блока данных, записьшаемого в блок 1 памятИо Разряд определяет блокировку передачи приемнику информации считанных из блока 1 памяти данныхо Разряд КЗ является идентификатором содержимого разрядов К4 - Кц + 3 информационного слова. Если , то при выполнении операции чтения в разрядах К4 - К/, + 3 содержится слово, подлежащее выдаче приемнику. Если , то при выполнении операции в разрядах К4 - Кд, + 3 содержится код количества разрядных сдвигов, выполняемых в регистре 3 сдвига при согласовании форматов данных или код временной задержки передачи следующего информационного слова приемнику.

По окончании записи в блок 1 па- 5 мяти сигналом на входе 7 устройства счетчик 5 адреса сбрасьшается в нулевое состояние«

Режим чтения начинается с приходом сигнала на входе 12 управления устройства. Работу БЗУ в режиме чтения целесообразно рассматривать применительно к конкретной области его использования.

Рассмотрим работу устройства в режиме чтения при его использовании

0

5

в цепи активный источник - пассивный приемник информации. Пусть, например, в режиме записи в блок 1

памяти по последовательно возрастающим адресам, начиная с нулевого был записан информационный массив, представленный в таблице.

Б режиме чтения сигнал на входе 12 управления через первый вход 28 и элемент ИПИ-НЕ 25 блока 11 синхронизации осуществляет запись первого информационного слова, записанного в блоке 1 памяти по адресу 000, в регистр 9(разряды К1 - КЗ) и в вычитающий счетчик 8 (разряды К4 - К1 1) Задним фронтом сигнала на выходе элемента ИЛИ-НЕ 25 устанавливается в единичное состояние триггер 15, что обеспечивает установку в единичное состояние триггера 16 с приходом положительного перепада сигнала от генератора 19 синхроимпульсов. Установка в единичное состояние триггера 16 вызьшает появление сигнала

на выходе элемента И 24, т.е. на третьем выходе 36 блока 11 синхронизации, который обеспечивает запись регистр 3 сдвига К4 - К1I разрядов первого информационного слова блока

Iпамяти, так как значение разряда задает для регистра 3 сдвига режим записи данных по информационным входам.

Выходные сигналы регистра 3 сдви га поступают на информационные выходы 4 устройства в сопровождении сигнала на первом выходе 34 блока I 1 синхронизации. Сигнал на выходе элемента И 23 формируется при условии и по времени задержан на половину такта генератора 19 синхроимпульсов относительно сигнала на третьем выходе 36 блока 11 синхронизации. Сигнал на первом выходе 34 блока 11 синхронизации является сигналом сопровождения информации, в данном случае 10111011, присутст- на информационных выходах 4 устройства. Таким образом приемнику выдается первое слово данных.

Единичньш уровень сигнала триггера 1 6 и условие (высокий уровень сигнала на пятом входе 32 блока

I1синхронизации) приводит к срабатыванию элемента И-ИЛИ-НЕ 21, выходной сигнал которого устанавливает триггер 15, а затем и триггер 16

в нулевое состояние. При этом на выходе элемента И 22 появляется вы- ;сокий зфовень сигнала, так как ус- ловие (высокий уровень на.входе 30 блока 11 синхронизации), по которому формирователь 20 формирует сигнал, поступающий на пятый выход 38 блока 11 синхронизации, и который через элемент ИЛИ IО модифицирует содержимое счетчика 5 адреса, т.е. к его содержимому добавляется единица.

Выходной сигнал формирователя 20, задержанный на элементе 27 задержки, поступает на вход элемента ИЛИ-НЕ 25 и вызьтает запись и вычитающий счетчик 8 и регистр 9 второго информационного слова, записан- ного в блоке 1 памяти по адресу 001. Во втором слове разряд , что приводит к блокировке элемента И 23, следовательно, при работе с этим словом выдача импульсов сопровожде ния приемнику производиться не будет. Второе слово в данном случае предназначено для задания режима

j

(о f2025

30

40

55

временной задержки между выдачей двух последовательных слов приемнику. Код (двоичный) требуемой задержки содержится в разрядах К4 - К11 информационного слова и записьшает- ся в вычитающий счетчик 8,

Блок I1 синхронизации при обработке второго слова работает аналогично описанному, за исключением того, что сброс триггера;, 15 вызывается сигналом заема вычитающего счетчика 8, поступающе:го на вход 33 блока 1 1 синхронизации. Выходной сигнал формирователя 20 обеспечивает модификацию содержимого счетчика 5 адреса и через элемент 27 задержки третий пуск устройства в режиме чтения, в котором выдается приемнику информационное слово 00011010 с сигналом сопровождения на первом управляющем выходе 13 устройства. Управляющее слово, записанное по адресу 011 блока 1 памяти, обеспечивает временную задержку в 128 тактов генератора 19 синхроимпульсов между выдачей второго и третьего информационных слов. После вьщачи приемнику третьего информационного слова 11110000, по сбросу триггера I6 и при наличии (низкий уровень сигнала на входе 30 блока 11 синхронизации), который поступает на D-вход триггера 18, последний устанавливается в нулевое состояние, и на втором управляющем выходе 14 устройства появляется высокий уровень сигнала, который свидетельствует об окончании режима чтения.

При использовании устройства в системе с активным -приемником и активным передатчиком все слова, записываемые в блок 1 памяти, должны содержать разряды и и в последнем слове К . При этом зап-. росы на чтение информации должны подаваться на управляющий вход 12 устройства.

БЗУ при его использовании для преобразования форматов данных работают аналогично описанному, за исключением- того, что в вычитающий счетчик 8 записывается не код временной задержки, а код требуемого количества разрядных сдвигов данных в регистре 3 сдвига. Так, например, при согласовании формата данных источника N разрядов с форматом приемника в Р разрядов (N Р), управляющие части слов, записываемых в блок 1 памяти, должны содержать следующие признаки: управляющая часть 1 слова: , , управляющая часть 2 слова: К1 Г, , и в разрядах К4 - К„ +3 код, обеспечивающий сдвиг данных в регистре 3 сдвига на Р-1 разряд; управляющая часть 3 слова: , , и код,

Формула изобретения

Буферное запоминающее устройство, содержащее блок памяти, информационные входы которого являются информационными входами устройства, первым входом управления которого является вход управления блока памяти, счетчик адреса, первый вход которого яв.ляется вторым управляющим входом устройства, выходы счетчика адреса подключены к адресным входам блока памяти, отличающееся тем, что, с цепью расширенная области применения устройства за счет вьодачи информации через определенные интервалы времени, в Него введены регистр сдвига, вычитающий счетчик, элемент ИЛИ, регистр, блок синхронизации, первый вход которого подключен к первому входу счетчика адреса, а второй вход является третьим управляющим входом устройства, выход вычитаю,щрго сче;гчика подключен к третьему входу блока синхронизации, входы

обеспечивающий сдвиг данных в регистре 3 сдвига на 1 разряд; управляющая часть 4 слова: , , и код, обеспечиваюпщй сдвиг данных в регистре 3 сдвига на Р-1 разряд; управляющая часть 5 слова: , , , код, обеспечивающий сдвиг данных в регистре 4 на 1 разряд, и т.д.

группы которого, соединены с выходами регистра, выходы первой группы блока памяти соединены с входами групп вычитающего счетчика и регис.т- ра сдвига, выходы которого являются, информационными выходами -устройства, выходы второй группы блока памяти подключены к входам группы регистра, первый и второй выходы блока синхронизации являются управляющими выхюдами устройства, третий вьгход блока синхронизации подключен к первым входам регистра сдвига и вычитающего счетчика, четвертьй выход блока синхронизации соединен с вторым входом вычитающего счетчика и входом .регистра, одни из выходов которого подключен к второму входу регистра сдвига, пятый выход блока синхронизации соединен с одним входом элемента ИЛИ, другой вход которого подключен к входу управления блока памяти, выход элемента ИЛИ соединен с вторым входом счетчика адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Устройство для контроля блоков буферной памяти | 1987 |

|

SU1501175A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1647579A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278981A1 |

Изобретение относится к запоминаю щим устройствам и может быть использовано в качестве буферного запоминающего устройства при построении устройств обмена Цель изобретения - расширение области применения устройства за счет вьщачи информации через определенные интервалы времени. Устройство содержит блок памяти с информационными входами, регистр сдвига с информационными выходами, счетчик адреса, входы управления, вычитающий счетчик, регистр, элемент ИЛИ, блок синхронизации, управляющие выходы. Устройство работает в режиме записи, в режиме чтения при его использовании в цепи активный источник - пассивный приемник информации. При использовании устройства в системе с активным приемником и активным передатчиком все слова, записьгоаемые в блок памяти, должны содержать разряды и и в последнем слове , 2 ил. С/) ГС iJlai СП СХ) 00

71

2S

5

37

«

22

32

JJ

19

In

n

Л

-

2S

24

J6

JS

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3992699, кло G 11 С 19/00 опублико 1976„ | |||

Авторы

Даты

1986-08-07—Публикация

1984-12-07—Подача