. (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1984 |

|

SU1290521A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для измерения температуры | 1990 |

|

SU1742640A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2017203C1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Многоканальное устройство для ввода аналоговых данных | 1988 |

|

SU1501025A1 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1432776A1 |

изобретение относится к информационно-преобразовательной технике и может .быть использовано в устройств вах преобразования, например, напряжения в код.

Наиболее близким к предлагаемому является аналого-цифровой преобразователь, содержащий дифроанашоговый преобразователь, компаратор, генератор тактовых импульсов, триггер циклов, регистр сдвига, буферный регистр и блок управления, выполненный в виде выходного регистра, трехвходовых элементов И и линий задержкц, количество которых равно разрядам преобразования, причем вь1ход генератора тактовых импульсов (ГТИ) соединен с одним из входов элементов И каждого разряда, через элемент И ср учетными входами регистра сдвига «аждого разряда (кроме первого), . выполненного на последовательно соединенных КЗ-триггерах, через элемент И первого разряда регистра сдвига и через элемент задержки с одним из входов триггера циклов, выход которого соединен с элементом И первого разряда регистра сдвига, выход которого через линию задержки соединен с первым входом RS-триггера

1-го разряда регистра сдвига, выход которого соединен с вторым входом элемента И первого разряда, а выс ходы RS-триггеров всех последующих разрядов соединены с вторыми входами, элементов И соответствующих разря.дов и установочными входами выходного регистра блока управления, а ,

(О также элементами И регистра сдвига соответствующего разряда, применяю- щимися для формирования бита переноса сброса предыдущего RS-триггера в регистре сдвига, причем одновременно с э1:им третьим входы .эле15ментов К каждого разряда соединены с выходом компаратора через элемент НЕ, а выxoj№I элементов И через ли- . НИИ задержки каждого разряда соединены с R-Bходами триггеров вы20ходного регистра, который посредством ключей управляет выходом цифроаналогового преобразователя tl Недостатком устройства, является необходимость строгой синхронизации

25 и задержки во времени тактового импульса на R-вход и импульса запуска, на S-вход триггера циклов; импульсов на S-входе и R-входе первого разряда регистра сдвига; импульса

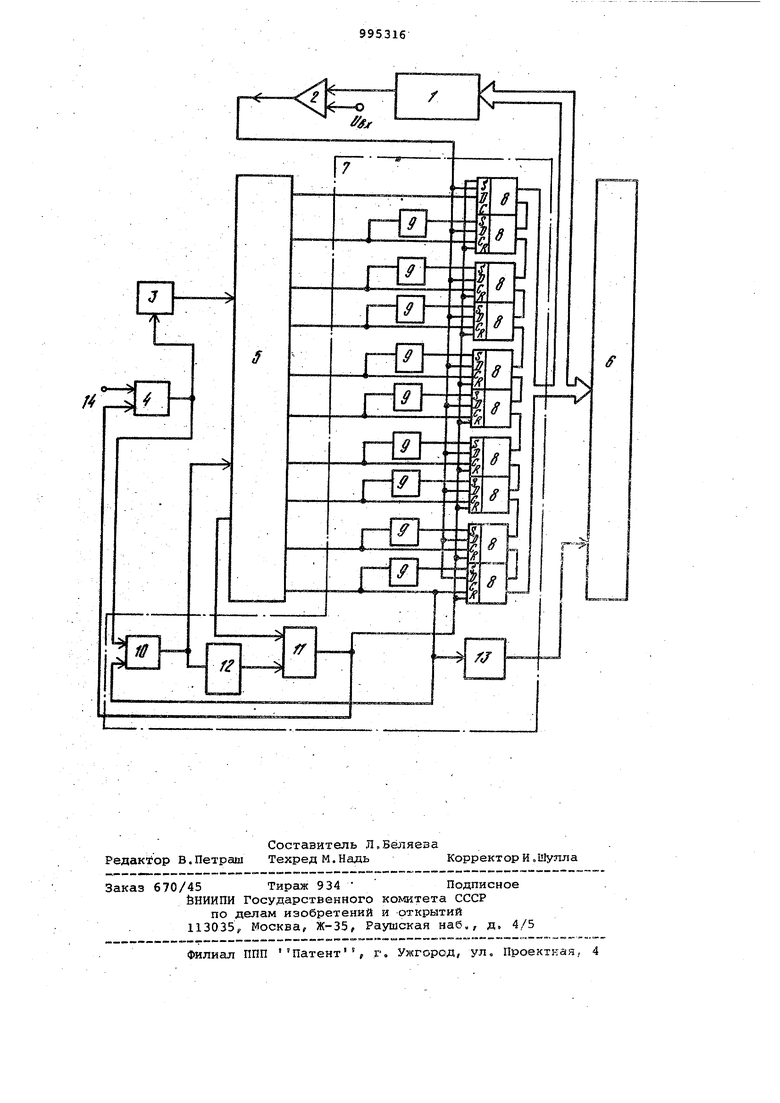

30 -G выхода компаратора, тактового импульса и одновременно с этим наличия предыдущего состояния триггера сдвига соответствующего разряда Это усложняет отладку схемы, требует сложных в реализации и ненадежны в работе схем, перенастройки схем при переходе на другой диапазон так вых частот, уменьшает быстродействие всего преобразователя в целом за счет наличия 2-тактной схемы синхронизации. Цель изобретения - повышение йлстродействия и надежности работы устройства. Поставленная цель достигается те что в аналого-цифровой преобразователь, содержащий блок управления, включающий регистр управления, выходы которого через цифроаналоговый преобразователь соединены с первым входом компаратора, второй вход которого соединен с входной шиной, триггер циклов, первый вход которого соединен с шиной запуска, генератор тактовых импульсов, выход которого соединен с первым входом регистра сдвига, введен буферный регистр и блок управления дополнительно включает узлы укорочения импульсов, генератор одиночных импульсов, элементы И и НЕ и линию за держки, причем выход триггера цикло соединен с входом генератора тактовых импульсов и с первым входом генератора одиночных импульсов, выход которого соединен с вторым входом регистра сдвига и через элемент НЕ с первым входом элемента И, второй вход которого соединен с выходом регистра сдвига, а выход соединен с вторым входом триггера циклов, 5 входом первого триггера и R-входами остальных триггеров регистра управления, С-входы которого соединены с соответствующими разрядными выходами регистра сдвига, а начиная с второго разряда через узл укорочения с S-входают соответствую щего разряда, при этом D-входы подключены к выходу компаратора, а выходы регистра управления подключены к входам буферного регистра, управляюший вход которого через линию за держки соединен с последним разрядным выходом регистра сдвига и вторым входом генератора одиночных импульсов . На.чертеже представлена схема аналого-цифрового преобразователя. Преобразователь содержит цифроаналоговый преобразователь (ЦАП) 1, компаратор 2, генератор 3 тактовых импульсов (ГТИ), триггер 4 циклов, регистр 5 сдвига, буферный регистр и блок 7 управления, состоящий из регистра 8 управления на D-триггера узлов 9 укорочения импульсов, генератора 10 одиночных импульсов, элемента И 31, элемента НЕ 12, линии 13 за,г,аржки, 14 - шина запуска. Аналого-цифровой преобразователь работает следующим образом. Импульс запуска поступает на установочный вход триггера 4 циклов, переводит его в состояние, включающее генератор -2 тактовых импульсов к генератор 10 коротких одиночных импульсов, выходной импульс которого необходим для записи в регистр 5 сдвига начальной информации (уровень О в первый разряд и уровень j во все последующие). С регистра 5 сдвига задержанный импульс, а также инвертированный элементом НЕ 12 импульс с выхода генератора 10 одиночных импульсов поступают на входы элемента ИИ. В результата этого образуется импульс, сбрасг шающий в нулевое состояние все разряды регистра 8 управления, кроме перЕОГО, а в первом триггере регистра 6 уровень 1 . Одновременно импульс с выхода элемента И 11 поступает на сброс триггера 4 циклов, но, так как импульс запуска по длительности больше, чем импульс с выхода элемента И 11, триггер 4 циклов остается в прежнем состоянии. После поступления импульса на С-вход триггера 1-го разряда регистра 8 управления на его выходе появляется сигнал, который коммутирует старший разряд цифроаналого-; вого преобразователя 1, Вес (напряжение ) г соответствующий старшему разряду, сравнивается с исследуемым сигналом (напряжение Ug) на компараторе 2. В случае на D-входы (до окончания тактового импульса, поступившего на С-вход) регистра 8 управления подается уровень . При этих условиях на выходе D-триггера регистра 8 управления сохраняется уровень IV. При Ue,Um,f, с компаратора 2 поступает уровень О на D-вход указанного разряда и происходит запись О на выходе . Следующие тактовые импульсы генератора 3 производят сдвиг уровня О с 1-го разряда во все последующие разряды регистра 5 сдвига. Сформированные таким образом нулевые уровни для каждого разряда поступают на С-входы соответствующих D-триггеров регистра В управления, а также через узлы 9 укорочения импульсов на их S-входы. Выходы регистра 8 управления коммутируют соответствующие ключи ЦАП 1, при этом напряжение с выхода цифроаналогового поеобразователя 1 сравнивается с

исследуемым сигналом Ug,, на компараторе 2. При этом происходит суммирвание весов (напряЯсений) каждого последующего разряда ЦАП 1 и выставляется код на регистре 8 управления, определяющий величину входного исследуемого сигнала.

импульс регистра 5 сдвига последнего разряда, записав в регистр 8 управления информацию по результатам поразрядного уравновешивания ВХОДНОГО:сигнала с опорным напряжением ЦАП 1, через линию 13 задержки переписывает, ее в буферный регистр 6 Линия 13 задержки вводится с целью записи истинной информации из регистра 8 управления только лишь после прихода импульса с компаратора 2 на D-вход последнего разряда регистра 8 управления. Одновременно импульс последнего разряда регистра 5 -сдвига поступает .на генератор 10 одиночных импульсов, кот/орый при этом стирает информацию в регистре 5 сдвига и формирует на элементе И 11 импульс, задержанный на время, определенное длительностью импульса генератора 10 одиночных импульсов. Импульс генератора 10 сбрасывает в начальное состояние всё (кроме первого) разряды регистра 8 и переводит триггер 4 циклов в .состояние, запрещающее работу генератора 3 до прихода следующего Импульса Запуск (строб от ЭВМ или любой дауг импульс). С приходом следующего импульса запуска процесс повторяется.

В буферном регистре информация сохраняется дц след1ующего цикла и может считываться в любое время, вплоть до окончания нового цикла преобразования.

Благодаря предлагаемому построению блока 7 управления преобразование заканчивается аа время, мень-г шее длительности такта (в прототипе для преобразования необходимо 2 тактовых импульса).

Таким образом, №1стродействие устройства, увеличивается за счет отсутствия второго тактирующего импульса в l+1/n раз, где п-число разрядов преобразования, и за счет сокращения периода цикла обработки

сигнала по цепи ЦАП - компаратор блок управления. .

Формула изобретения

Аналого-цифровой преобразователь, содержащий блок управления, включающий регистр управления, .выхода которого через цифроаналоговый преобразователь соединены с первым входом компаратора, второй вход, которого соединен с входной шиной, триггер циклов, первый вход которого соединен с шиной запуска, генератор тактовых импульсов, выход которого соединен с первым входом регистра

5 сдвига, отличающийся тем, что, с целью повышения быстродействия и надежности в работе, в него введен буферный регистр и блок управления дополнительно вклю0чает узлы укорочения импульсов, генератор одиночных импульсов, элементы И -и НЕ и линию задержки, причем выход триггера циклов соединен с входом генератора, тактовых 5 импульсов и с первым входом генератора одиночных импульсов, выход которого соединен с вторым входом регистра .сдвига и через элемент НЕ с первым входом элемента И, второй

0 вход которого соединен с выходом регистра сдвига, а выход соединен с вторым входом триггера циклов, S-входдм первого триггера и R-входами остальных триггеров регистра уп5 равления, С-входы которого соединены . с соответствующими разрядными выходами регистра сдвига, а начиная с второго разряда через узлы укорочения с S-входами соответствующего разп ряда, при этом В-входал подключены к выходу кс 1паратора, а выходы регирх.ра управления подключены к входам буферного регистра,, упра&ляю&шй вход которого через линию задержки соедо1нен с последним разрядным вы5ходом регистра сдвига и вторым вхб-. дом генератора одиночных импульсов.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1983-02-07—Публикация

1981-04-16—Подача