(54) ДЕШИФРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1221648A1 |

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1129597A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ГОСУДАРСТВЕННОГО РЕГИСТРА НАСЕЛЕНИЯ | 2004 |

|

RU2276806C1 |

| Устройство для считывания и кодирования изображений объектов | 1986 |

|

SU1548800A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ПОГРАНИЧНОГО КОНТРОЛЯ | 2006 |

|

RU2316811C1 |

| Устройство для обнаружения и исправления ошибок | 1980 |

|

SU938415A1 |

| Устройство для сопряжения электроннойВычиСлиТЕльНОй МАшиНы C уСТРОйСТВОМВВОдА-ВыВОдА | 1979 |

|

SU809141A1 |

| Устройство для ввода информации | 1990 |

|

SU1709294A1 |

1

Изобретение относится к технике преобразования электрических сигналов и может быть использовано в телеметрических системах и автоматизированных системах управления, при сборе накопленной информации с удаленных объектов.

Известен дешифратор, содержащий элементы ИЛИ, блок сравнения, блок управления перезаписью, тактовую шину, ячейки памяти, блок формирования сигнала сброса, п вентильных блоков, блок временной зашиты, блок формирования кодового образа 1.

Недостаток указанного дешифратора в том, что при потере хотя бы одного бита (разряда) текущего кодового образа в радиоканале, этот и все последующие .кодовые образы выделены не будут, что приведет к потере телеметрической информации.

Цель изобретения - повышение надежности.

Для достижения указанной цели в дешифратор, содержащий последовательно соединенные через первые элементы ИЛИ п ячеек памяти, блок сравнения, выполненный на однотипных ячейках, блок управления перезаписью, вход которого соединен с

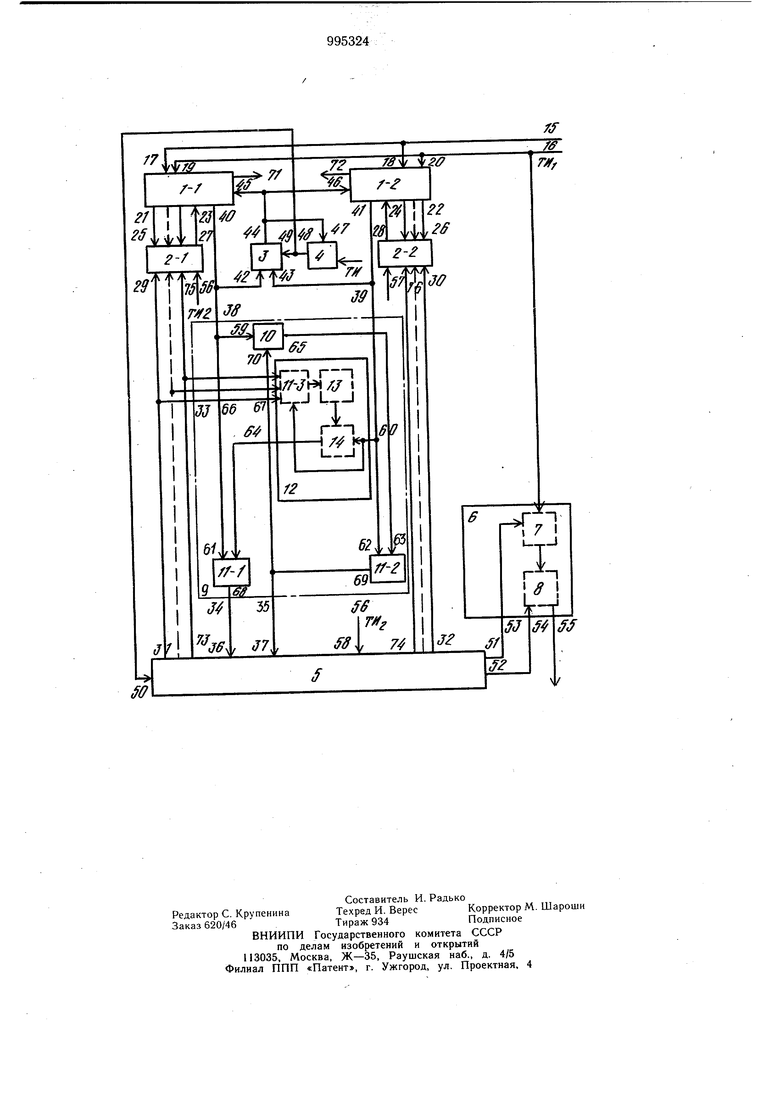

тактовой шиной, а выход - с первыми входами соответствующей ячейки памяти, блок формирования сигнала сброса и п вентильных блоков, соединенных последовательно, элементы ИЛИ, блок временной защиты и 5 блок формирования кодового образа, причем первый и второй выходы каждого вентильного блока подключены к второму и третьему входам соответствующей ячейки памяти и первому и второму входам соответствующей ячейки блока сравнения, третьи входь которых соединены с тактовой шиной, при этом четвертый вход первой ячейки блока сравнения соединен с блоком формирования кодового образа непосредственно, а остальных ячеек - через COOTIS ветствующие вторые элементы ИЛИ, причем первый вход блока формирования кодового образа подключен к тактовой шине, второй - к выходу блока временной защиты и входу блока формирования сигнала сброса, а третий - к входу блока времен ° ной защиты, выходу п-го вентильного блока и другом входу блока формирования сигнала сброса, выход которого соединён с четг вертыми входами ячеек памяти, выходы которых подключены к другим входам соответствующих вентильных блоков, кроме того, выходы ячеек блока сравнения через соответствующие третьи элементы ИЛИ подключены к другому входу блока управления перезаписью, введены блок управления выдачей кодовых образов, формирователь управляющего сигнала, второй блок сравнения и второй селектор кодовых образов, входы которого подключены к входу и первому синхронизирующему входу дещифратора, второй управляющий вход второго селектора кодовых образов соединен с выходом блока формирования сигнала сброса, первый управляющий вход и выход второго селектора кодовых образов соединены с выходом и первым входом второго блока сравнения соответственно, а его управляющий выход соединен с входом блока формирования сигнала сброса и вторым входом блока управления выдачей кодовых образов, первый вход которого соединен с управляющим выходом первого селектора кодовых образов, а его третий вход и выход соединены соответственно с первым выходом и первым и вторым входами блока формирования кодовых образов второй выход котого соединен с вторым входом второго блока сравнения, а его управляющие выходы - с первым и вторым входами формирователя управляющего сигнала, выход и синхронизирующий вход которого являются выходом и первым синхронизирующим входом дешифратора соответственно. Блок управления выдачей кодовых образов содержит узлы четного и нечетного управления и два элемента ИЛИ, первый и второй входы блока являются первыми входами узла четного управления и первого элемента ИЛИ и узла нечетного управления и второго элемента ИЛИ соответственно, второй вход узла нечетного управления является третьим входом блока, а его выход соединен с вторым входом первого элемента ИЛИ, выход которого является первым выходом блока, второй выход которого соединен с вторым входом узла четного управления и подключен к выходу второго элемента ИЛИ, второй вход которого соединен с выходом узла четного управления. На чертеже приведена функциональная схема предлагаемого дещифратора. Устройство содержит селекторы 1 - 1 - 1-2 кодовых образов; блоки 2-1 - 2-2 сравнения, блок 3 формирования сигнала сброса блок 4 временной защиты, блок 5 формирования кодовых образов, формирователь 6 управляющего сигнала, счетчик 7, элемент ИЛИ 8, блок 9 управления кодовых образов, узел 10 четного управления, элементы ИЛИ 11 - 1 - 11-3, узел 12 нечетного управления, счетный 13 триггер, вентиль 14. Вход 15 дешифратора и его первый синхронизирующий вход 16 являются соответствующими входами 17, 18 и 19, 20 первого 1 - 1 и второго 1-2 селекторов, выходы 21 и 22 и управляющие входы 23 и 24 которых соединены с входами 25, 26 и выходами 27, 28 соответствующих блоков 2-2 сравнения, вторые входы 29 и 30 которых соединены с первым 31 и вторым 32 выходами блока 5 формирования кодовых образов, первый выход которого, кроме того, соединен с третьим входом 33 блока 9 управления выдачей кодовых образов: первый 34 и второй 35 выходы которого соединены с входами 36 и 37 соответственно, а его первый 38 и второй 39 входы соединены с управляющими выходами 40 и 41 селекторов 1 - 1 - 1-2 соответственно, которые соединены также с входами 42 и 43 блока 3 формирования сигнала сброса выход 44 которого соединен с вторыми управляющими входами 45 и 46 селекторов 1 - 1 - 1-2, а также с входом 47 блока 4 временной защиты, выход 48 которого соединен с третьими входами 49 и 50 блока 3 и блока 5, управляющие выходы 51 и 52 которого соединены с входами 53 и 54 формирователя 6 управляющего сигнала, выход 55 которого является выходом дещифратора, а его синхронизирующий вход - его первым 16 синхронизирующим входом, второй 56 синхронизирующий вход которого является аналогичным входом блока 2-1 сравнения и входом 57 блока 2-2 сравнения, а также входом 58 блока 5 формирования кодового образа. Кроме того, первый 38 и второй 39 входы блока 9 управления выдачей кодовых образов соединены с первыми входами 59 и 60 соответственно четного 10 и нечетного 12 узлов управления и входами 61 первого 11 - 1 и 62 второго 11-2 элементов ИЛИ соответственно, второй вход первого элемента ИЛИ 11-1 и второй вход 63 второго элемента ИЛИ 11-2 соединены соответственно с выходами 64 и 65 узлов 12 нечетного управления и 10 четного управления, при этом третий вход 66 блока является вторым входом 67 узла 12, а первый 34 и второй 35 выходы блока - соответственно выходами 68 и 69 первого 11 - 1 и второго И-2 элементов ИЛИ, выход 69 второго элемента ИЛИ 11-2 подключен также к второму входу 70 узла 10; 71 и 72 - выходы селекторов 1 - 1 - 1-2, 73 и 74 - выходы блока 5 формирования кодовых образов, 75 и 76 - входы блоков 2-1 и 2-2 соответственно. На входы 15 и 16 поступают синфазно бит информации и тактовый сигнал, которые запоминаются в селекторах 1 - 1 - 1-2, а также поступают на соответствующие входы 25 и 27 блоков 2-1-2-1 сравнения, где сравниваются с соответствующими разрядами кодовых образов, которые поступают на входы 29 и 30 блоков 2-1 - 2-2. При этом на вход 29 блока 2-1 поступает первый J oдoвый образ, а на вход 30 блока 2-2 - второй кодовый образ. При равенстве сравниваемых разрядов изменений в селекторах не происходит и они не принимают следующие разряды (биты) информации. При неравенстве на управляющем выходе 27 или 29 формируется сигнал продвижения, который сдвигает накопленный код на выход 71 (72) на один бит (разряд) принятого кода и накопление и сравнение принятого кода с заданным кодовым образом продолжается. При обнаружении заданного кодового образа в поступившей на вход 15 информации, т. е. при равенстве всех разрядов поступившего кода и кодового образа, задаваемого блоком 5, формируется сигнал на выходе 40 или 41 селектора 1 - 1 или I-2. Рассмотрим конкретные условия дешифрирования. 1. Допустим, условия радиоканала обеспечивают надежный прием информации. С выхода 73 блока 5 подается первый кодовый образ, которьш поступает на вход 75 блока 2-1 для сравнения, а также проходит через элемент ИЛИ 11-3 на вход счетного триггера 13, который перебрасывается и открывает вентиль 14. На выход 74 блока 5 подается второй кодовый образ, который поступает на вход 76 блока 2-2 для сравнения. На входы 15 и 16 поступают биты текущей информации и тактовые сигналы, которые запоминаются в селекторах 1-1 - 1-2 и сравниваются в блоках 2-1 - . При отыскании первого кодового образа на выход 40 селектора 1 - 1 поступает сигнал, который через блок 3 поступает на . входы 45 и 46 селекторов 1 - 1 - 1-2 и сбрасывает их, а также на вход 47 блока 4, который сбрасывается и начинает отсчет интервала временной защиты. Если в течение заданного защитного интервала времени блок 4 не будет сброшен, то на его выход 48 поступит сигнал, который сбросит в исходное состояние блок 5 (по входу 50 и через блок 3 селекторы 1-1 и 1-2. Сигнал с выхода 40 селектора 1--1 поступает также на вход 59 узла 10 четного управления и через первый элемент ИЛИ 11 -1 на вход 36 блока 5, который на выход 73 подает третий кодовый образ. Этот образ поступает на вход 75 блока 2-1 для сравнения, а также через третий элемент ИЛИ 11-3 (вход 67) на вход триггера 13, который возвращается в исходное состояние и закрывает вентиль 14. Затем выделяется второй кодовый образ и на выход 41 селектора 1-2 поступает сигнал, который через блок 3 возвращает в исходное состояние селекторы 1 - 1 - 1-2 и блок 4, а также поступает на вход закрытого вентиля 14 и через элемент ИЛИ 11-3 на вход триггера 13, который открывает вентиль 14, кроме того, через второй элемент ИЛИ 11-2 на вход 70 узла 10, который сбрасывается, и на вход 37 блока 5, который подает на вход 57 блока 2-2 четвертый кодовый образ. 2. Допустим, в радиоканале потерян хотя бы один бит первого кодового образа. Первый кодовый образ с выхода 73 блока 5 поступает на вход 75 блока и через третий элемент ИЛИ 11-3 на вход триггера 13, который открывает вентиль 14. Второй кодовый образ с выхода 74 блока 5 поступает на вход 76 блока 2-2. Так как первый кодовый образ селектором 1 - 1 и блоком 2-1 не выделяется, то через некоторое время селектируется второй кодовый образ и на выход 41 селектора 1-2 поступает сигнал, который через блок 3 сбрасывает селекторы 1-1 - 1-2 и блок 4, а также поступает через третий элемент ИЛИ И-3 на йход триггера 13 и через открытый вентиль 14 и первый элемент ИЛИ И - 1 на выход 44 блока 5. При этом триггер 13 возвращается в исходное состояние и закрывает вентиль 14, а блок 5 подает третий кодовый образ на вход 75 блока 2--1 сравнения и через третий элемент ИЛИ 11-3 на вход триггера 13, который перебрасывается и открывает вентиль 14. Кроме того, сигнал с выхода 41 через второй элемент ИЛИ 11-2 (вход 62) поступает на вход 70 узла 10, который сбрасывается, и на вход 37 блока 5, на выход 74 которого подается четвертый кодовый образ. 3. Допустим, в радиоканале потерян второй кодовый образ. В этом случае сигнал с выхода 40 поступает на вход 42 блока 3 и на вход 59 узла 10, который собран по схеме счетного триггера, а также через элемент ИЛИ 11-1 на вход 36 блока 5, на выход 73 которого поступает третий кодовый образ. Так как второй кодовый образ не выделяется селектором 1-2 и блоком 2-2, то следующим выделяется третий кодовый образ. Поэтому на выход 40 селектора 1 - 1 снова поступит сигнал, который подается на вход блока 3, через элемент ИЛИ 11 - 1 на вход 36 блока 5, на выход 73 которого подается пятый кодовый образ. Этот кодовый образ через элемент ИЛИ 11-3 и триггер 13 закрывает вентиль 14. Кроме того, сигнал с выхода 40 селектора 1 - 1 поступает на вход 59 узла 10, на выходе 65 которого формируется в этом случае сигнал, который через элемент ИЛИ 11-2 -поступает на вход 37 блока 5, на выход 74 которого поступает четвертый кодовый образ. Работа блоков 2 и 5 синхронизируется тактовыми сигналами с входа 16. После селекции (п-1) кодового образа на выходе 51 блока 5 формируется сигнал, который поступает на вход счетчика 7 и запускает его. Счетчик суммирует тактовые сигналы с входа 16 и, после отсчета заданного интервала, равного интервалу между (п-1) и п кодовым образом, на его выход поступает сигнал, который через элемент ИЛИ 8 поступает на выход 55 дешифратора. В случае селекции п-го кодового образа сигнал с выхода 29 через элемент ИЛИ 8 поступает на выход 30. При селекции кодовых образов п-1 и п сигналы на выход 30 поступают одновременно. Кодовые интервалы между кодовыми образами произвольны, но между (п-1) и п кодовыми образами такой интервал жестко соответствует заданному числу тактовых импульсов на входе 34. Сигнал на выходе 30 дешифратора сигнализирует о том, что следуюший- бит информации является сигналом передачи телеметрических или иных сообщений. Предлагаемое устройство обеспечивает компенсацию постоянных в радиоканале кодовых образов. Кроме того, дешифратор формирует на выходе 30 управляющий сигнал при выходе из строя одного из каналов (селектор - блок сравнения), что повыщает его надежность, оперативно изменяет кодовые образы (изменение символов О и 1 в таких образах) без изменения какихлибо аппаратурных доработок, что расширяет область его применения. Формула изобретения 1. Дешифратор, по авт. св. № 754672, отличающийся трм, что, с целью повышения надежности, в него введены блок управления выдачей кодовых образов, формирователь управляющего сигнала, второй блок сравнения и второй селектор кодовых образов, входы которого подключены к входу и первому синхронизирующему входу дещифратора, второй управляющий вход второго селектора кодовых образов соединен с выходом блока формирования сигнала сброса, первый управляющий вход и выход второго селектора кодовых образов соединены с выходом и первым входом второго блока сравнения соответственно, а его управляющий выход соединен с входом блока формирования сигнала сброса и вторым входом блока управления выдачей кодовых образов, первый вход которого соединен с управляющим выходом первого селектора кодовых образов, а его третий вход и выход соединены соответственно с первым выходом и первым и вторым входами блока формирование кодовых образов, второй выход которого соединен с вторым входом второго блока сравнения, а его управляющие выходы - с первым и вторым входами формирователя управляющего сигнала, выход и синхронизирующий вход которого являются выходом и первым синхронизирующим входом дещифратора соответственно. 2.. Дешифратор по п. 1, отличающийся тем, что блок управления выдачей кодовых образов содержит узлы четного и нечетного управления и два элемента ИЛИ, при этом первый и второй входы блока являются первыми входами узла четного управления и первого элемента ИЛИ и узла не-, четного управления и второго элемента ИЛИ соответственно, второй вход узла нечетного управления является третьим входом блока, а его выход соединен с вторым входом первого элемента ИЛИ, выход которого является первым выходом блока, второй выход которого соединен с вторым входом узла четного управления и подключен к выходу второго элемента ИЛИ, второй вход которого соединен с выходом узла четного управления. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 754672, кл. Н 03 К 13/24, 01.06.76 (прототип) .

Авторы

Даты

1983-02-07—Публикация

1981-09-24—Подача