лятого и шестого элементов И второй группы, выходы элементов И первой и второй групп каждого блока выработки синхросигналов являются соответственно первой и второй группами выходов устройства, о т л ич а ющ е е с я тем, что, с целью расширения функциональных возмоЯсностей за счет обеспечения переминного периода синхросигналов в нечетные и четные такты работы устройства, в него введен блок вьфаботки сигналов начальной установки, блок переключателей, блок формирования сигналов управления режимами, элементы задержки группы с ( 1)-го по (2 п +1)-й, и в каждый блок выработки синхросигналов введены второй и третий элементы НЕ, второй элемент задержки, третий счетчик первый, второй и третий элементы ИНЕ, первый и второй элементы И, третий и четвертьй селекторы, первый, второй, третий и четвертый регистры сдвига, первый, второй, третий и чет- вертьй триггеры, первый и второй узлы управления, первый и второй узлы сравнения, третья и четвертая группы элементов И, причем выход задающего генератора соединен с входом блока выработки сигналов начальной установки, выход которого соединен с входами элементов задержки группы с ( п+1)-го по (2 п +1)-й, выходы элементов задержки группы с (п +1)-го по 2п -и соединены соответственно с установочными входами блоков вьфаботки синхросигналов с первого по п-й, выходы блока переключателей соединены соответственно с группой информационных входов блока формирования сигналов управления режимами, синхровход которого соединен с выходом (2п+1)-го элемента задержки группы, первый выход блока формирования сигналов управления режимами соединен с первыми управляюпщми входами блоков выработки синхросигналов, вторые управляющие входы которых соединены со вторым выходом блока формирования сигналов управления режимами, третий выход которого соединен с третьими управляюпщми входами блоков выработки синхросигналов, при этом в каждом блоке вьфаботки синхросигналов выход первого элемента задержки соединен с синхровходом первого регистра сдвига, с синхровходом первого триггера, с сннхровходом второго триггера, с

синхровходом второго регистра сдвига, с синхровходом первого узла управления, с первыми входами элементов И третьей группы, первым входом первого элемента И-НЕ, второй вход которого соединен с установочным входом блока, с первым входом второго элемента И-НЕ, второй вход которого соединен с выходом первого элемента НЕ, с синхровходом третьего регистра сдвига, с синг v хровходом четвертого триггера, с синхровходом четвертого регистра сдвига, с синхровходом второго узла управления, с первыми входами элементов И четвертой группы, вторые входы которых соединены с выходом второго узла управления, с управляющим входом третьего регистра сдвига, прямой выход первого разряда которого соединен с первым входом первой группы

первого узла сравнения, второй вход первой группы которого соединен с инверсным выходбм первого разряда третьего регистра сдвига, прямой выход второго разряда которого соединен с третьим входом первой группы первого узла сравнения, четвертый вход первой группы которого соединен с инверсным выходом второго разряда третьего регистра сдвига, информационный вход которого соединен с инверсным выходом второго разряда второго счетчика, первый вход второй группы первого узла сравнения соединен с прямым выходом первого разряда второго .счетчика, инверсньй выход первого разряда которого соединен

со вторым входом второй группы первого узла сравнения, третий вход второй группы которого соединен с прямым выходом второго разряда второго счетчика, инверсный вькод второго разряда которого соединен с четвертью входом второй группы первого узла сравнения, первый, второй, третий и четвертый выходы второго дешифратора соединены соответственно с третьими входами первого, второго, третьего и четвертого элементов И четвертой группы, четвертый выход второго дешифратора подключен к управляющим входам третьего и четвертого триггеров и четвертого регистра сдвига, выход первого элемента И-НЕ соединен с установочным входом второго счетчика, выход второго элемента И-НЕ соединен с установочным входом первого счетчика, прямой выход первого разряда которого

соединен с первым входом первой группы второго узла сравнения, второй вход первой группы которого соединен с инверсным выходом первого разряда первого счетчика, прямой выход второго разряда которого соединен с третьим входом первой группы второго узла сравнения, четвертый вход первой группы которого соедийен с инверсным выходом второго; разряда первого счетчика и с информационньм входом первого регистра сдвига, прямой выход первого разряда которого соединен с первым входом второй группы второго узла сравнения, второй вход второй группы которого соединен с инверсным вькодом первого разряда первого регистра сдвига, прямой выход второго разряда которого соединен с третьим входом второй группы второго узла сравнения, четвертый вход второ группы которого соединен с инверсным выходом второго разряда первого регистра сдвига, управляющий вход,которого соединен с выходом первого узла управления, со вторыми входами первого, второго, третьего и четвертого элементов И третьей группы, третьи входы первого, второго и третьего элементов И третьей группы соединены соответственно с первым, вторым и третьим выходами первого дешифратора, четвертый выход первого дешифi ратора соединен с третьим входом четIвертого элемента И третьей группы, с управляющим входом первого триггера, с управлякицим входом второго триггера и с управляющим входом второго регистра сдвига, прямой выход первого разряда которого соединен с первым информационным входом первого узла управления, второй информационный вход которого соединен с инверсным выходом второго разряда второго регистра сдвига, инверсный выт .ход первого триггера соединен с третьим информационным входом первого узла управления, с первым входом третьего элемента И-НЕ, с первым входом первой группы третьего селектора, с входом второго элемента задержки, выход которого соединен с входом второго элемента НЕ, выход которого соединен со вторым входом третьего элемента И-НЕ, выход, которого соединен с установочным входом третьего счетчика, счетный вход которого соединен с выходом третьего

элемента НЕ, с первым входом первого элемента И, с первым входом второго элемента И с первым входом первой группы четвертого селектора и с первым входом второй группы входов трет тьего селектора, инверсный выход которого соединен с информационным входом второго регистра сдвига, прямой выход третьего счетчика соединен со вторым входом первого элемента И, инверсньй выход третьего счетчика соединен со вторым входом второго элемента И, выход которого соединен со вторым входом первой группы третьго селектора, второй вход второй группы которого соединен с инверсным выходом второго триггера и с четвертым информационным входом первого узла управления, пятый информационный вход которого соединен с выходом второго узла сравнения, первый управляющий вход каждого блока выработки синхросигналов соединен с информационным входом первого триггера, с информаг онным входом третьего триггера, инверсный выход которого соет динен с первым входом второй группы четвертого селектора, второй вход первой группы которого соединен с инверсным выходом четвертого триггера, первый информационный вход второго узла управления соединен с прямым выходом первого разряда четвертого регистра сдвига, инверсный выход второго разряда которого соединен со вторым информационным входом второго узла управления, третий четвертый и пятый информационные входы которого соединены соответственно с инверсным выходом третьего триггера, инверсным выходом четвертого триггера и с выходом первого узла сравнения, выход первого элемента И соединен со вторым входом второй группы четвертого селектора, инверсньА выход которого соединен с информационным входом четвертого регистра сдвига, второй управляющий вход каждого блока выработки синхросигналов соединен с информационным входом второго триггера и с информационным входом четверт го триггера, третий управляющий вход каждого блока выра-, ботки синхросигналов соединен с входом третьего элемента НЕ, выходы элементов И третьей и четвертой групп каждого блока выработки синхросигналов являются соответственно третьей и четвертой группой выходов устройства, при этом каждый узел управления содержит три элемента И-НЕ, два селектора, элемент И, причем в узле управления первый информационный вхо соединен с первым входом первого эле мента И-НЕ, с первым входом первой группы входов первого селектора и с первым входом первой группы второго селектора, прямой выход которого сое динен с первым входом второй группы входов второго селектора, второй вход второй группы которого соединен с первым входом второй группы первог селектора и с выходом второго элемен та И-НЕ, первый вход которого является синхровходом узла, второй информационный вход которого соединен с первым входом третьего элемента И-НЕ, выход которого соединен с первым входом элемента И, выход которог соединен со вторым входом второго эл мента И-НЕ и является выходом узла, третий информационный вход которого соединен со вторым входом первой группы первого селектора, со вторым входом второй группы первого селектора, со вторым входом первой группы второго селектора и с третьим входом второй группы второго селектора, инверсный выход которого соединен с третьим-входом второй группы первого селектора, инверсный выход которого соединен со вторьм входом элемента И третий вход которого соединен с выходом первого элемента И-НЕ, второй вход которого соединен со вторым входом третьего элемента И-НЕ и является четвертым информационньпи входом узла, пятый информационный вход которого соединен с четвертым входом элемента И. 2. Устройство по п. 1, отличающееся тем, что каждый узел сравнения содержит пять элементов И-НЕ, причем первый вход первой груп пы входов узла соединен с первым вхо дом первого элемента И-НЕ, с первым входом второго элемента И-НЕ, выход которого соединен с первым входо третьего элемента И-НЕ, второй вход которого соединен с выходом четвертого элемента И-НЕ, первый вход которого соединен с первым входом пятого элемента И-НЕ и является вторым входом первой группы входов узла, третий вход первой группы входов которого соединен со вторым входом пер 97 вого элемента И-НЕ, .со вторым входом пятого элемента И-НЕ, выход которого соединен с третьим входом третьего элемента И-НЕ, выход которого является выходом узла,четвертый вход первой группы входов которого соединен со вторым входом четвертого элемента И-НЕ, со вторым входом второго элемента И-НЕ, первый вход второй группы входов узла соединен с третьим входом второго элемента И-НЕ, с третьим входом первого элемента И-НЕ, выход которого соединен с четвертым входом третьего элемента И-НЕ, второй вход второй группы входов которого соединен с третьим входом четвертого элемента И-НЕ, третий вход второй группы входов которого соединен с четвертым входом первого элемента И-НЕ, с четвертым входом пятого элемента И-НЕ, четвертый вход второй группы входов узла соединен с четвертым входом четвертого элемента ИНЕ, с четвертым входом второго элемента И-НЕ, 3« Устройство по п. 1, /о т л ичающееся тем, что блок формирования сигналов управления режимами содержит два триггера, регистр сдвига и элемент И, причем информаг онный вход первого триггера, информационный вход второго триггера, информационньй вход регистра сдвига являются соответственно первы, вторым, третьим входами группы информационных входов блока, синхровход которого соединен с синхровходом регистра сдвига, с синхровходом второго триггера-и с синхровходом первого триггера, выход которого соединен с первым выходом блока, второй выход которого соединен с выходом второго триггера, прямой выход первого разряда регистра сдвига соединен с первым входом элемента И, второй вход которого соединен с инверсным выходом второго разряда регистра сдвига, выход элемента И соединен с третьим выходом блока. 4. Устройство по п. 1, о т л и I, что блок вырачающееся тем. б.отки сигналов начальной установки содержит два счетчика, элемент И, причем вход блока соединен с синхровходом первого счетчика, с синхровходом второго счетчика и спервым входом первого элемента И, второй вход которого соединен с инверсным

выходом первого разряда первого счетчика, прямой выход первого разряда которого соединен с управляющим вхо- дом второго счетчика, инверсньш вы11295972

ход первого разряда которого соединен с третьим входом элемента И, выход которого соединен с выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU974364A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1221648A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Устройство для синхронизации цифровой системы | 1981 |

|

SU981980A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1287138A1 |

| Устройство для синхронизации с контролем | 1983 |

|

SU1161933A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1367015A1 |

| Устройство для синхронизации внешних блоков памяти | 1985 |

|

SU1254457A1 |

1. УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее задающий генератор, группу элет ментов задержки, группу блоков выработки синхросигналов, причем выход задающего генератора соединен с входами элементов задержки группы с первого по п-й где п- число каналов вычислительной системы), выходы которых соединены соответственно с синхровходами блоков выработки синхро сигналов, каждый из которых содержит два счетчика, два селектора, два дешифратора, две группы элементов И, первый элемент задержки, первый элемент НЕ, причем в каждом блоке выработки синхросигналов синхровход блока соединен с входом первого элемента НЕ и с входом первого элемента задержки, выход которого соединен с первыми входами элементов И первой группы и с синхровходом первого счетчика, прямой выход первого разряда которого соединен с первым входом первого деишфратора и с первым входом Первой группы входов первого селектора, второй вход первой группы входов которого соединен с прямым выходом второго разряда первого счетчика и со вторым входом первого дешифратора. третий вход которого соединен с инверсным выходом первого разряда первого счетчика, с первым входом второй группы входов первого селектора, второй вход второй группы входов которого соединен с инверсным выходом второго разряда первого счетчика и с четвертым входом первого деишфратора, выходы которого соединены соответственно со вторыми входами первого, второго, третьего и четвертого элементов И первой группы, прямой и инверсный выходы первого селектора соединены соответственно со вторыми входами пятого и шестого элементов И первой группы, выход первого элемента НЕ соединен с первьгми входами эле(П ментов И второй группы и с синхровходом второго счетчика, прямой выход первого разряда которого соединен с первым входом второго дешифратора,, с первьпк входом первой группы входов второго селектора, второй вход первой группы.входов которого соединен с прямым выходом второго разряда второго счетчика и со вторьЫ входом второго дешифратора, третий вход которого соединен с инверсным выходом первого разряда второго счетчика и с первым входом второй группы входов второго селектора, второй вход второй группы входов которого соедит нен с инверсным выходом второго разряда второго счетчика и с четвертым входом второго дешифратора, выходы которого соединены соответственно со вторыми входами первого,второго, тертьего и четвертого элементов И второй группы, прямой и инверсный выходы второго селектора соединены Соответственно со вторыми входами

Изобретение относится к вычислительной технике, а именно к синхронизируемым вычислительным системам.

Известно устройство для синхронизации вычислительной системы, содержащее задающий генератор, две группы элементов задержки, группу блоков выработки синхросигналов, блок выработки сигналов начальной установки, блок переключателя, блок формирования сигналов управления режимами, причем выход задающего генератора соединен с входами-элементов задержки первой группы с первого по п-й (где п - число каналов), с входом блока вьгработки сигналов начальной установки, выходы которого соединены с входами элементов задержки первой группы с (п +1)-го по 2п-й группа выходовблока переключателей соединена с группой входов блока формирования сигналов управления режимами, первая группа выходов которого соединена соответственно с первыми управляю- : щими входами блоков выработки сигналов начальной установки, вторые управляющие входы-которых соединены соответственно со второй группой выходов блока формирования сигналов уп- равления режимами, третья группа выходов которого соединена соответственно с третьими управляющими входами блоков выработки синхросигналов, синхровходы которых соединены соответ- ственно с выходами элементов задержки первой группы с первого по h-й, выходы элементов задержки первой группы с (п+1)-го по 2 п-й соединены соответственно с установочными входами , блоков вьфаботки синхросигналов, вы-i ходы блоков выработки синхросигналов соединены соответственно с входами элементов .задержки второй группы, вькоды которых являются выходами устройства. Это устройство вырабатывает четыре фазы синхросигналов, сдвинутых giPYr относительно друга на Т д (4) ,

где Тд, - длительность машинного такта синхронизируемой, системы, и на величину выбранной фиксированной задержки ГО- Недостаток этого устройства заключается в том, что сдвиг синхросигналов определяется величиной задержки, постоянной для определенной конфигурации 6Л.ОКОВ синхронизируемой вычислительной системы. Это не позволяет автоматически изменить частоту задающего генератора (и тем самым величину T, и сдвиг синхросигналов один относительно другого) в процессе вычислений в соответствии с решаемой задачей вычислительной системой для уменьшения времени выполнения команд.

Наиболее близким по технической сущности к предложенному является устройство для синхронизации вычислительной системы, содержащее задающий генератор, выход которого соединен с входами элементов задержки, выходы которых соединены соответственно с входами блоков выработки синхросигналов, каждый из которых содержит два счетчика, два депшфратора, два селектора, две группы элементов И, повторитель, элемент НЕ, причем вход каждого блока выработки синхросигналов соединен с входом повторителя и элемента НЕ, выход повторителя соединен с первыми входами элементов И первой группы, с синхровходом первого счетчика, выходы которого соединены соответственно с входами первого дешифратора и первого селектора, выход элемента НЕ соединен с первыми входами элементов ,И второй группы, с синхровходом второго счетчика, выходы которого соединены соответственно с входами второго дешифратора и второго селектора выходы первого дешифратора соединены соответственно со вторыми входами первого, второго, третьего и четвер того элементов И первой группы, прямой и инверсный выходы первого селектора соединены соответственно со вторыми входами пятого и шестого элементов И первой группы, выходы второго дешифратора соединены соответственно со вторыми входами первого, второго, третьего, четвертого элементов И второй группы, прямой и инверсный выходы второго селектора соединены соответственно.со вто рыми входами пятого и шестого элемен :тов И второй группы, выходы элементов И первой и второй групп являются выходами устройства 21. Известное устройство вырабатывает BoqeMb фаз синхросигналов в течение одного Т . Сдвиг между синхросигналами равен нулю. Нечетные синхросигналы, вырабатываемые этим устройством соответствуют синхросигналам, выраба тываемым устройством l J. Недостатком указанного устройства является невозможность управления синхросигналами, которое необходимо для ускорения процесса наладки вычис лительной системы. При наладке необходимо, чтобы синхросигналы вырабаты вались в различных режимах: автоматическом, тактовом, импульсном. При автоматическом режиме синхросигналы вырабатываются непрерывно, а при тактовом режиме - поочередно, такт за тактом. При импульсном режим синхросигналы вырабатываются поочередно в пределах машинного такта. При выполнении команды в вычислительной системе задействовано боль шое количество аппаратуры в виде последовательно включенньЕС регистров с комбинационной схемой на входе и команда выполняется за. один или несколько машинньк тактов последовательно или параллельно. Определить место неисправности ап паратуры при выполнении команды слож но, так как нарушение информации при выполнении команды может быть в любой из параллельных цепей или на любом этапе выполнения. Индикация регистров на инженерном пульте при авт матическом режиме работы вычислитель ной системы отображает только резуль тат выполнения команды. . Диагностический режим работы вш.числительной системы для выполнения процедуры Диагноз,. т.е. поиск неисправной аппаратуры, требует обяза974тельно часть исправной аппаратуры, без которой невозможно выполнить данную процеду1ру, например ввод диагностических данных в вычислительную систему, управление этим вводом и т.д., наладка которого осуществляется с помощью режимов Шаг и Такт. Устройство fl позволяет в режиме Шаг вьфабатывать поочередно синхросигналы, что соответствует переменному периоду следования нечетных синхросигналов устройства 2 J. Для выработки синхросигнала необходимо выполнение следующего условия Ту, где длительность сигнала управления выработки синхросигнала} Т - длительность синхросигнала.Сиг-. нал управления формируется в проме- i жутке между соседними синхросигналами. . Устройство 2} вырабатывает восемь синхросигналов в течение одного Тд. Сдвиг между синхросигналами равен нулю. Таким образом, использовать данное управление выработкой синхро- сигналов в устройстве 2 невозможно. Цель изобретения - .расширение функциональных возможностей устройства за счет обеспечения переменного периода синхросигналов в нечетные и четные такты работы устройства. Поставленная цель достигается тем, что в устройство для синхронизации вычислительной системы, сфдержащее задающий генератор, группу элементов задержки ,. группу блоков вьфаботки син- , хросигналов, причем вькод задающего генератора соединен с входами элементов задержки группы с первого по п-и (где п-число каналов вычислительной системы), выходы которых соединены соответственно с синхровходами блоков вьфаботки синхросигналов, каждый из которых содержит два счетчика, два селектора, два дешифратора, две группы элементов И, первый элемент задержки, первый элемент НЕ, причем в каждом блоке вьфаботки синхросигналов синхровход блока соединен с входом первого элемента НЕ и с входом первого элемента задержки, вьосод которого соединен с первыми входа1 1И элементов И первой группы и с синхровходом первого счетчика, прямой выход первого разряда которого соединен .с первым входом первого .дешифратора и с первым входом первой группы входов первого селектора, второй вход первой группы входов которого соединен с прямым выходом второго разряда первого счетчика и со вторым входом первого дешифратора, третий вход которого соединен с инверсным выходом первого разряда первого счетчика, с первым входом второй группы входов первого селектора, второй вхо второй группы входов которого соеди.нен с инверсным выходом второго разряда первого счетчика и с четвертым входом первого дешифратора, выходы которого соединены соответственно со вторыми входами первого, второго, третьего и четвертого элементов И первой группы, прямой и инверсный выходы первого селектора соединены соответственно со вторыми входами пятого и шестого элементов И первой группы, выход первого элемента НЕ соединен с первыми вх,одами элементов И второй группы и с- синхровходом второго счетчика, прямой выход первого разряда которого соединен с пер вым входом второго дешифратора, с первым входом первой группы входов вт рого селектора, второй вход первой группы входов которого соединен с прямым вькодом второго разряда второго счетчика и со вторым входом второго дешифратора, третий вход которого соединен с инверсным выходом первого разряда второго счетчика и с первым входом второй группы входов второго селектора, второй вход второй группы входов которого соединен с инверсным выходом второго разряда второго счетчика и с четвертым входо второго дешифратора, выходы которого соединены соответственно с вторыми входами первого, второго, третьего, и четвертого элементов И второй груп пы, прямой IJ инверсный вьпсоды второго селектора соединены соответственно со вторыми входами пятого и шестого элементов И второй группы выходы элементов И первой и второй груп каждого блока выработки синхросигнало являются соответственно первой и вто рой группами выходов устройства,введен блок вьфаботки сигналов начальной установки, блок переключателей, блок формирования сигналов управления режимами, элементы задержки груп пы с ( п +1) -го по ()-й, ив каждый блок выработки синхросигналов введены второй и третий элементы НЕ второй элемент задержки, третий сче чик, первый, второй и третий элементы И-НЕ, первый и второй элементы И, третий и четвертый селекторы, первый, второй, третий и четвертый регистры сдвига, первый, второй, третий и четвертый триггеры, первый и второй узлы управления,, первый и второй узлы сравнения, третья и четвертая группы элементов И, причем выход задающего генератора соединен с входом блока выработки сигналов начальной установки, выход которого сбег динен соответственно с входами элементов задержки группы с (п +t)-ro по (2п+1)-й, выходы элементов задержки группы (п -«-О-го по 2 п -и соединены соответственно с установочными входами блоков вьфаботки синхросигналов с первого по п-и выходы блока переключателей соединены соответственно с группой информационных входов блока формирования сигналов управления режимами, синхровход которого соединен с выходом (2п -fD-ro элемента задержки группы, первый выход блока формирования сигналов управления режимами соединен с первыми управляющими входами блоков вьфаботки синхросигналов, вторые управляющие входы которых соединены со вторым выходом -блока формирования сигналов управления резкимами, третий выход которого соединен с третьими управляющими входами блоков вьфаботки синхросигналов, при этом в каждом блоке вьфаботки синхросигналов выход первого элемента задержки соели нен с синхровходом первого регистра сдвига, с синхровходом первого триггера, с синхровходом второго триггера, с синхровходом второго регистра сдвига, с синхровходом первого, узла управления, с первыми входами элементов И третьей группы,с первым входом первого элемента И-НЕ, второй вход которого соединен с установочным входом блока, с первым входом второго элемента И-НЕ, второй йход которого соединен с выходом первого элемента Н.Е, с синхровходом третьего регистра сдвига, с синхровходом четвертого триггера, с синхровходом четвертого регистра сдвига, с синхровходом второго узла управления, с первыми входами элементов И четвертой группы, вторые входы которых соединены с выходом второго узла управления, с управляющим входом третьего регистра.

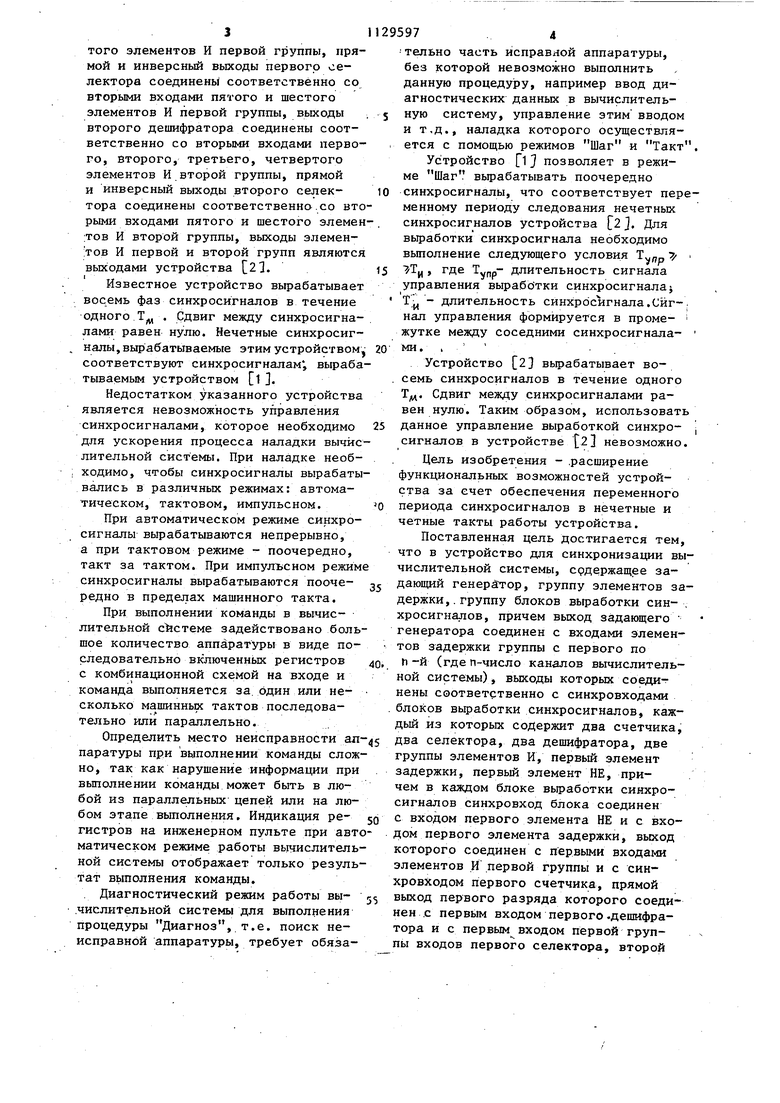

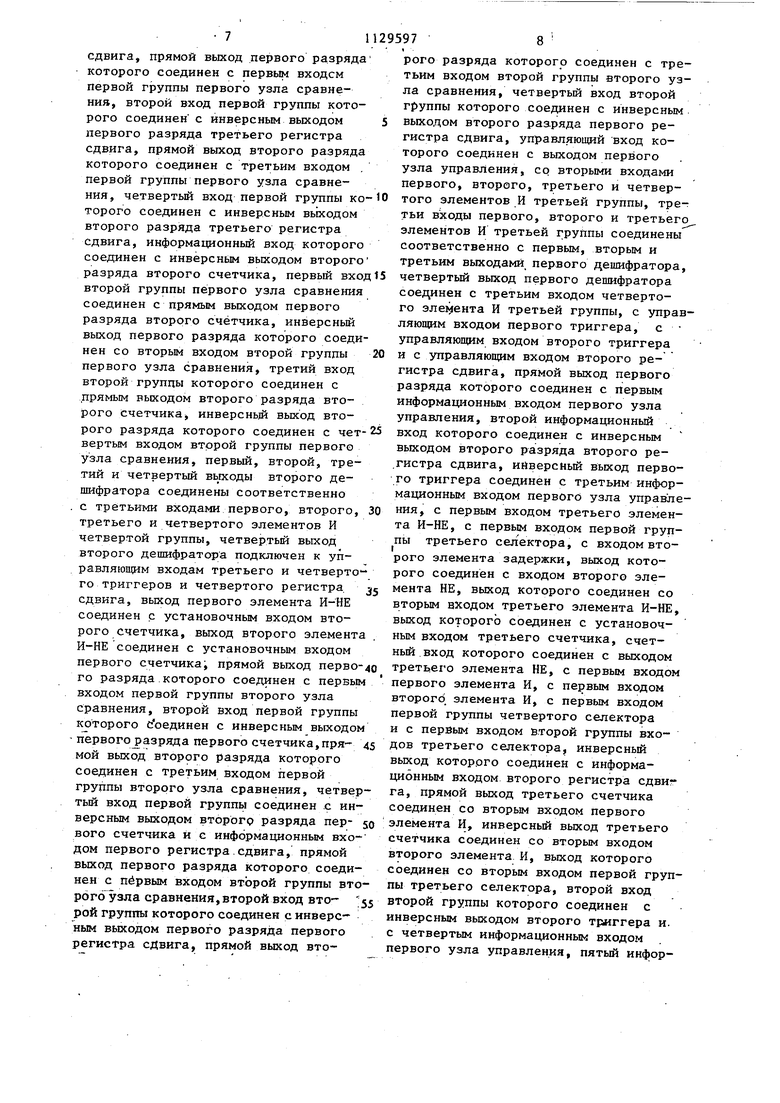

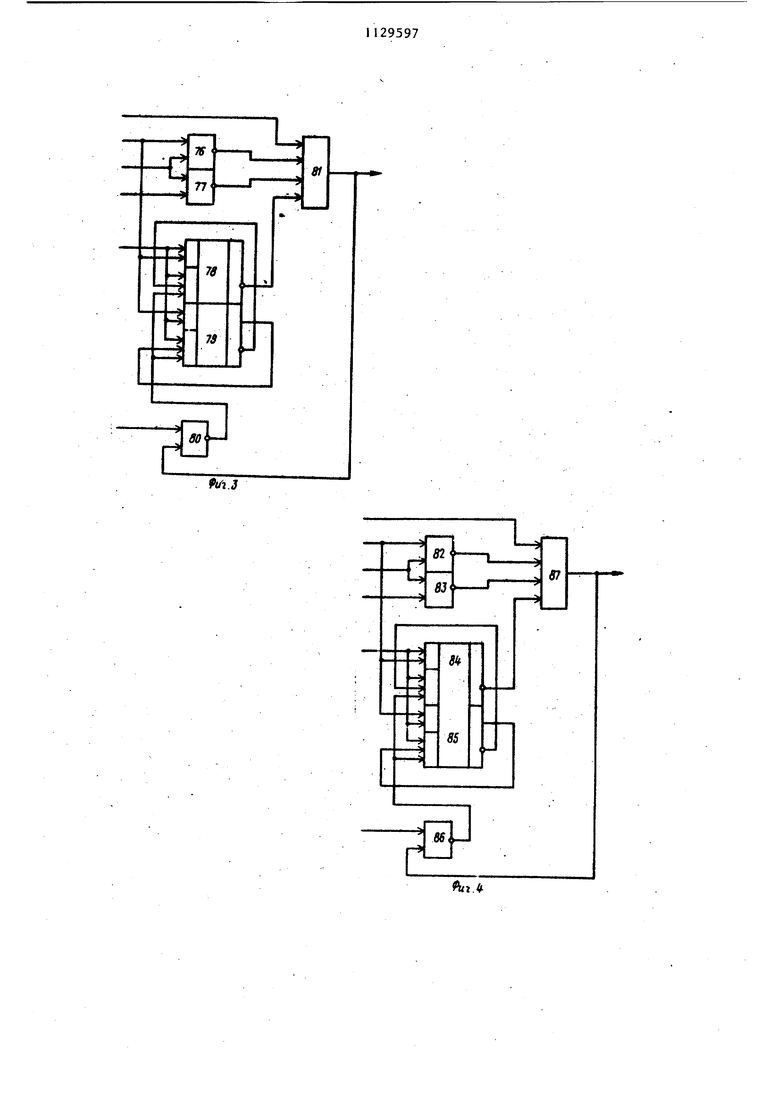

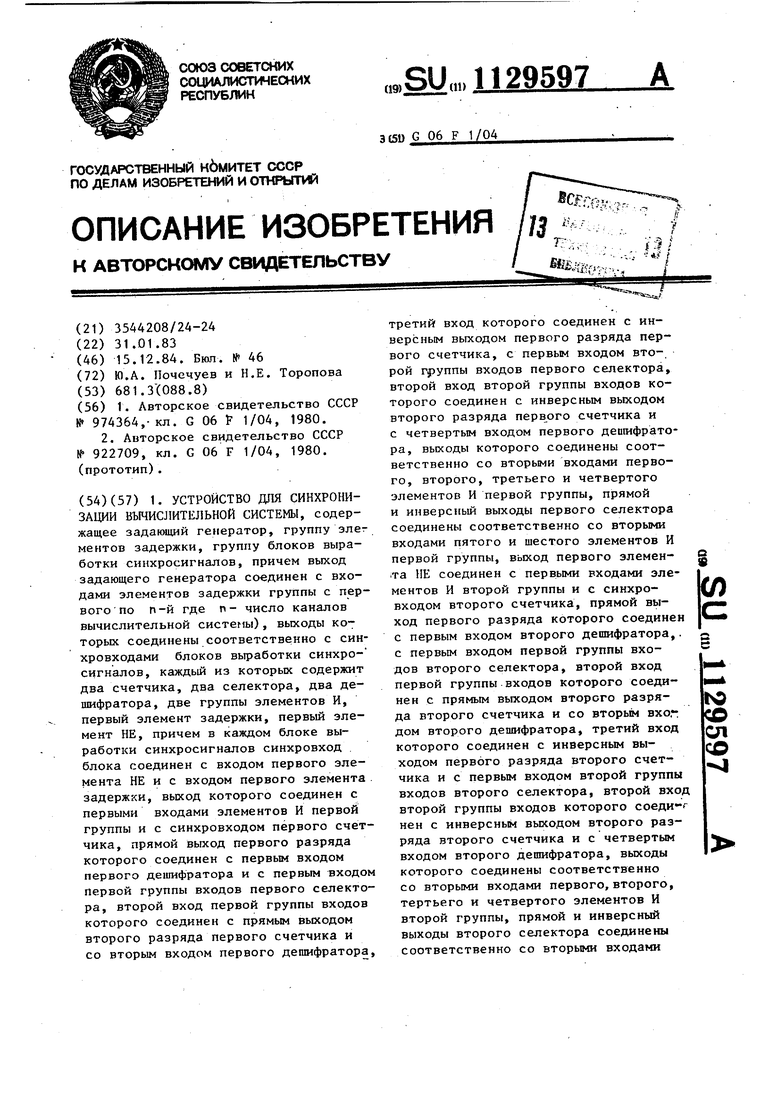

сдвига, прямой вькод первого разряда которого соединен с первым входом первой Г1зуппы первого узла сравнения, второй вход первой группы которого соединен с инверсным выходом первого разряда третьего регистра сдвига, прямой выход второго разряда которого соединен с третьим входом . первой группы первого узла сравнения, четвертый вход первой группы которого соединен с инверсным вь ходом второго разряда третьего регистра сдвига, информационный вход которого соединен с инверсным выходом второго разряда второго счетчика, первый вход второй группы первого узла сравнения соединен с прямым выходом первого разряда второго счётчика, инверсньй выход первого разряда которого соединен со вторым входом второй группы первого узла сравнения, третий вход второй группы которого соединен с прямым выходом второго разряда второго счетчика, инверсный выход второго разряда которого соединен с четвертым входом второй группы первого узла сравнения, первый, второй, третий и четвертый вьгходы второго депифратора соединены соответственно с третьими входами первого, второго, третьего и четвертого элементов И четвертой группы, четвертьм выход второго дешифратора подключен к управляющим входам третьего и четверто го триггеров и четвертого регистра. сдвига, выход первого элемента И-НЕ соединен с установочным входом второго счетчика, выход второго элемента И-НЕ соединен с установочным входом первого cчeтчикaj прямой выход первого разряда.которого соединен с первым входом первой группы второго узла сравнения, второй вход первой группы которого Лединен с инверсным выходом первого азряда первого счетчика,прямой выход второго разряда которого соединен с третьим входом первой группы второго узла сравнения, четвертый вход первой группы соединен с инверсным выходом второго разряда первого счетчика и с информационным входом первого регистра.сдвига, прямой выход первого разряда которого соединен с первым входом второй группы второго узла сравнения, второй вход второй группы которого соединен с инверсным выходом первого разряда первого регистра сдвига, прямой выход второго разряда которого соединен с третьим входом второй группы второго узла сравнения, четвертьй вход второй группы которого соединен с инверсным выходом второго рааряда первого регистра сдвига, управляющий вход которого соединен с выходом первого узла управления, со вторыми входами первого, второго, третьего и четвертого элементов И третьей группы, третьи входы первого, второго и третьего элементов И третьей группы соединены соответственно с первым, вторым и третьим выходамй первого дешифратора четвертый выход первого дешифратора соединен с третьим входом четвертого эле1; ента И третьей группы, с управляющим входом первого триггера, с управляющим входом второго триггера и с управляющим входом второго регистра сдвига, прямой выход первого разряда которого соединен с первым информационным входом первого узла управления, второй информационный вход которого соединен с инверсным выходом второго разряда второго ре.гистра сдвига, ийверсньй выход первого триггера соединен с третьим информационным входом первого узла управления, с первым входом третьего элемента И-НЕ, с первым входом первой группы третьего селектора, с входом второго элемента задержки, выход которого соединен с входом второго элемента НЕ, выход которого соединен со вторым входом третьего элемента И-НЕ, выход которого соединен с установочным входом третьего счетчика, счетньй вход которого соединен с выходом третьего элемента НЕ, с первым входом первого элемента И, с первым входом второго, элемента И, с первым входом первой группы четвертого селектора и с первым входом в.торой группы входов третьего селектора, инверсный выход которого соединен с информационным входом второго регистра сдвига, прямой выход третьего счетчика соединен со вторым входом первого элемента И, инверсный выход третьего счетчика соединен со вторым входом второго элемента И, выход которого соединен со вторым входом первой группы третьего селектора, второй вход второй группы которого соединен с инверсным выходом второго триггера и. с четвертым информационным входом первого узла управления, пятый информационный вход которого соединен с вы ходом второго узла сравнения, первый управляющий вход каждого блока вьфаботки синхросигналов соединен с информационным входом первого триггера с информационным входом третьего триг гера, инверсный выход которого соединен с первым входом второй группы четвертого селектора, второй вход первой группы которого соединен с инверсным выходом четвертого триггера первый информационньй вход второго узла управления соединен с прямым выходом первого разряда четвертого регистра сдвига, инверсный выход второго разряда которого соединен со вторым информационным входом второго узла управления, третий, четвертьй и пятый информационные входы которого соединены соответственно с инверс ным выходом третьего триггера, инверсным выходом четвертого триггера и с выходом первого узла сравнения, выход пер-вого элемента И соединен со вторым входом второй группы четверто го селектора, инверсньо выход которо го соединен с информационным входом четвертого регистра сдвига, второй управляющий вход каждого блока выработки синхросигналов соединен с информационным входом второго триггера и с информационным входом четвертого триггера, третий управляющий вход каждого блока выработки синхросигналов соединен с входом третьего эле.мента НЕ, выходы элементов И третьей и четвертой групп каждого блока вьфа ботки синхросигналов являются соотве ственно третьей и четвертой группой .выходов устройства, при этом каждый узел управления содержит три элемен та И-НЕ, два селектора, элемент И, причем в узле управления первьй инфо мационный вход соединен с первым вхо дом первого элемента И-НЕ,с первым входом первой группы входов первого селектора и с первым входом первой группы второго селектора, прямой выход которого соединен с первым вхо дом второй группы входов второго селектора, второй вход второй группы которого соединен с первым входом второй группы первого селектора и с ,выходом второго элемента И-НЕ, первы вход которого является синхровходом узла, второй информационный вход которого соединен с первым входом третьего элемента И-НЕ, выход которого соединен с первым входом элемента И, выход которого соединен со вторым входом второго элемента И-НЕ и является выходом узла, третий информационный вход которого соединен со вторым входом первой группы первого селектора, со вторым входом второй группы первого селектора, со вторым входом первой группы второго селектора и с .третьим входом второй группы второго селектора, инверсный выход которого соединен с третьим входом второй группы первого селектора, инверсный выход которого соединен со .вторым входом элемента И, третий.вход которого соединен с выходом первого элемента И-НЕ, второй вход которого соединен со вторым входом третьего элемента И-НЕ и является четвертым информационным входом узла, пятый информационный вход которого соединен с четвертым входом элемента И. Кроме того, каждый узел сравнения содержит пять элементов И-НЕ, причем первый вход первой группы входов узла соединен с первым входом первого элемента И-НЕ, с первым входом второго элемента И-НЕ, выход которого соединен с первым входом третьего элемента Й-НЕ, второй вход которого соединен с выходом четвертого элемента И-НЕ, первый вход которого соединен с первым входом Пятого,элемента И-НЕ и является вторым входом первой группы входов узла, третий вход первой группы входов которого соединен со вторым входом первого элемента И-НЕ, со вторым входом пятого элемента И-НЕ, выход которого соединен с третьим входом третьего элемента И-НЕ, выход которого является выходом узла, четвертый вход . первой группы входов которого соединен со вторым входом четвертого эле-, мента И-НЕ, со вторым входом второго Элемента И-НЕ, первый вход второй группы входов узла соединен с третьим входом второго элемента И-НЕ, с тре- тьим входом первого элемента И-НЕ, выход которого соединен с четвёртым входов третьего элемента И-НЕ, второй вход второй группы входов кото- рого соединен с третьим входом четвертого элемента И-НЕ, третий вход второй группы входов которого соединен с четвертым входом первого элемента И-НЕ, с четвертым входом пятого элемента И-НЕ, четвертый вход второйГ группы входов узла соединен с четвертым входом четвертого элемента . И-НЕ, с четвертым входом второго элемента И-НЕ. Блок формирования сигналов управления режимами содержит два триггера, регистр сдвига и элемент И, причем информационный вход триггера, информационный вход второго триггера, информационный вход регистра сдвига : являются соответственно первым, вторым, третьим входами группы информационных входов блока, синхровход которого соединен, с синхровходрм регистра сдвига, с синхровходом второго триггера и с синхровходом первого триггера, выход которого соединен первым выходом блока, второй вьк-од которого соединен с выходом второго / триггера, прямой выход первого разря- да регистра сдвига соединен с первым входом элемента И, второй вход которого соединен с инверсным выходом второго разряда регистра сдвига, .выход элемента И соединен с третьим выходом блока. Блок выработки сигналов начальной установки содержит два счетчика, эле мент И, причем вход блока соединен с синхровходом первого счетчика, с синхровходом второго счетчика и с пе вым входом первого элемента И, второ вход которого соединен с инверсным выходом первого разряда первого счет чика, прямой выход первого разряда которого соединен с управляющим входом второго счетчика, йнверсньй выход первого разряда которого соединен с третьим входом элемента И, выход которого соединен с выходом блока. FJa фиг. 1 представлена структурная схема устройства; на фиг. 2 схема блока выработки синхросигналов на фиг. 3 - схема первого узла управ ления; на фиг, 4 - схема второго узла управления; на фиг. 5 - схема первого узла сравнения; на фиг. 6 схема второго узла сравнения; на фиг. 7 схема блока формирования сигналов управления режимами; на фиг. 8 - схема блока выработки сигналов начальной установки; на фиг. 9 временная диаграмма синхросигналов, вырабатываемая блоком вьфаботки синхросигналов. Устройство содержит задающий гене ратор 1, элементы 2 задержки, блоки 3 выработки синхросигналов, -.блок 4 выработки сигналов начальной установки, блок 5 переключателей, блок 6 формирования сигналов управления режимами, первые управляющие входы 7 блоков выработки синхросигналов, вторые управляющие входы 8 блоков выработки синхросигналов, третьи управляющие входы 9 блоков выработки синхросигналов, синхровходы 10 блоков выработки синхросигналов, установочные входы 11 блоков выработки синхросигналов, синхровход 12 блока формирования сигналов зшравления режимами, вход 13 блока выработки сигналов начальной установки, первые группы 14, вторые группы 15, третьи группы 16, четвертые группы 17 выходовблоков 3 вьфаботки синхросигналов, группа 18 информационных входов блока формирования сигналов управления режимами. группы 19 вьЬсодов блока выработки сигналов -начальной установки, выход 20 задающего генератора. Блок 3 выработки синхросигналов содержит элемент НЕ 21, элемент заДержки 22, элемент И-НЕ 23, элемент И-НЕ 24, счетчик 25, регистр 26 сдвига, триггер 27, триггер 28, регистр 29 сдвига, счетчик 30, регистр 31 сдвига, триггер 32, триггер 33, регистр 34 сдвига, дешифратор 35, селектор 36, узел 37 управления, узел 38 управления, селектор 39, узел 40, сравнения, узел 41 сравнения, дешифратор 42, элемент НЕ 43, элемент задержки 44, счетчик 45, элемент НЕ 46, элемент И-НЕ 47, элемент И 48, элемент И 49, селектор 50, селектор 51, группа элементов И 52, группа элементов И 53, группа элементов 54, группа элементов И 55. Выходы 56-61 элементов И 52, выходы 62-67 элементов И 53, выходы 68-71 элементов 54 выходы 72-75 элементов И 55. Узел 37 управления (фиг. 3) содержит элементы И-НЕ 76 и 77,. селекторы 78 и 79, элемент И-НЕ 80. . Узел 38 управления (фиг. 4) содержит элементы и-НЕ 82 и 83, селекторы 84 и 85, элемент И-НЕ 86, элемент И 87. Узел 40 (фиг. 5) содержит элементы И-НЕ 88-92. Узел 41 (фиг. 6) содержит элементы И-НЕ 93-97. Блок 6 (фиг. 7) содержит триггеры 98 и 99, регистр 100 сдвига, элемент И 101. Блок 4 (фиг. 8) содержит счетчики 102 и 103, элемент И 104. Устройствоработает следующим образом. Задающий генератор 1 вырабатывает .исходную последовательность, поступающую через элементы 2 задержки, служащие для выравнивания синхросигналов на входы 10 блоков 3 выработки сии хросигналов. Исходная последователь ность синхросигналов поступает также на вход 13 блока 4 выработки сигналов начальной установки, счетчики 102 и 103 которого делят исходную последовательность соответственно на два и на четыре. Элемент И 104 выработки сигналов начальной установки вьфабатывает сигнал начальной установ ки, которые поступают через элементы 2 задержки, служащие также для зыравнивания сигйалов начальной установ ки, на вход 11 блоков выработки синхросигналов. Сигнал ы начальной уста-новки в блоках выработки синхросигналов через элементы И-НЕ 23 и 24 посту на входы начальной установки соответственно счетчиков 30 и 25 блоков выработки синхросигналов. Выравни вание сигналов начальной установки осуществляется для обеспечения одно- временной установки в исходное состоя ние счетчиков 25 и 30 всех блоков выработки синхросигналов. Исходная последовательность поступает в блоках выработки синхросигналов через первый элемент 22 и первый элемент НЕ 21 на синхровходы счетчиков соответствен но 25 и 30. Элемент НЕ 21 служит для инверсии исходной последовательности Элемент 22 служит для временного вы- равнивания исходной последовательности внутри блоков- выработки синхросигналов. Счетчики 25 и 30 делят исходную последовательность на четьфе, каждый из которых позволяет получить четьфе сигнала длительностью Тдд(4), где Т - длительность мапшнного такта. Сигналы со счетчиков поступают на входы дешифраторов соответственно 35 и 42. Инверсные выходы вторых разрядов счетчиков 25 и 30 поступают на информационные входы регистров сдвига соответственно 26 и 31, которые осу ществляют перепись информации счетчиков под управлением управляющих сигналов, которые поступают от узлов управления, соответственно 37 и 38. Узлы 37 и 38 управления управляют пеП714 реписью информации регистров 26 и 31 сдвига соответственно, .под управлением сигналов поступающих на управляющие входы 7-9 блоков 3 вьфаботки синхросигналов от блоков 6 формирования сигналов управления режимами, который вырабатывает управляющие сигналы в зависимости от положения переключателей, обеспечивающих выбор режима Автомат, Шаг, Такт Пуск. Сигналы от переключателей в. блоке 6 формирования сигналов управления режимами синхронизируются триггерами 98 и 99, регистром 100 сдвига и поступают на входы 7-9 блоков 3 выработки синхросигналов соответственно. В блоках 3 вьфаботки синхросигнал лов сигналы Шаг(Авт., Такт) Авт, Пуск синхронизируются триггерами 27, 28, 32 и 33, регистрами 25 и34. сдвига. Синхронизация осуществляется для одновременной установки всех блоков вьфаботки синхросигналов в заданный режим, причем триггеры 27 и 28, регистр 29 сдвига синхронизируются в .нечетные такты работы устройства, а триггеры 32 и 33, регистр 34 сдвига - в четные. Регистры 29 и 34 осуществляют выработку управляющих импульсов длительностьют машин- ньй такт. Элемент 43.НЕ осуществляет инвертирование сигнала ПУСК, nor ступающего на вход счетчика 45, который делит исходную последовательность на два. Счетчик 45 устанавливается в исходное состояние сигналом Шаг, поступающим через элемент 44, элемент НЕ 46, элемент И-НЕ 47 на установочный вход счетчика 45. Элементы 44, 46, 47 формируют импульс .для установки счетчика 45, элементы 48 и 49 осуществляют формирование сигналов Пуск для нечетных и четных тактов работы устройства в режиме Шаг, Селекторы 50 и 51 служат для вьфабот ки сигналов Пуск в нечетные и четные такты работы устройства, причем необходимо разделение сигналов Пуск для режимов, Такт и Шаг в нечетные и четные такты работы устройства:. В режиме Такт должны вырабатываться все синхросигналы на выходах 68, 72, 69, 73, 70, 74, 71, 75(фиг.10) прследоват ельно, после нажатия кнопки Пуск. В режиме Шаг должны вырабатываться синхросигналы поочередно от каждого нажатия кнопки Пуск, приче м сначала нечетный импульс на 15 выходе 68, затем четный на выходе 7 и т.д. Селектор 50 осуществляет выработку сигнала Пуск для нечетньк синхроимпульсов в режимах Такт и Шаг. Селектор 51 осуществляет выработку сигнала- Пуск для четных с хроимпульсов в режимах Такт и Ша Узлы управления 37 и 38 осуществ |ют выработку управляю их сигналов с ответственно в нечетные и четные та ты оабаты устройства. Рассмотрим работу узлов управления на примере первого узла управления (фиг. 3). В режиме Так- селекторы 78 и 79 закрыты, на выходе селектора 78 сигнал равен единице, поступающий на вход элемента И 81. В режиме Автомат на выходе элемента 81 идет разрешение и регистр 26 сдвига блока вьфаботки синхросигналов осуществляет перепись информации счетчика. Выходы счетчика 23 и регистра 26 сдвига сравниваются в узле сравнения . блока 3 и в каждые моменты времени Тд, (4) происходит сравнение состояний счетчика и регистра, следователь но, осуществляется выработка непрерывных нечетных последовательностей на выходах 56-61 блоков вьфаботки синхросигналов. Аналогично осуществл ется выработка непрерывных четных по следовательностей на выходах 62-67 блоков выработки синхросигналов. В режиме Такт происходит блокировка управляющего входа регистров 26 и 3 сдвига. При появлении сигнала Пуск в режиме Такт на входе 9 блоков выработки синхросигналов, который проходит через селекторы 50 и 51 блс ков 3 вьфаботки синхросигналов и эти селекторы управляют регистрами лоответственно 29 и 34, которые в течение времени Т разрешают прохождение синхроимпульсов, это разрешение поступает соответственно на входы уз лов 37 и 38 управления, в которых через элементы 76, 77, 82, 83 проходят разрешающие сигналы на вход элемента 81 (87) И. При установке режима Шаг узлы 37 и 38 управления блокируют перепись информации регистрами 26 и 31 сдвига. При появлении сигнала Пуск в режиме Шаг Этот сигнал поочередно дает разрешение для прохождения синхроимпульса то в нечетных, то в четных тактах работы устройства на 97;16 выходах селекторов 50 и 51 соответ- ственно. Счетчик 45 считает нажатия кнопки Пуск. При нечетном нажатии кнопки Пуск он разрешает прохождение сигнала Пуск в селекторе 50, при четном нажатии - в селекторе 51. Узлы управления 37 и 38 поочередно дают разрешение на прохождение синхроимпульса на время Тд,(4), т.е. в каждую четверть такта .поочередно появляется разрешение, что разрешает выработку синхросигналов поочередно в зависимости от сигнала Пуск. На выходах 68,72,69,73,70,74,71, 75 поочередно вырабатываются синхросигналы после каждого нажатия кнопки Пуск в режиме Шаг. В режиме Автомат синхросигналы на выходах 62,72,69,73,70,74,71,75 вьфабатываются непрерывно, как и неуправляемые синхросигналы на выходах 56,62,57,63,58,64,59,65,60,61,66,67 (фиг. 10). Введение режимов Такт и Шаг устройства синхронизации вычислительной системы позволяет вьшолнять команды,обрабатывающиеся в вычислительной системе, поэтапно.- С помощью данных режимов работы устройства синхронизации, которое определяет временную диаграмму работы ЭВМ, можно проследить выполнение команды от момента начала выполнения до момента окончания. Каждый этап выполнения отображает-. ся на инженерном пульте вычислительной системы в виде индикации регистров. В режиме Такт команда выполняется с дискретом- одного машинного такта и с частотой управляемой one-, ратором или управляющим сигналом в режиме Диагноз. В режиме Шаг команда выполняется с дискретом следования одного синхросигнала устройства синхронизации вычислительной системы и с частотой, определяемой оператором, или управляющим сигналом в режиме Диагноз. Предложенное устройство позволяет использовать те же цепи вьфаботки синхросигналов, .что и в автоматическом режиме и сохраняет параметры синхросигналов автоматического режима. Таким образом, режимы работы Такт и Шаг устройства сцнхронизаии вычислительной системы предназнаены как наладочные и как , позволяю1цие выполнить диагностические процедуры в ЭВМ. Применение дднных режимов работы вычислительной системы позволяет значительно- сократить время и облег чить процедуру нападки вычислительной системы на заводе - изготовител и в вычислительных центрах при эксплуатации. 718 Режим Такт и Шаг могут быть использованы для построения ЭВМ, в которых применяется синхронный принцип работы и имеется устройство выработки синхросигналов,определяющее временную диаграмму обработки команд. Применение данных режимов работы в ЦВМ позволяет сократить процедуру поиска неисправной аппаратуры и уменьшить экономические затраты на обслуживание ЭВМ

Iff. 15,16.17

73

«7

63

MffL

I -W в

.5

18

12

13

D ,99

8

7l)f 9

Ui.l

19

WiiФиг.8

TM

15(65}

.

B 67

Риг.9

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU974364A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU922709A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип). | |||

Авторы

Даты

1984-12-15—Публикация

1983-01-31—Подача