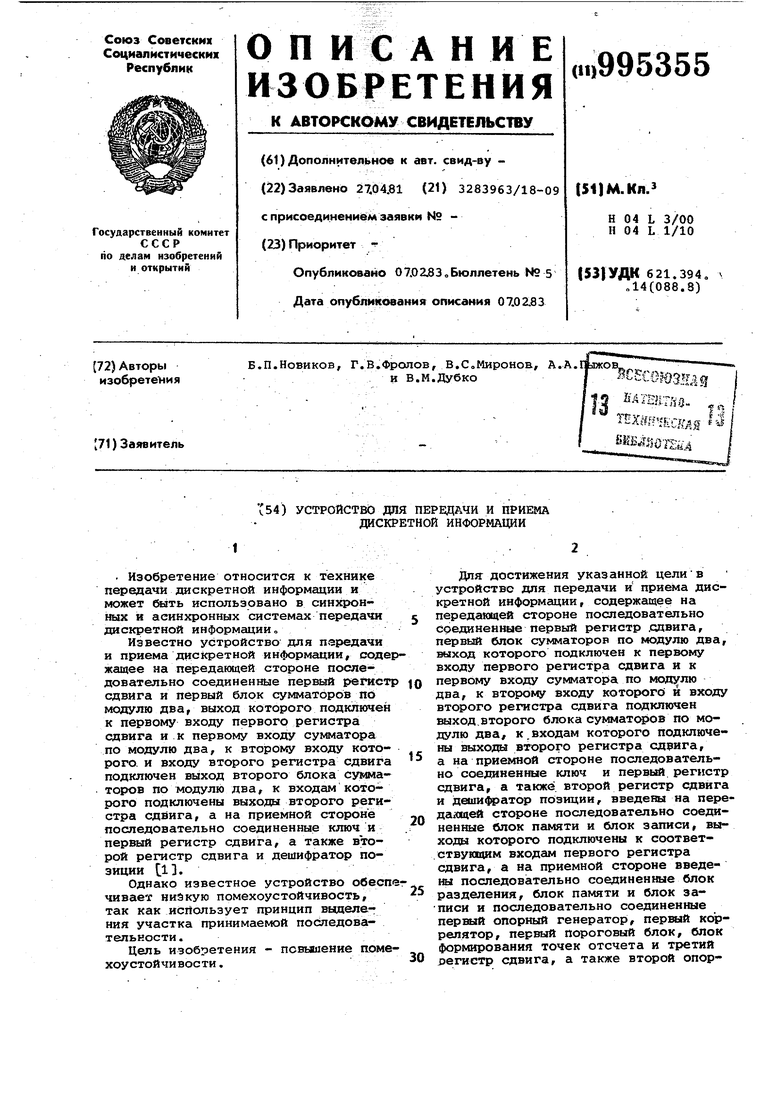

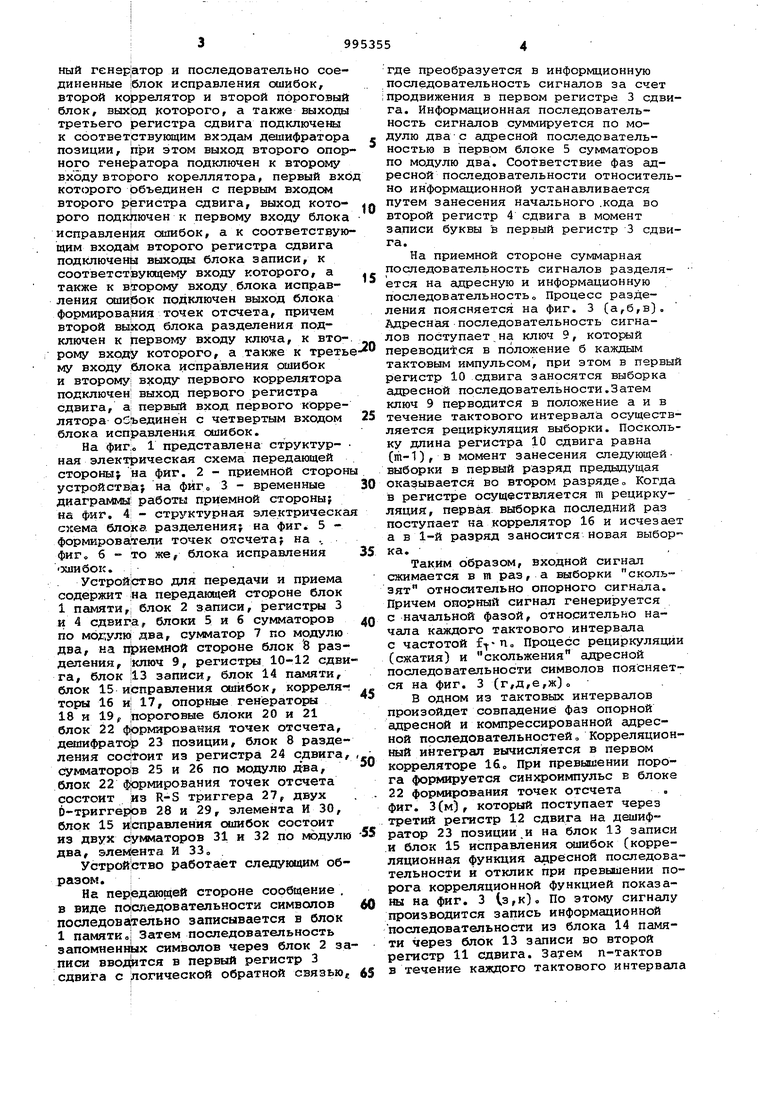

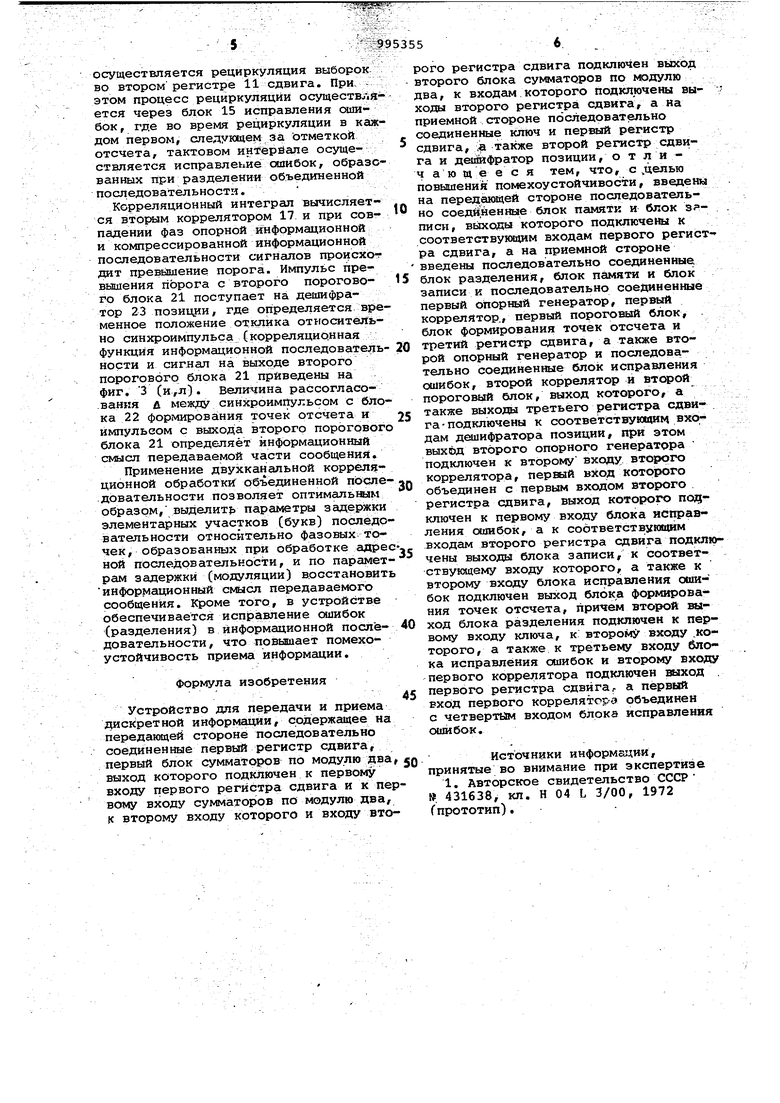

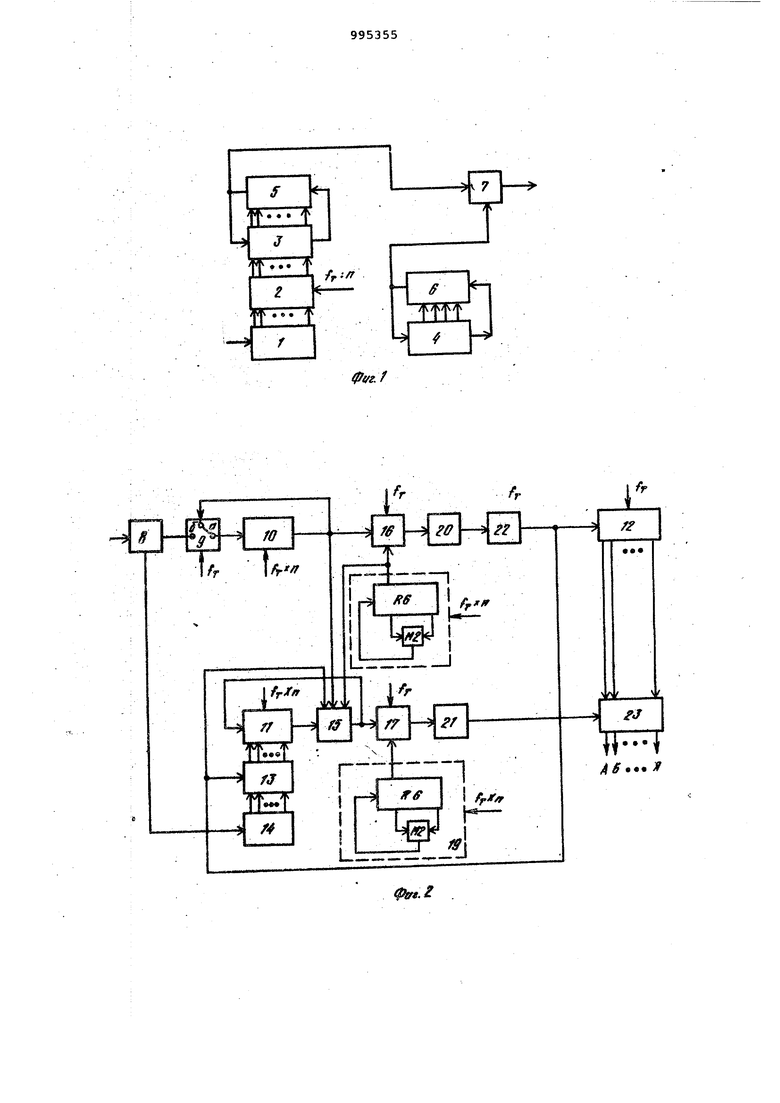

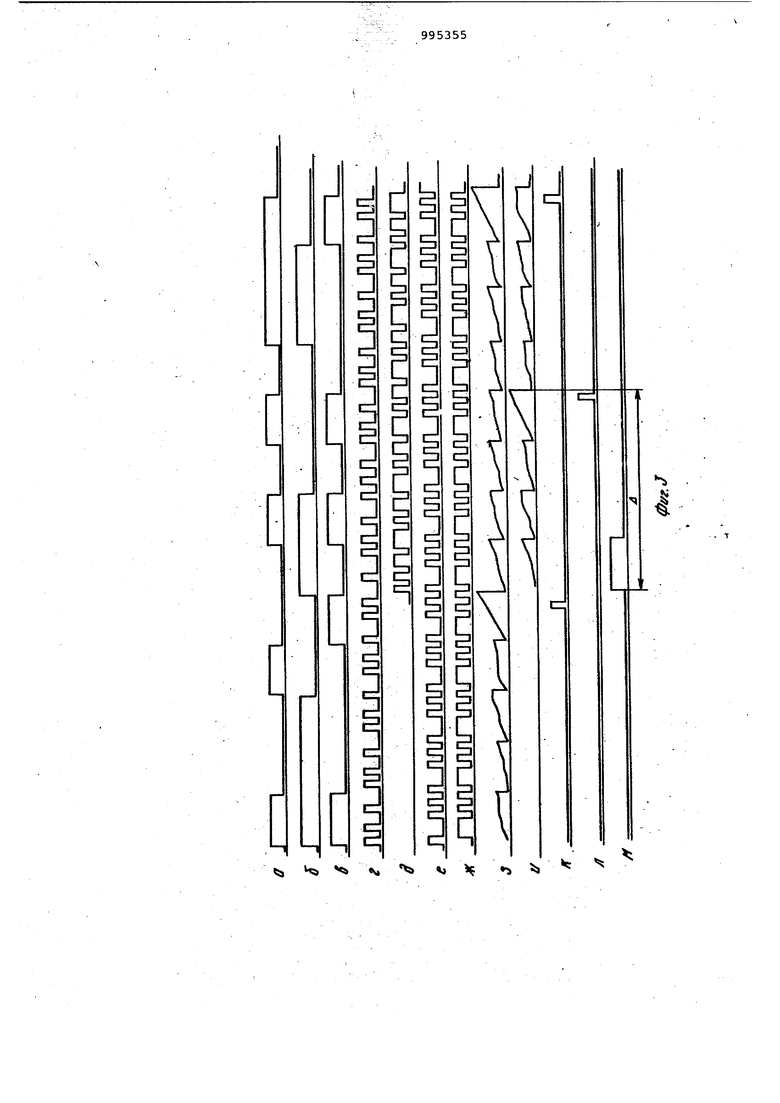

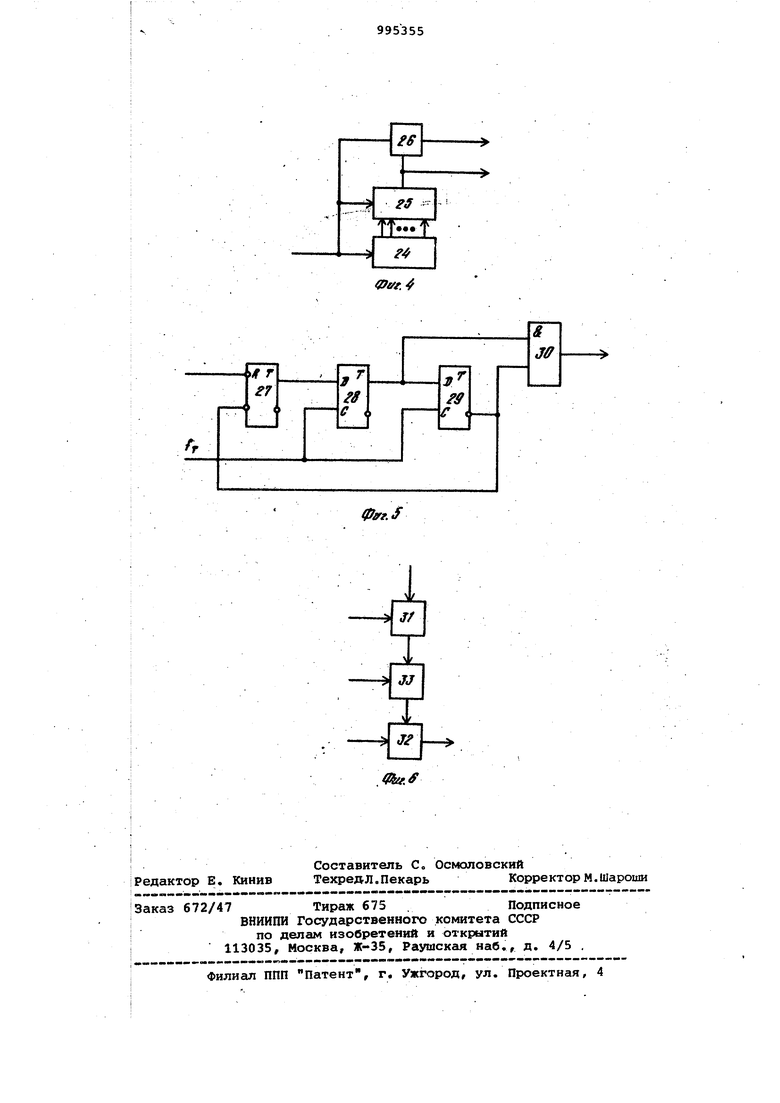

Изобретение относится к технике передачи дискретной информации и может feiTb использовано в синхронных и асинхронных системах передачи дискретной информации„ Известно устройство для пзредачи и приема дискретной информации, сод жащее на передающей стороне последовательно соединенные первый регис сдвига и первый блок сумматоров по модулю два, выход которого подключе к первому входу первого регистра сдвига и к первому входу сумматора по модулю два, к второму входу кото рого, и входу второго регистра сдвиг подключен выход второго блока сумма торов по модулю два, к входам которого подключены выходы второго реги стра сдйига, а на приемной стороне последовательно соединенные ключ и первый регистр сдвига, а также второй регистр сдвига и дешифратор позиции 1. Однако известное устройство обес чивает ниЭкую помехоустойчивость, так как использует принцип вьщеления участка принимаемой последовательности . Цель изобретения - псвьвнение пом хоустойчивости. Для достижения указанной целив устройстве для передачи и приема дискретной информации, содержащее на передающей стороне последовательно соединенные первый регистр .сдвига, первый блок сумматоров по модулю два, выход которого подключен к первому входу первого регистра сдвига и к первому входу сумматора по модулю два, к второму входу которого и входу второго регистра сдвига подключен выход,второго блока сумматоров по модулю два, к.входам которого подключены выходы второго регистра сдвига, а на приемной стороне последовательно соединенные ключ и первый регистр сдвига, а также, второй регистр сэдвига и позиции, введены на переда оцей стороне последовательно соединенные блок памяти и блок записи, выходы которого подключены к соответствукщим входам первого регистра одвига, а на приемной стороне введены последовательно соединенгале блок разделения, блок памяти и блок записи и последовательно соединенные первый опорный генератор, первый коррелятор, первый пороговый блок, блок формирования точек отсчета и третий регистр сдвига, а также второй опорный генератор и последовательно сое диненные |блок исправления ошибок, второй коррелятор и второй пороговы блок, выход которого, а также выход третьего регистра сдвига подключены к соответствующим входам дешифратор позиции, при этом выход второго опо ного генератора подключен к второму входу второго кореллятора, первый вх которого объединен с первым входсм второго регистра сдвига, выход кото рого подключен к первому входу блок исправления сяпибок, а к соответству щим входам второго регистра сдвига подключены выходы блока записи, к соответст|вующему входу которого, а также к второму входу блока неправления ошиЬок подключен выход блока формирования точек отсчета, причем второй выход блока разделения подключен к рервому входу ключа, к вто рому входу которого, а также к треть му входу блока исправления ошибок и второму входу первого коррелятора подключен; выход первого регистра сдвига, а первый вход первого корре лятора объединен с четвертым входом блока исправления ошибок. На фиг;, 1 представлена структурная электрическая схема передающей cтopoны на фиг. 2 - приемной сторон устройства} на фйго 3 - временные диаграммы работы приемной стороны; на фиг. 4 - структурная электрическа схема блока paздeлeния на фиг. 5 формирова тели точек отсчета; на .. фиг б - то же, блока исправления эашбок. Устроимте во для передачи и приема содержит на передающей стороне блок 1 памяти,; блок 2 записи, регистры 3 и 4 сдвига, блоки 5 и 6 сумматоров по мохулвд два, сумматор 7 по модулю два, на фиемной стороне блок 8 разделения, 1КЛЮЧ 9, регистры 10-12 сдви га, блок ;13 записи, блок 14 памяти, блок 15 исправления ошибок, корреляг торы 16 и 17, опорные генераторы 18 и 19, пороговые блоки 20 и 21 блок 22 Армирования точек отсчета, дешифратф 23 позиции, блок 8 разделения состоит из регистрй 24 сдвига, сумматоров 25 и 26 по модулю два, блок 22 фрмирования точек отсчета состоит из R-S триггера 27, двух D-TpHrrept B 28 и 29, элемента И 30, блок 15 и|справления сшшбок сострит из двух сумматоров 31 и 32 по модулю два, элемента И 33, Устройство работает следующим образом. ; На пер ёдаюрчей стороне сообщение . в виде пйспедовательности символов последовфельно записывается в блок 1 памяти oi Затем последовательность 3anoMHeHi4ix символов через блок 2 за писи ввофтся в первый регистр 3 сдвига с логической обратной связью где преобразуется в информционную .последовательность сигналов за счет :продвижения в первом регистре 3 сдвига. Информационная последовательность сигналов суммируется по модулю дваС адресной последовательностью в первом блоке 5 сумматоров по модулю два. Соответствие фаз адресной последовательности относительно информационной устанавливается путем занесения начального .кода во второй регистр 4 сдвига в момент записи буквы в первый регистр 3 сдвига. На приемной стороне суммарная последовательность сигналов разделяется на адресную и информационную последовательность о Процесс разделения поясняется на фиг. 3 (а,б,в). Адресная последовательность сигналов поступает,на ключ 9, которлй переводится в положение б каждым тактовым импульсом, при этом в первый регистр 10 сдвига заносятся выборка адресной последовательности.Затем ключ 9 перводится в положение айв течение тактового интервала осуществляется рециркуляция выборки. Поскольку длина регистра 10 сдвига равна (т-1), в момент занесения следующейвыборки в первый разряд предыдущая оказывается во разряде о Когда в регистре осуществляется m рециркуляция, первая выборка последний раз поступает на коррелятор 16 и исчезает а в 1-й разряд заносится новая выборка. Таким образом, входной сигнал сжимается в га раз, а выборки скользят относительно опорного сигнала. Причем опорный сигнал генерируется с начальной фазой, относительно начала каждого тактового интервала с частотой -j По Процесс рециркуляции (сжатия) и скольжения адресной последовательности символов поясняется на фиг. 3 (г,д,е,ж)о В одном из тактовых интервалов произойдет совпадение фаз опорной адресной и компрессированной адресной последовательностей. Корреляционный интеграл вычисляется в первом корреляторе 16о При превышении порога формируется синхроимпульс в блоке 22 формирования точек отсчета . фиг. 3(м), который поступает через третий регистр 12 сдвига на дешифратор 23 позиции.и на блок 13 записи и блок 15 исправления сниибок (корреляционная функция адресной последовательности и отклик при превышении порога корреляционной функцией показа№Л на фиг. 3 Сз,к), По этому сигналу производится запись информационной последовательности из блока 14 памяти через блок 13 записи во второй егистр 11 сдвига. Затем п-тактов в течение кгиедого тактового интервала осуществляется рециркуляция выборок во втором регистре 11 сдвига. При этом процесс рециркуляции осуществля ется через блок 15 исправления сяиибок, где во время рециркуляции в каж дом первом, следующем за ЬтметкоЙ отсчета, тактовом интёрйале осуществляется исправление ошибок, образо ванных при разделении объединенной последовательности. Корреляционный интеграл вычисляется вторлм коррелятором 17. и при совпадении фаз опорной информационной и компрессированной информационной последовательности сигналов происхог дат превышение порога. Импульс превышения порога с второго порогового блока 21 поступает на дешифратор 23 позиции, где определяется вре менное положение отклика относительно синхроимпульса (корреляционная функция информационной последователь ности и сигнал на выходе второго порогового блока 21 приведены на фиг. 3 (и,л). Величина рассогласо ванкя д между синхроимпульсом с бло ка 22 формирования точек отсчета и импульсом с выхода второго пороговог блока 21 определяет информационный смысл передаваемой части сообщения. Применение двухканапьной корреляционной обработки объединенной пЬсле довательности позволяет оптимальным образом, выделить параметры задержки элементарных участков (букв) последо вательности относительно фазовых точек, образованных при обработке адре ной последовательности, и по парамет рам задержки (модуляции) восстановит информационный смысл передаваемого сообщения. Кроме того, в устройстве обеспечивается исп)равление сшибок (разделения) в информационной последовательности, что повышает помехоустойчивость приема информации. Формула изобретения Устройство для передачи и приема дискретной информации, содержащее на передающей стороне последовательно соединенные первый регистр сдвига, первый блок сумматоров по модулю два выход которого подключен к первому входу первого регистра сдвига и к пе вому входу сумматоров по модулю два, к второму входу которого и входу вто рого регистра сдвига подключен выход второго блока сумматоров по модулю два, к входам которого подключены выходы второго регистра сдвига, а на приемной стороне последовательно соединенные ключ и первый регистр сдвига, ,а также второй регистр сдвига и дой фратор позиции, о т л и ч а ю щ е е с я тем, что, с .целью повышения помехоустойчивости, введены на передающей стороне последовательно соед1 йенн1ле блок памяти и блок записи , выходы которого подключены к соответствунячим входам первого регистра сдвига, а на приемной стороне введены последовательно соегданенные блок разделения, блок памяти и блок записи и последовательно соединенные первый опорный генератор, первый коррелятор., первый пороговый блок, блок формирования точек отсчета и третий регистр сдвига, а также второй опорный генератор и последовательно соединенные блок исправления ошибок, второй коррелятор и второй пороговый блок, выход которого, а также выходы третьего регистра сдвига подключены к соответствующим входам дешифратора позиции, при этом выход второго опорного генератора подключен к второму входу второго коррелятора, первый вход которого объединен с первым входом второго . регистра сдвига, выход которого подключен к первому входу блока исправления ошибок, а к собтветствумадим входам второго регистра сдвига подключены выходы блока записи, к соответствуквдему входу которого,, а также к второму входу блока исправления ошибок подключен выход блока формирования точек отсчета, причем второй выход блока разделения подключен к первому входу ключа, к второму входу .которого, а также к третьему входу блока исправления сшибок и второму входу первого коррелятора подключен выход . первого регистра сдвига,- а первый вход первого коррелятора объединен с четвертым входом блока исправления ошибок. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №. 431638, кл. Н 04 L 3/00, 1972 (прототип).

C±

cr

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ АЗИМУТАЛЬНОЙ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2060541C1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство поиска шумоподобного сигнала | 1988 |

|

SU1540020A1 |

| Цифровой коррелятор | 1984 |

|

SU1264200A1 |

| Коррелятор | 1984 |

|

SU1180927A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

« 45, 4 X, 4 Ч i Sj

c± c: cz

cr cr

cr c:

c: c: cr

Фггг.

Авторы

Даты

1983-02-07—Публикация

1981-04-27—Подача