точной двоичной системе счисления (например, в устройствах умножения).

Для достижения поставленной цели устройство, содержащее два 0-триггера и элемент 2И-ИЛИ, содержит два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента НЕ и второй элемент 2И-ИЛИ, причем входные шины прложительных значений первого и второго слагаемых устройства соединены соответственно с. первыми и вторыми входами первых элементов ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ, а входные шины отрицательных значений первого и второго слагаемых соединены соответственно с первыми и вторыми входами вторых элементов ИЛИ и ИСКЛЮЧЙЮЩЕЕ ИЛИ, ВЫХОДЫ первого и второг р элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с D-входами соответственно первого и второго 0-триггеров, выходы первого и второго элементов ИЛИ подключены ко входам соответственно первого и второго элементов НЕ и к первым входам соответственно первого и второго элементов 2И-ИЛИ, вторые входы которых подключены к инверсным выходам соответственно первого и второго D-триггеров, прямые выходы которых подключены к третьим входам соответственно второго и первого элементов 2И-ИЛИ, выходы которых соединены соответственно с выходными шинами положительных и отрицательных значений результата, а четвертые входы первого и второго элементов 2И-ИЛИ подключены к -выходам соответственно второго и первого элементов НЕ.

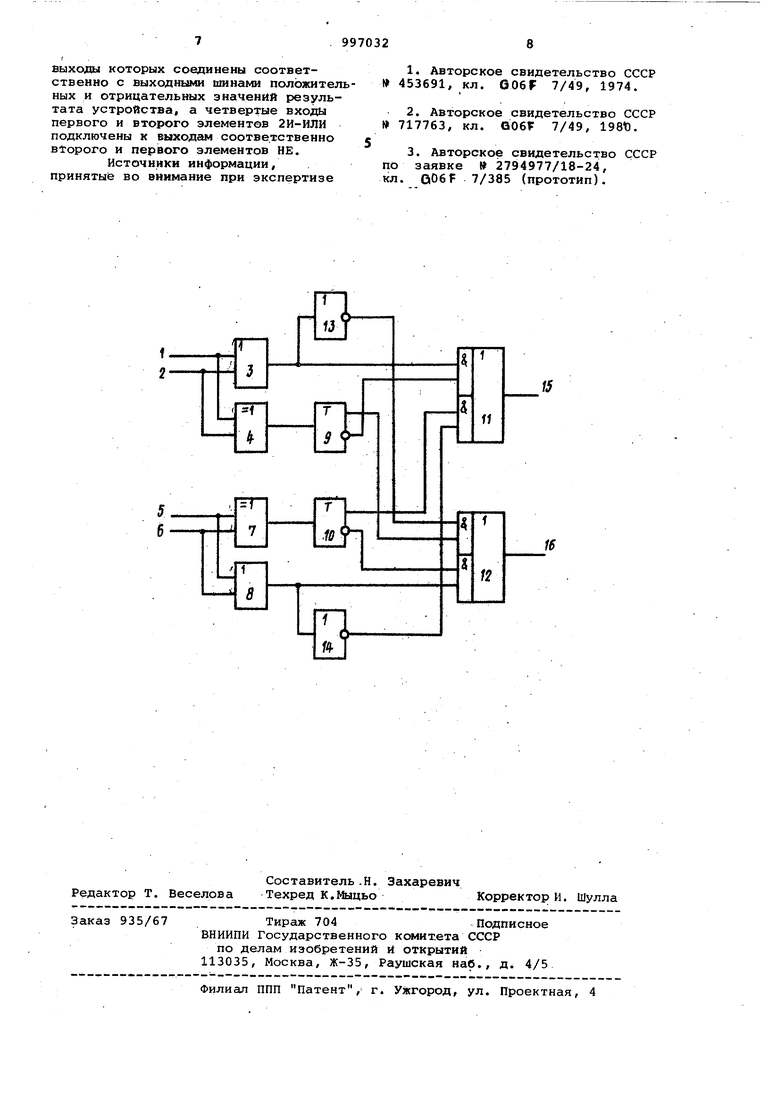

На чертеже показана функциональная схема устройства для сложения в двоичной избыточной -системе счисления.

Устройство содержит входные шины 1 и .2 положительных -значений первого и второго слагаемых устройства, первый элемент ИЛИ 3, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, входные шины 5 и 6 отрицательных значений первого и второго слагаемых устройства, вто-ч рой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, второ элемент ИЛИ 8, первый и второй О-три геры 9 и 10, первый и второй элементы 2И-ИЛИ 11 и 12, первый и второй элементы НЕ 13 и 14, выходные шины 15 и 16 положительного и отрицательного значений результата устройства.

Входные шины 1 и 2 соединены с первыми и вторыми входами элемента ИЛИ 3 и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4. Входные шины 5 и б соединены с первыми и вторыми входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и второго элемента ИЛИ 8. Выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4 и 7 соединены со входами соответственно первого и второго D-триггеров 9 и 10, инверсные выходы которых соединены со вторыми входами соответственно первого и второго элементов 2и-или 11 и 12, первые входы которых соединены со входами соответственно первого и второго элементов НЕ 13 и 14 и подключены к выходам соответственно первого и второго элементов ИЛИ 3 и 8. Прямые выходы первого и второго 6-триггеров 9 и 10 подключены к третьим входам-соответственно второго и первого элементов 2И-ИЛИ 11 и 12, четвертые входы которых соединены с выходами соответственно первого и второго элементов НЕ 13 и 14, а выходы соединены с выходными шинами 15 и 16 результата устройства.

Любое число А в двоичной избыточцой системе счисления с цифрами 1,0, 1 можно передавать по двум шинам А и А в виде последовательности двухраэрядных двоичных чисел. При сложении только положительных чисел слагаемые поступают в устройство по шинам 1 и 2 положительных значений, а при сложении.только отрицательных чисел слагаемые поступают в устройство-по шинам 5 и б отрицательных значений.

Рассмотрим работу устройства при сложении положительных чисел А и В.

На входные шины 1 и 2 устройства подаются старшими разрядами вперед числа А и.В. Если А В s О, то на выходах элемента ИЛИ 3 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 сигнал отсутствует И D-триггер 9 остается в нулевом состоянии, а на входы элемента 2И-ИЛИ 11 подаются нулевые потенциалы и на выходе 15 устройства значение результата Z равно нулю;

Если А я О и В .1 или и В а 0), то единичный сигнал появляется на выходах элемента ИЛИ 3 и ИСКЛЮЧАЮЩЕЕ ИЛИ 4. Единичный сигнал с выхода элемента ИЛИ 3 проходит через элемент 2И-ИЛИ 11 на выходную шину 15 устройства, так как D-триггер 9. находится в нулевом состоянии. Затем О-триггер по тактовому импульсу, поступающему в устройство(шина тактовых импульсов не показана), перебрасывается в единичное состояние сигналом с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.

В следующем такте работы в устройство поступает второй разряд чисел А .и В. Если одно из слагаемых (или оба) равно единице, то единичный сигнал с выхода элемента ИЛИ 3 не проходит на выход 15 устройства, так как на- второй вход- элемента 2И-ИЛИ 1 подается нулевой сигнал с инверсного выхода D-триггера 9. На выходе 16 устройства также будет нулевой сигнал, так как на вход э емента 2И-ИЛИ 12 поступает единичный сигнал с прямого выхода D-триггера, а на четвертый его вход - нулевой потенциал с выхода элемента НЕ 14.

Бели во втором такте А « В л. О, то сигнал с прямого выхода D-триггера 9 проходит через элемент 2И-ИЛИ 12 на выход 16 устройства, т.е. получаем отрицательное значение i -го разряда результата. При этом 0-триггер 9 перебросится в нулевое состояние,так как на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 нулевой потенциал.

Если А«В«1 И D-триггер находится в нулевом состоянии, то на выход 15 устройства выдается единичный сигнал, 0-триггер 9 остается в нулевом состоянии.

Если АшВ.а и О-триггер 9 нажодится в единичном состоянии, то на выход 15 устройства выдается нулевой сигнал, а 0-триггер 9 перебраси-, ьается в нулевое состояние.

Сложение отрицательных чисел производится ангшогично с помощью элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7, ИЛИ 8 НЕ 14, и 2И-ИЛИ 12.

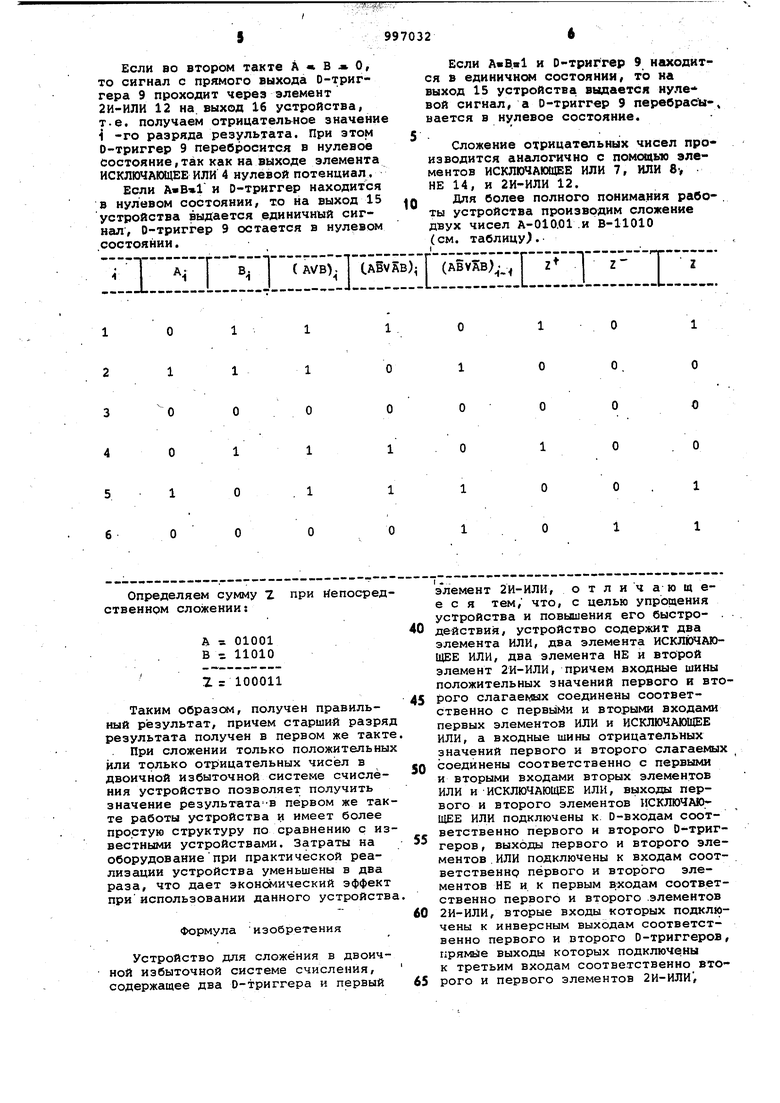

Для более полного понимания рабо- .

0 ты устройства производим сложение двух чисел А-010.01 .и В-11010 (см. таблицу).

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Накапливающий сумматор | 1980 |

|

SU920706A2 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Устройство для сложения в избыточнойдВОичНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824201A1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Отсчетное устройство | 1976 |

|

SU661548A1 |

| Устройство для сложения чисел | 1976 |

|

SU634274A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1564614A1 |

Z г 100011

Таким образом, получен правильный результат, причем старший разряд результата получен в первом же такте

При сложении только положительных или только отрицательных чисел в двоичной избыточной системе счисления устройство позволяет получить значение результата в первом же такте работы устройства и имеет более простую структуру по сравнению с известными устройствами. Затраты на оборудование при практической реализации устройства уменьшены в два раза, что дает зконсмический эффект прииспользовании данного устройства

Формула изобретения

Устройство для сложения в двоичной избыточной системе счисления, содержащее два 0-триггера и первый

злемент 2И-ИЛИ, причем входные шины положительных значений первого и второго слагаемых соединены соответственно с первыми и вторыми входами первых элементов ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ, а входные шины отрицательных значений первого и второго слагаемых соединены соответственно с первыми и вторыми входами вторых элементов ИЛИ и -ИСКЛЮЧАЮЩЕЕ ИЛИ, ВЫХОДЫ первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к. D-входам соответственно первого и второго 0-триггеров, выходы первого и второго элементов .ИЛИ подключены к входам соответственно первого и второго элементов НЕ и к первым входам соответственно первого и второго .элементов 2И-ИЛИ, вторые входы которых подключены к инверсным выходам соответственно первого и второго 0-триггеров, прямые выходы которых подключены к третьим входам соответственно второго и первого элементов 2И-ИЛИ,

выходы которых соединены соответственно с выходными шинами положительных и отрицательных значений результата устройства, а четвертые входы первого и второго элементов 2И-ИЛИ подключены к выходам соответственно второго и первого элементов НЕ.

Источники информации, принятые во внимание при экспертизе

кл. Q06F 7/385 (прототип).

Авторы

Даты

1983-02-15—Публикация

1981-07-22—Подача