t

Изобретение относится к вычислительной технике и может быть исполь зовано в вычислительных машинах и устройствах, работающих в избыточной двоичной системе счисления с цифрами 1, О и 1.

В известных устройствах для последовательного суммирования чисел в двоичной системе счисления и в избыточной двоичной системе счисления с цифрами 1,0, 1, суммируемые числа подаются младшими разрядами вперед.

В избыточной системе счисления перенос передается только на следующий разряд, что позволяет производить сложение старшими разрядами вперед, т.е. получать результат на выходе сумматора по мере накопления входны:; частей 1 и 2.

Известно устройство для параллелького сложения и вычитания двух чисел в избыточной двоичной системе счисления, содержащее в каждом разряде блоки формирования отрицательной суммы, положительной суммы, отрицательного переноса, положительного переноса и блок формирования результата р1.

Недостатком известного устройства является большое количество оборудования, требуемого для его реализации

Наиболее близким к предлагаемому по технической сущности является усройство для сложения в избыточной двоичной системе, содержащее блоки формирования положительной и отрицательной суммы, блоки формирования пложительного, и отрицательного переноса, блок формирования результата и три элемента задержки. Устройство требует для своей реализации небольшого количества оборудования 4 .

Однако устройство обладает недостаточно высоким быстродействием, так как велика временная задержка результата, определяемая задержками составных частей устройства.

Цель изобретения - увеличение быстродействия.

Для достижения поставленной цели в устройство, содержащее три элемента задержки и- блок формирования результата, причем выходы блока формирования результата подключены к выходным шинам устройства, введены четвертый элемент задержки и блок .анализа входных аргументов, причем элементы задержки выполнены наDтриггерах, входные шины устройства подключены ко входам блока анализа ВХОДНЫХ аргументов, первый и второй

выходы которого соединены с первым и вторым, входами блока формирования результатов, второй, третий и чет- вертый выходы блока анализа входных аргументов соединены со входами соответственно первого, второго и третьего D-триггеров, прямой и инверсный выходыпервого 0-триггера соединены с третьим и четвертым входами блока формирования результаi-a соответственно, пятый и шестой входы которого подключены к прямому и инверсному выходам второго О-триггера соответственно, прямой и инверсный выходы третьего D-триггера подключены к седьмому и восьмому входам блока формирования, результата соответственно, девятый и десятый входы которого соединены соответственно с прямым и инверсным выходами четвертого О-триггера, вход которого подключен к выходу третьего элемента задержки.

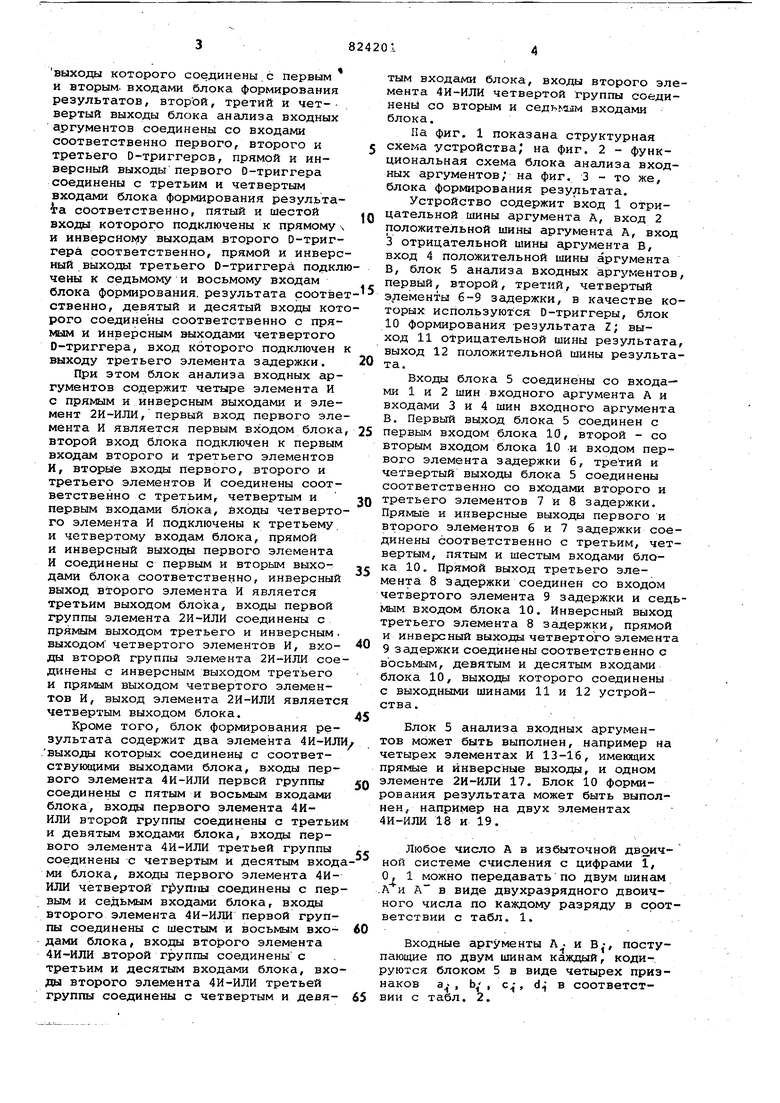

При этом блок анализа входных аргументов сод: ержит четыре элемента И с прямым и инверсным выходами и элемент 2И-ИЛИ, первый вход первого элемента И является первым входом блока, второй вход блока подключен к первым входам второго и третьего элементов И, вторые входы первого, второго и третьего элементов И соединены соответственно с третьим, четвертым и первым входами блока, входы четвертого элемента И подключены к третьему и четвертому входам блока, прямой и инверсный выходы первого элемента И соединены с первым и вторым выходами блока соответственно, инверсный выход второго элемента И является третьим выходом блока, входы первой группы элемента 2И-ИЛИ соединены с прямым выходом третьего и инверсным. выходом четвертого элементов И, входы второй группы элемента 2И-ИЛИ соединены с инверсным выходом третьего и выходом четвертого элементов И, выход элемента 2И-ИЛИ является четвертым выходом блока.

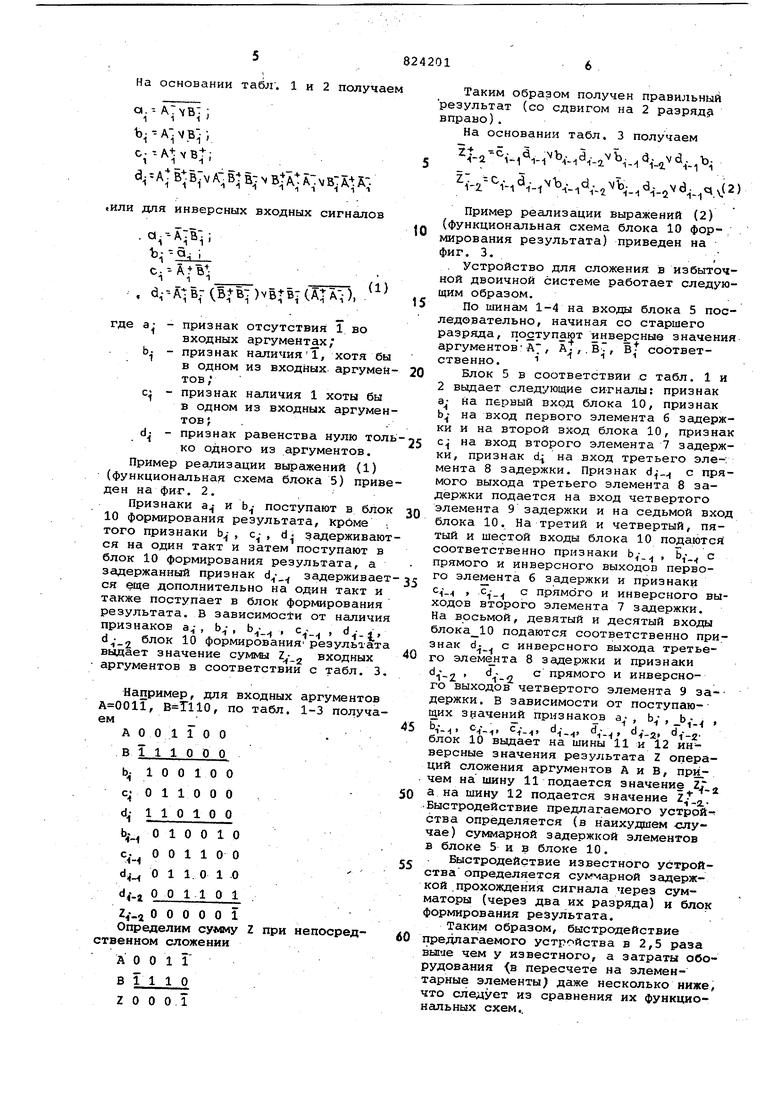

Кроме того, блок формирования результата содержит два элемента 4И-ИЛИ .выходы которых соединены с соответствующими выходами блока, входы первого элемента 4 И-ИЛИ первой группы соединены с пятым и восьмым входами блока, входы первого элемента 4ИИЛИ второй группы соединены с третьим и девятым входами блока, входы первого элемента 4И-ИЛИ третьей группы соединены с четвертым и десятым входами блока, входы первого элемента 4ИИЛИ четвертой группы соединены с первым и седьмым входами блока, входы второго элемента 4И-ИЛИ первой группы соединены с шестым и восьмым входами блока, входы второго элемента 4И-ИЛИ второй группы соединены с третьим и десятым входами блока, входы второго элемента 4И-ИЛИ третьей группы соединены с четвертым и девятым входами блока, входы второго элемента 4И-ИЛИ четвертой группы соединеньа со вторым и седь.1ам входами блока.

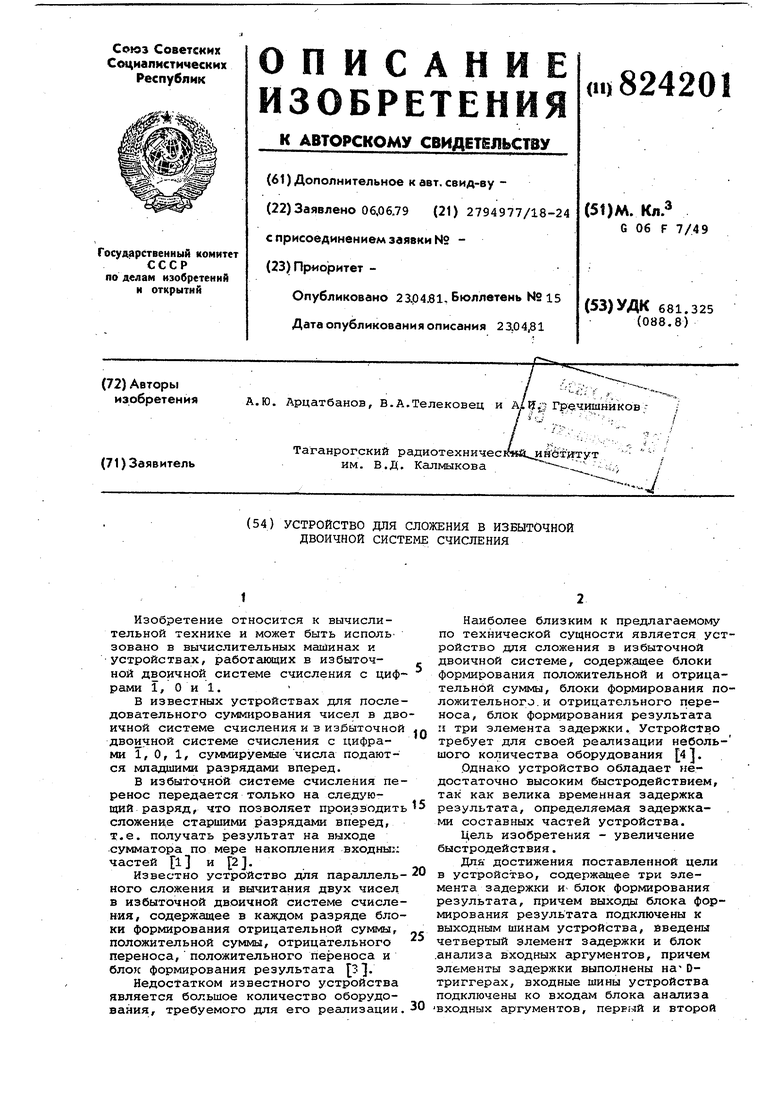

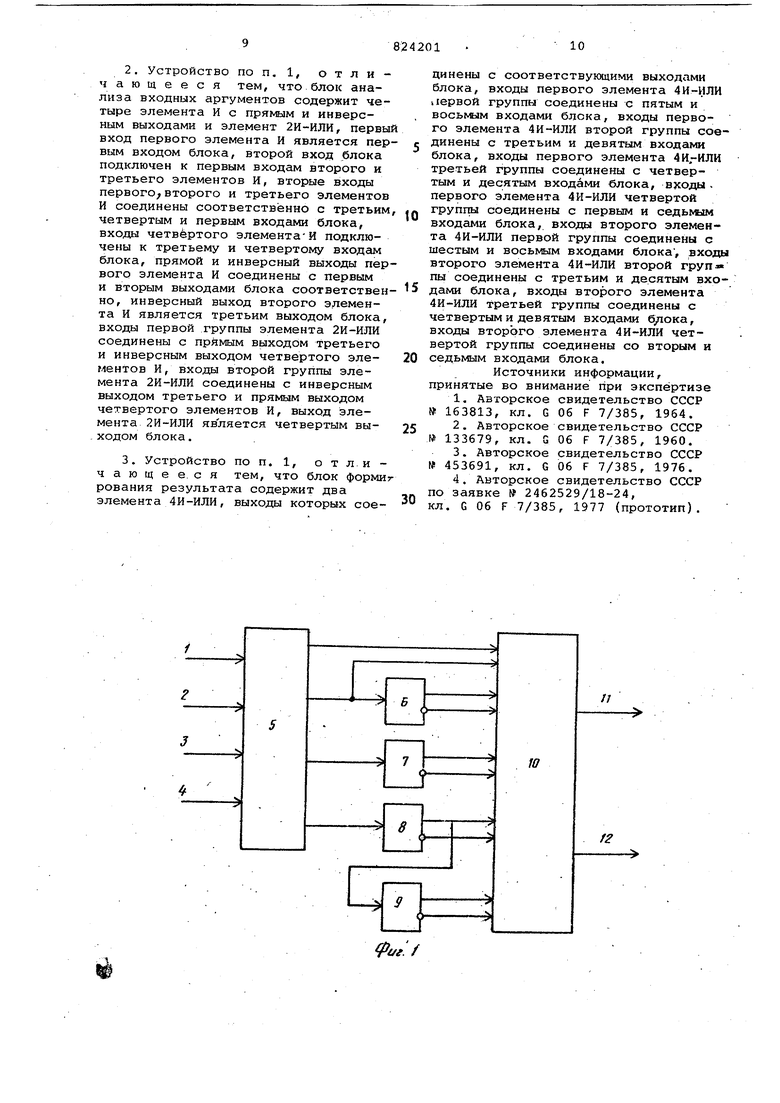

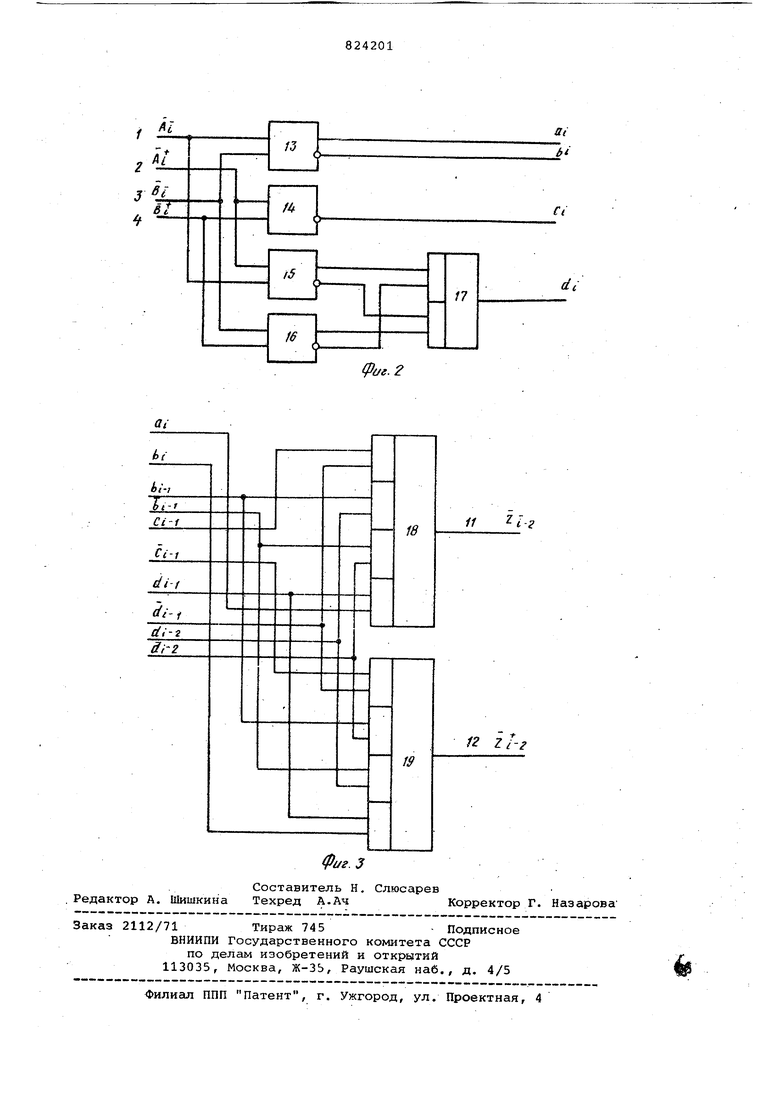

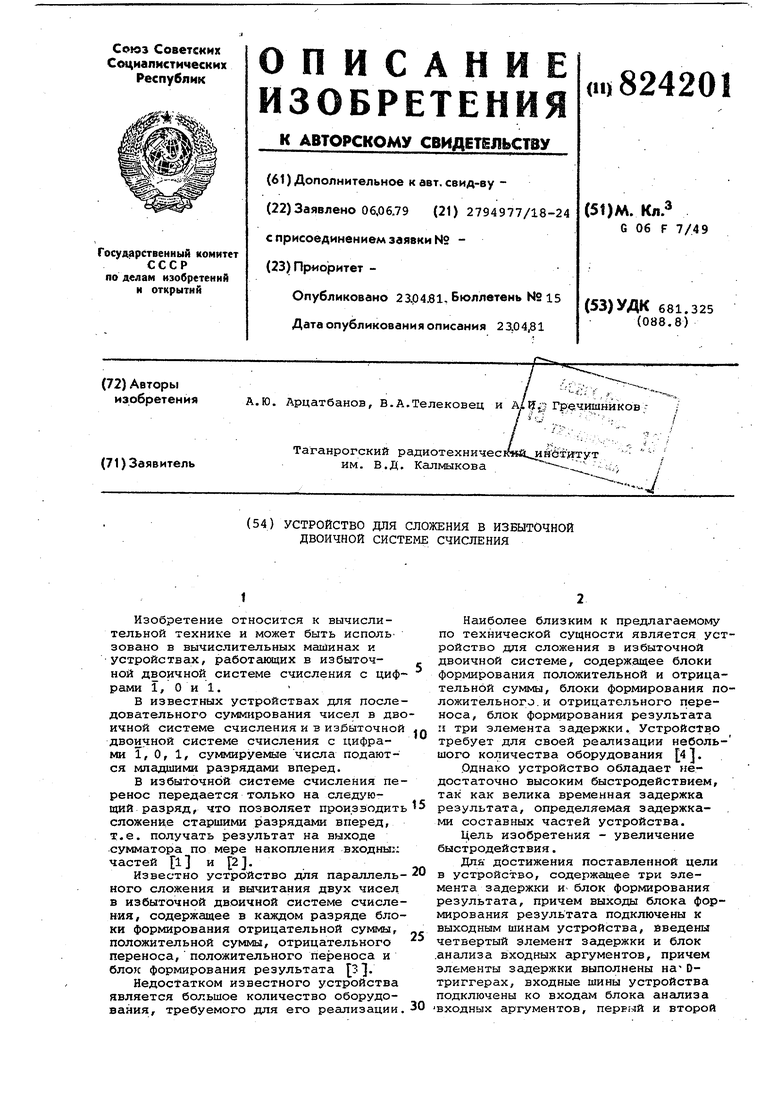

На фиг. 1 показана структурная схема устройства; на фиг. 2 - функциональная схема блока анализа входных аргументов; на фиг. 3 - то же, блока формирования результата.

Устройство содержит вход 1 отрицательной шины аргумента А, вход 2 положительной шины аргумента А, вход 3 отрицательной шины аргумента в, вход 4 положительной шины аргумента В, блок 5 анализа входных аргументов первый, второй, третий, четвертый э.лементы 6-9 задержки, в качестве которых используются О-триггеры, блок 10 формирования -результата Z; выход 11 отрицательной шины результата выход 12 положительной шины результата.

Входы блока 5 соединены со входами 1 и 2 шин входного аргумента А и входами 3 и 4 шин входного аргумента В. Первый выход блока 5 соединен с первым входом блока 10, второй - со вторым входом блока 10 .и входом первого элемента задержки б, третий и четвертый выходы блока 5 соединены соответственно со входами второго и третьего элементов 7 и 8 задержки. Прямые и инверсные выходы первого и второго элементов 6 и 7 задержки соединены соответственно с третьим, четвертым, пятым и шестым входами блока 10. Прямой выход третьего элемента 8 задержки соединен со входом четвертого элемента 9 задержки и седмым входом блока 10. Инверсный выход третьего элемента 8 задержки, прямой и инверсный выходы четвертого элемента 9 задержки соединены соответственно с восьмым, девятым и десятым входами блока 10, выходы которого соединены с выходными шинами 11 и 12 устройства.

Блок 5 анализа входных аргументов может быть выполнен, например на четырех элементах И 13-16, имеквдих прямые и инверсные выходы, и одном элементе 2И-ИЛИ 17. Блок 10 формирования результата может быть выполнен, например на двух элементах 4И-ИЛИ 18 и 19.

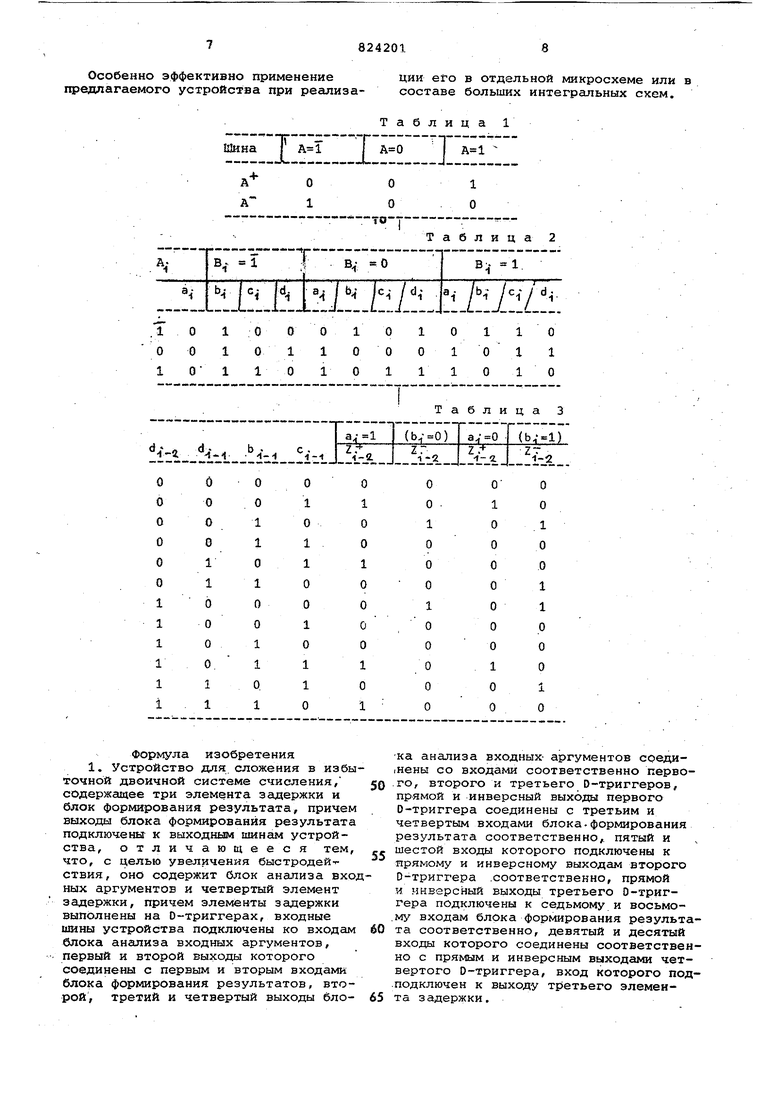

Любое число А в избыточной двоичной системе счисления с цифрами 1, О, 1 можно передавать по двум шинам . А в виде двухразрядного двоичного числа по каждому разряду в срответствии с табл. 1.

Входные аргументы А- и , поступаюише по двум шинам каждый, коди-. руются блоком 5 в виде четырех признаков а f Ь , , d в соответствии с табл. 2. На основании табл; 1 и 2 получа «, Ъ-А:ГВ---; c.--AtvB-; a-A;B;B:vA:;§ &:vB|XtA:vB: s; «или для инверсных входных сигнало .Ц- - Qj i . , d -- A Вг (Б| ВТ ) VBt В (А: А;- ), где а - признак отсутствия 1 во входных аргументах; - признак наличия1, хотя в одном из входных аргум тов; с: - признак наличия 1 хоты б в одном из входных аргум тов f . d: - признак равенства нулю т ко одного из аргументов. Пример реализации выражений (1 (функциональная схема блока 5) при ден на фиг. 2. Признаки и поступают в бл 10 формирования результата, кроме того признаки , , d задержива ся на один такт и затем поступают блок 10 формирования результата, а задержанный признак d, задержива ся еще дополнительно на один такт также поступает в блок формировани результата. В зависимости от налич признаков , , Ь , , d. d.- „ блок 10 формированиярезульта -1-2 выдает значение сум1«ы Z входных аргументов в соответствии с табл. Например, для входных аргументо , , по табл. 1-3 получ ем А О О 1 1 О О. В 111 00 О Ь,- 1 О О 1 О О О 1 1 О О О 110100 bf О 1 О О 1 О с. О О 1 1 О О d О 1 1. О 1 .0 df.j, 001101 , z.2 О О О О О i Определим Z при непосредственном сложении А О О 1 Г В 1110 ZOO 01 Таким образом получен правильный результат (со сдвигом на 2 разряду вправо). На основании табл. 3 получаем Zt,-e,.vb,.,d,.,vb..,c}.vd..b. iV 4-1 -.--ЛЧч.ч Ч--. -.--2 2) Пример реализации выражений (2) (функциональная схема блока 10 фор- , мирования результата) приведен на фиг. 3., Устройство для сложения в избыточной двоичной системе работает следующим образом. По шинам 1-4 на входы блока 5 последовательно, начиная со старшего разряда, поступают инверсные значения соответаргументовА, А,.В, ственно. Блок 5 в соответствии с табл. 1 и 2 выдает следующие сигналы: признак а- на первый вход блока 10, признак на вход первого элемента 6 задержки и на второй вход блока 10, признак с на вход второго элемента 7 задержки, признак d на вход третьего эле-: мента 8 задержки. Признак с прямого выхода третьего элемента 8 задержки подается на вход четвертого элемента 9 задержки и на седьмой вход блока 10. На третий и четвертый, пятый и шестой входы блока 10 подаются соответственно признаки bY. , b,- с прямого и инверсного выходов первого элемента 6 задержки и признаки c , S- прямого и инверсного выходов второго элемента 7 задержки. На восьмой, девятый и десятый входы блока 10 подаются соответственно признак d с инверсного выхода третьего элемента 8 задержки и признаки d. п с прямого и инверсного выходов четвертого элемента 9 за- держки. В зависимости от поступающих значений признаков аь,-,ь,-. , ., d.j i-гблок 10 выдает на шины 11 и 12 инверсные значения результата 2 операций сложения аргументов А и В, при.чем на шину 11 подается значение а на шину 12 подается значение Z.,. Быстродействие предлагаемого устройства определяется (в наихудшем случае) суммарной задержкой элементов в блоке 5 и в блоке 10. Быстродействие известного устройства определяется суммарной задержкой прохождения сигнала через сумматоры (через два их разряда) и блок формирования результата. Таким образом, быстродействие предлагаемого устройства в 2,5 раза выие чем у известного, а затраты оборудования (в пересчете на элементарные элементы даже несколько ниже, что следует из сравнения их функциональных схем.. Особенно эффект предлагаемого устр А. To 00 10

0 0 0 0

0

0 0

1

1 1

0

1 1

1 1

0

1

0 0

0 0 0 0.

0 0

1

1 1

0

1

1 1

1

0

1

0

0

0 0

0 0

1

1

. 1

0 0 0 0 0 0 0

0 0 0

0

0

1 1

1

0 0 0 0 0

0 0 0

1

1

0 0

0 вно применение ции его в отдельной микросхеме или в йства при реализа- составе больших интегральных схем. Шина Т 1 а О01 А 1О.0 «. .. -«.--.-«...jj-. . В, 1f 0В- 1 l 100010 1 0 1 10 1 01 1 00 0101 1 1 10 10 1 11 010 1 () Г(Ь,) Таблица Т а б л и ц а 2 ТаблицаЗ fikJ- ik l5LijL...

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения в избыточной двоичной системе счисления | 1981 |

|

SU1587494A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для сложения в двоичном избыточном коде | 1987 |

|

SU1413623A1 |

| Сумматор в избыточной двоичной системе счисления | 1982 |

|

SU1042011A1 |

| УСТРОЙСТВО ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ КАНАЛА ВОСПРОИЗВЕДЕНИЯ АППАРАТУРЫ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ | 1991 |

|

RU2024968C1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| РАСШИРИТЕЛЬ ИНТЕРФЕЙСА "КАНАЛ ОБЩЕГО ПОЛЬЗОВАНИЯ" | 2009 |

|

RU2402805C1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

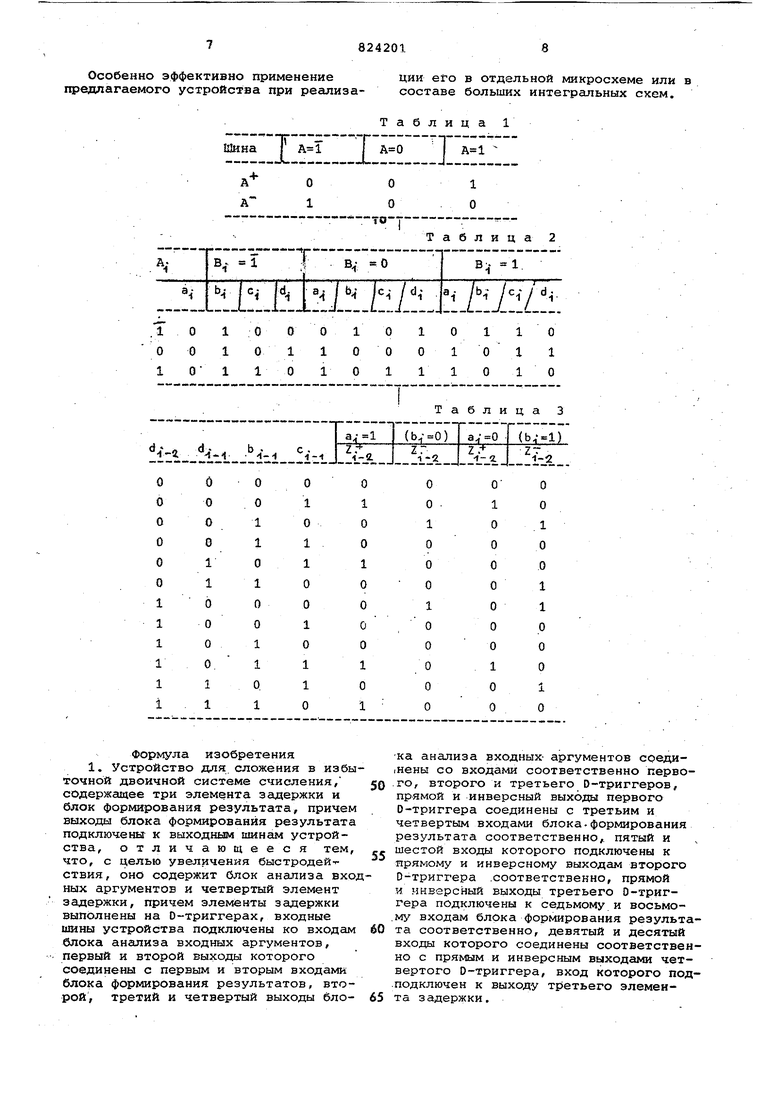

Формула изобретения 1. Устройство для,сложения в избы точной двоичной системе счисления/ содержащее три элемента задержки и блок формирования результата, причем выходы блока формирования результата подключены к выходным шинам устройства, отличающееся тем, что, с целью увеличения быстродей-гствия, оно содержит блок анализа вхо ных аргументов и четвертый элемент задержки, причем задержки выполнены на D-триггерах, входные шины устройства подключены ко входам блока анализа входных аргументов, первый и второй выходы которого соединены с первым и вторым входами блока формирования результатов, второй, третий и четвертый выходы блока анализа входных- аргументов соеди|Нены со входами соответственно первого, второго и третьего D-триггеров, прямой и инверсный выходы первого О-триггера соединены с третьим и четвертым входами блока.формирования результата соответственно,, пятый и шестой входы которого подключены к прямому и инверсному выходам второго D-триггера .соответственно, прямой и инверсный выходы третьего О-триггера подключены к седьмому и восьмому входам блока формирования результата соответственно, девятый и десятый входы которого соединены соответственно с прямым и инверсным выходами четвертого D-триггера, вход которого под.подключен к выходу ТЕ етьего элемента задержки. 2, Устройство по п. 1, отличающееся тем, что блок анализа входных аргументов содержит четыре элемента И с прямым и инверсным выходами и элемент 2И-ИЛИ, первы вход первого элемента И является пер вым входом блока, второй вход блока подключен к первым входам второго и третьего элементов И, вторые входы первого;второго и третьего элементов И соединены соответственно с третьим четвертым и первым входами блока, входы четвёртого элемента-И подключены к третьему и четвертому входам блока, прямой и инверсный выходы пер вого элемента И соединены с первым и вторым выходами блока соответствен но, инверсный выход второго элемента И является третьим выходом блока входы первой группы элемента 2И-ИЛИ соединены с прямым выходом третьего и инверсным выходом четвертого элементов И, входы второй группы элемента 2И-ИЛИ соединены с инверсным выходом третьего и прямым выходом четвертого элементов И, выход элемента 2И-ИЛИ является четвертым вы.ходом блока. 3. Устройство по п. 1, отл.и чающее. ся тем, что блок форми рования результата содержит два элемента 4И-ИЛИ, выходы которых сое дннены с соответствующими выходами блока, входы первого элемента 4И-ИЛИ 11ервой группы соединены с пятым и восьмым входами блока, входы первого элемента 4И-ИЛИ второй группы соединены с третьим и девятым входами блока, входы первого элемента 4И-ИЛИ третьей группы соединены с четвертым и десятым входами блока, входы . первого элемента 4И-ИЛИ четвертой группы соединены с первым и седьмым входами блока, входы второго элемента 4И-ИЛИ первой группы соединены с шестым и восьмым входами блока , входы второго элемента 4И-ИЛИ второй груп пы соединены с третьим и десятым входами блока, входы второго элемента 4И-ИЛИ третьей группы соединены с четвертым и девятым входами б/юка, входы второго элемента 4И-ИЛИ четвертой группы соединены со вторым и седьмым входами блока. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 163813, кл. G 06 F 7/385, 1964. 2,Авторское свидетельство СССР № 133679, кл. G 06 F 7/385, 1960. 3.Авторское свидетельство СССР № 453691, кл. G 06 F 7/385, 1976. 4.Авторское свидетельство СССР по заявке № 2462529/18-24, кл. G 06 F 7/385, 1977 (прототип).

ТГ

Ci-f

li

11

18

12 Zi-г

Авторы

Даты

1981-04-23—Публикация

1979-06-06—Подача