Изобретение относится к области вычислительной техники и может быть использовано в арифметических устройствах программного управления, вычислительных машинах и цифровых измерительных приборах.

Известно отсчетное устройство, содержащее регистры, шифраторы, сумматоры, элементы И. ИЛИ 1. Недостатком его является сложность.

Наиболее близким техническим решением к данному предложению является отсчетное устройство, содержащее распределитель импульсов, первый выход которого подключен ко входу регистра сдвига, второй - ко входам управления блока ввода информации и блока индикации, третий - к первым входам .элементов И группы, четвертый - к управляющему входу шифратора, первый информационный вход которого подключен к выходу блока ввода информации, выход шифратора подключен к первому информационному входу сумматора, втбрая группа информационных входов которого соединена с выходами элементов И группы, выход сумматора соединен с информационным входом регистра и с первым входом блока индикации, первый вход которого подключен ко вторым входам элементов И труппы 2. Недостатком его является невозможность работы с отрицательными числами и низкая достоверность информации.

Целью изобретения является расширение диапазона исходных чисел и повышение достоверности.

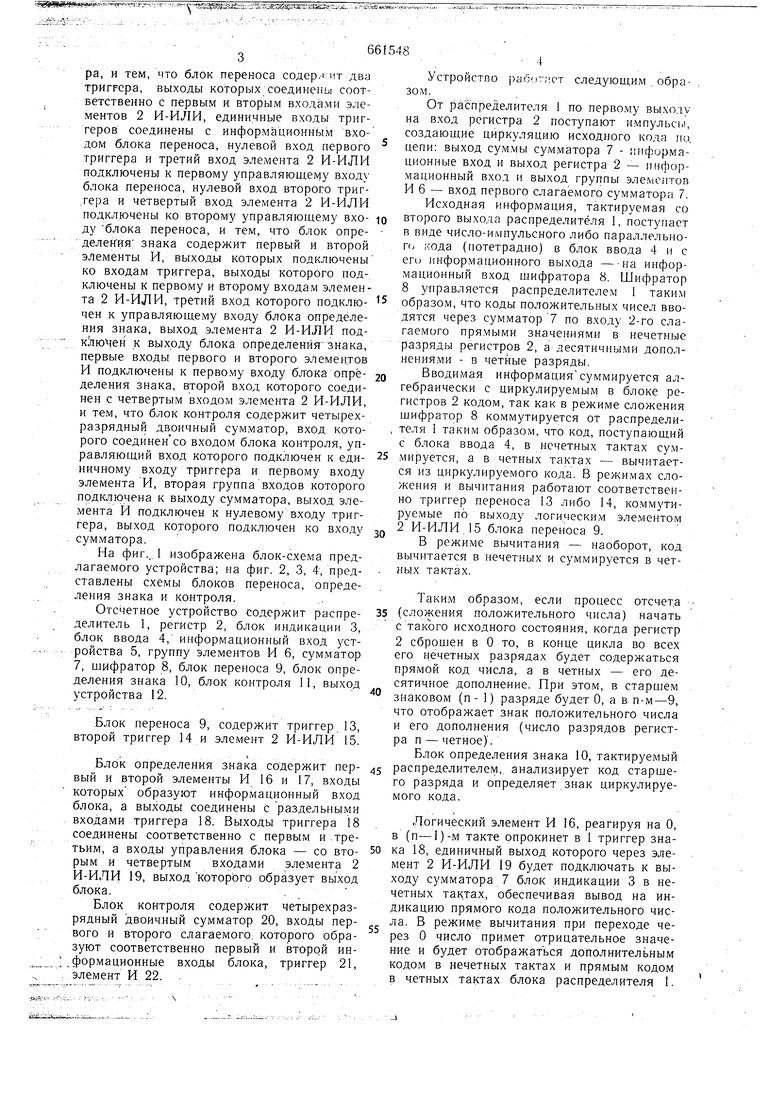

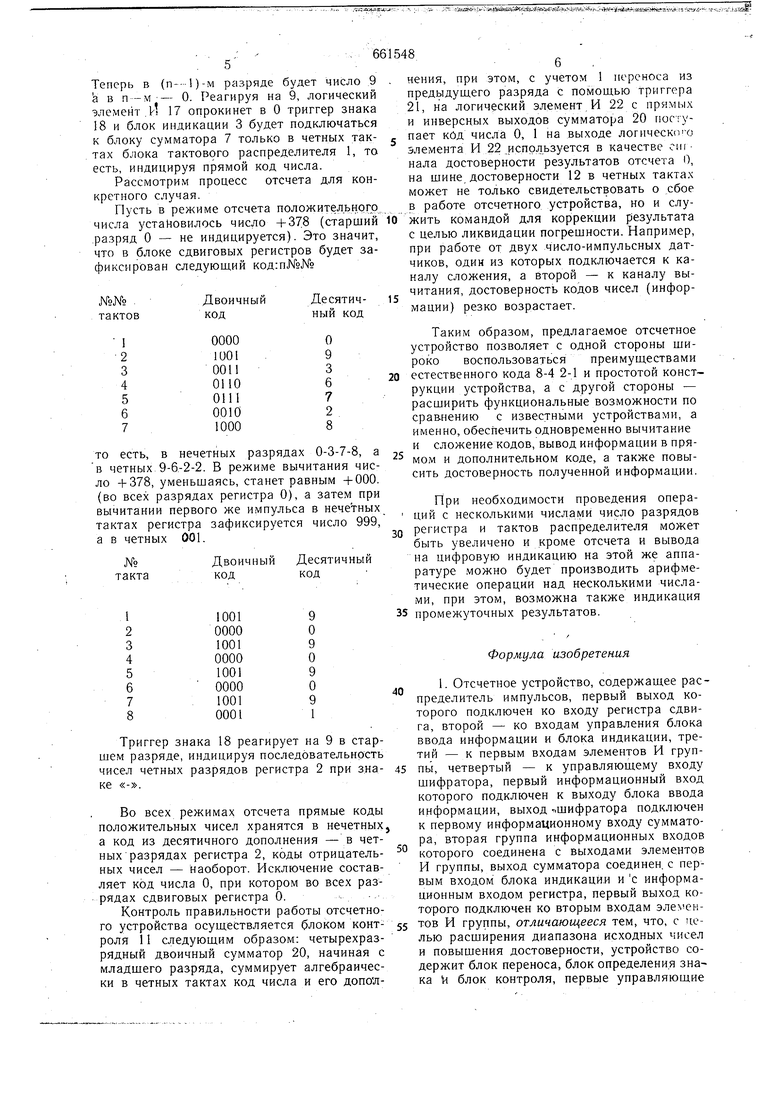

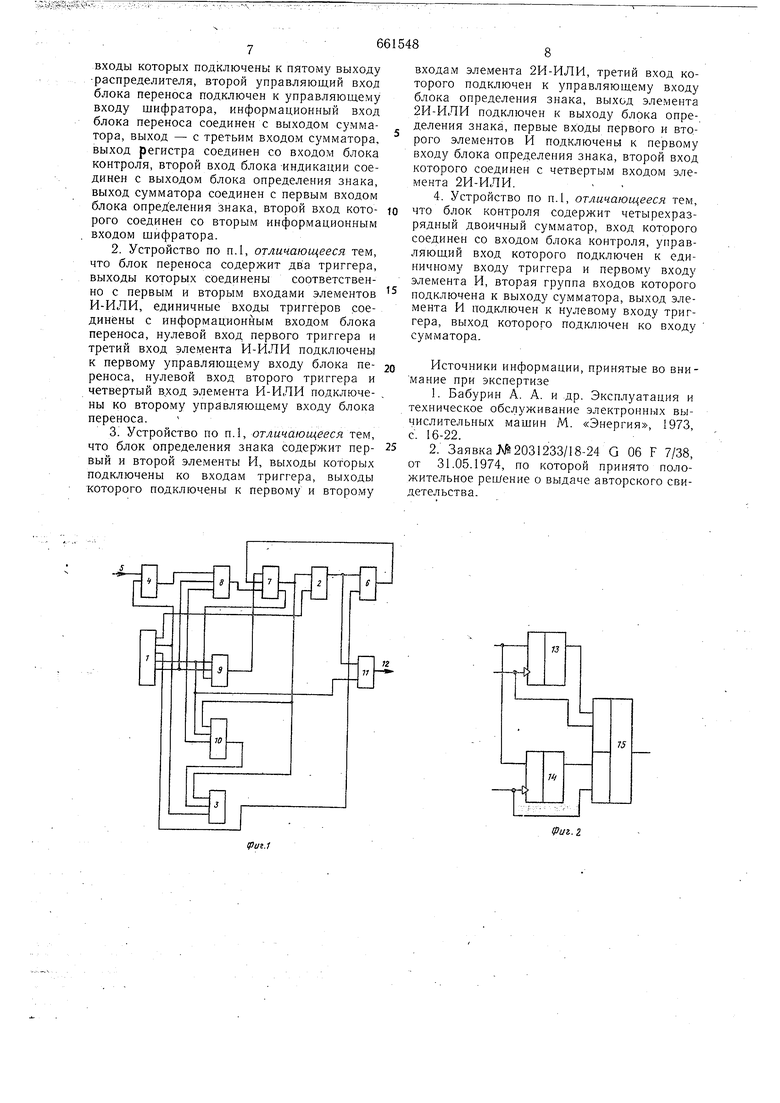

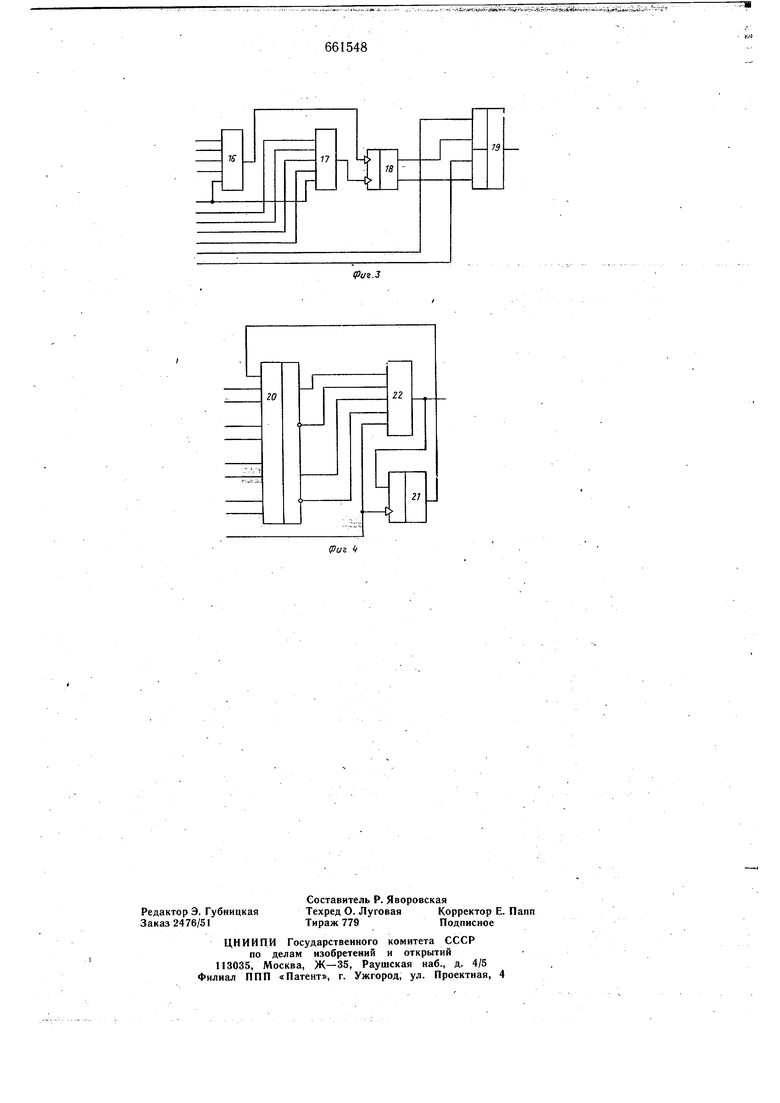

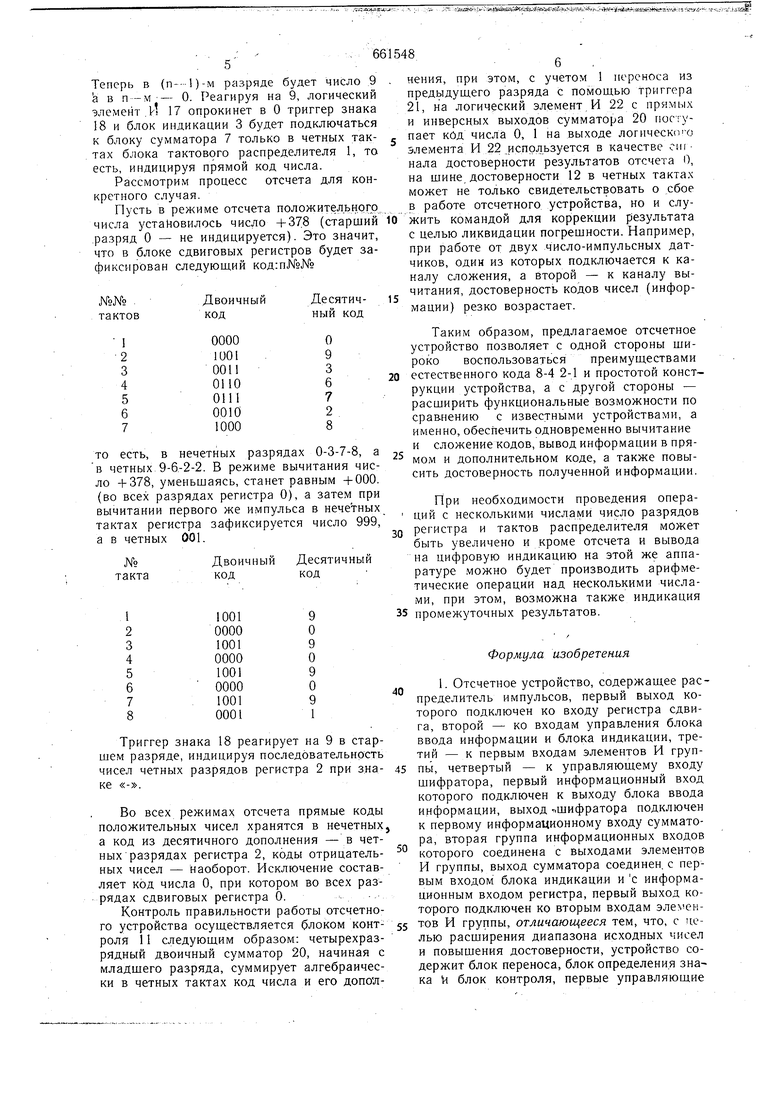

Цель изобретения достигается тем, что устройство содержит блок переноса, блок определения знака и блок контроля, первые управляющие входы которых подключены к пятому выходу pacпpeдeлитeJ|я, второй управляющий вход блока переноса подключен к управляющему входу шифратора, информационный вход блока переноса соединен с выходом сумматора, выход - с третьим входом сумматора, выход регистра соединен со входом блока контроля, второй вход блока индикации соединен с выходом блока определения знака, выход сумматора соединен с первым входом блока определения. знака, второй вход которого соединен со вторым информационным входом шифратоpa, и тем, что блок переноса содер.-кит дву триггера, выходы которых соединены соответственно с первым и вторым входами элементов 2 И-ИЛИ, единичные входы триггеров соединены с информационным входом блока переноса, нулевой вход первого триггера и третий вход элемента 2 И-ИЛИ подключены к первому управляющему входу блока переноса, нулевой вход второго триг.гера и четвертый вход элемента 2 И-ИЛИ подключены ко второму управляющему входу блока переноса, и тем, что блок определения: знака содержит первый и второй элементы И, выходы которых подключены ко входам триггера, выходы которого подключены к первому и второму входам элемента 2 И-ИЛИ, третий вход которого подключен к управляющему входу блока определения знака, выход элемента 2 И-ИЛИ подк люмен к выходу блока определениязнака, первые входы первого и второго элементов И подключены к первому входу блока опрёделения знака, второй вход которого соединен с четвертым входом элемента 2 И-ИЛИ, и тем, что блок контроля содержит четырехразрядный двоичный сумматор, вход которого соединенсо входом блока контроля, управляющий вход которого подключен к единичному входу триггера и первому входу элемента И, вторая группа входов которого подключена к выходу сумматора, выход элемента И подключен к нулевому входу триггера, выход которого подключен ко входу сумматора. На фиг... 1 изображена блок-схема предлагаемого устройства; на фиг. 2, 3, 4, представлены схемы блоков переноса, определения знака и контроля. Отсчетное устройство содержит распределитель 1, регистр 2, блок индикации 3, блок ввода 4, информационный вход устройства 5, группу элементов И 6, сумматор 7, щифратор 8, блок переноса 9, блок определения знака 10, блок контроля 11, выход устройства 12. Блок переноса 9, содержит триггер, 13, второй триггер 14 и элемент 2 И-ИЛИ 15. Блок определения знака содержит первый и второй элементы И 16 и 17, входы которых образуют информационный вход блока, а выходы соединены с раздельными входами триггера 18. Выходы триггера 18 соединены соответственно с первым и .третьим, а входы управления блока - со вторым и четвертым входами элемента 2 И-ИЛИ 19, выход которого образует выход блока. , Блок контроля содержит четырехразрядный двоичный сумматор 20, входы первого и второго слагаемого, которого образуют соответственно первый и второй ин формационные входы блока, триггер 21, элемент И 22.

661548 Устройство следующим . обраОт распределителя 1 по первому выходу на вход регистра 2 поступают импульсы, создающие циркуляцию исходного кода кц цепи: выход суммы сумматора 7 - информационные вход и выход регистра 2 - информационный вход и выход группы элементов И 6 - вход первого слагаемого сумматора 7. Исходная информация, тактируемая со второго выхода распределителя 1, поступает в виде чИсло-импульсного либо параллельного кода (иотетрадно) в блок ввода 4 и с еги информационного выхода -на информационный вход щифратора 8. Шифратор 8 управляется распределителем 1 таким образом, что коды положительных чисел вводятся через сумматор7 по входу 2-го слагаемого прямыми значениями в нечетные разряды регистров 2, а десятичными дополнениями - в четные разряды. Вводимая информациясу.ммируется алгебраически с циркулируемым в блоке регистров 2 кодом, так как в режиме сложения щифратор 8 коммутируется от распределителя 1 таким образом, что код, поступающий с блока ввода 4, в нечетных тактах суммируется, а в четных тактах - вычитается из циркулируемого кода. В режимах сложения и вычитания работают соответственно триггер переноса 13 либо 14, коммутируемые по выходу логически.м элементом 2 И-ИЛИ 15 блока переноса 9. В режиме вычитания - наоборот, код вычитается в нечетных и суммируется в четных тактах. Таким образом, если процесс отсчета (сложения положительного числа) начать с такого исходного состояния, когда регистр 2 сброщен в О то, в конце цикла во всех его нечетных разрядах будет содержаться прямой код числа, а в четных - его десятичное дополнение. При этом, в старщем знаковом (п - 1) разряде будет О, а в п-м-9, что отображает знак положительного числа и его дополнения (число разрядов регистра п - четное). Блок определения знака 10, тактируемый распределителем,, анализирует код старщего разряда и определяет знак циркулируемого кода. Логический элемент И 16, реагируя на О, в (п-1)-.м такте опрокинет в I триггер знака 18, единичный выход которого через элемент 2 И-ИЛИ 19 будет подключать к выходу сумматора 7 блок индикации 3 в нечетных тактах, обеспечивая вывод на индикацию прямого кода положительного числа. В режиме вычитания при переходе через О число примет отрицательное значение и будет отображаться дополнительным кодом в нечетных тактах и прямым кодом в четных тактах блока распределителя 1.

5 Теперь в {п--1)-м разряде будет число 9 а в п -м - 0. Реагируя на 9, логический элемент.И 17 опрокинет в О триггер знака 18 и блок индикации 3 будет подключаться к блоку сумматора 7 только в четных тактах блока тактового распределителя 1, то есть, индицируя прямой код числа. Рассмотрим процесс отсчета для конкретного случая. Пусть в режиме отсчета положительного числа установилось число +378 (старший ра.зряд О - не индицируется). Это значит, что в блоке сдвиговых регистров будет зафиксирован следующий код:п№№ Двоичный Десятичный код код то есть, в нечетных разрядах 0-3-7-8, а в четных 9-6-2-2. В режиме вычитания число -t-378, уменьшаясь, станет равным +000. (во всех разрядах регистра 0), а затем при вычитании первого же импульса в нечетных тактах регистра зафиксируется число 999, а в четных 001. Десятичный Двоичный код код Триггер знака 18 реагирует на 9 в старшем разряде, индицируя последовательность чисел четных разрядов регистра 2 при знаВо всех режимах отсчета прямые коды положительных чисел хранятся в нечетных, а код из десятичного дополнения - в четных разрядах регистра 2, коды отрицательных чисел - наоборот. Исключение составляет код числа О, при котором во всех разрядах сдвиговых регистра 0. Контроль правильности работы отсчетного устройства осуществляется блоком контроля 11 следующим образом: четырехразрядный двоичный сумматор 20, начиная с младщего разряда, суммирует алгебраически в четных тактах код числа и его допол6нения, при этом, с учетом 1 переноса из предь1дущего разряда с помощью триггера 21, на логический элемент.И 22 с прямых и инверсных выходов сумматора 20 носгупает кОд числа О, 1 на выходе логически-о элемента И 22,используется в качестве сигнала достоверности результатов отсчета О, на шине,достоверности 12 в четных тактах может не только свидетельствовать о сбое в работе отсчетного устройства, но и служить командой для коррекции результата с целью ликвидации погрешности. Например, при работе от двух число-импульсных датчиков, один из которых подключается к каналу сложения, а второй - к каналу вычитания, достоверность кодов чисел (информации) резко возрастает. Таким образом, предлагаемое отсчетное устройство позволяет с одной стороны щироко воспользоваться преимуществами естественного кода 8-4 2-1 и простотой конструкции устройства, а с другой стороны - расширить функциональные возможности по срав.нению с известными устройствами, а именно, обеспечить одновременно вычитание и сложение кодов, вывод информации в прямом и дополнительном коде, а также повысить достоверность полученной информации. При необходимости проведения операций с несколькими числами число разрядов регистра и тактов распределителя может быть увеличено и кроме отсчета и вывода на цифровую индикацию на этой же аппаратуре можно будет производить арифметические операции над несколькими числами, при этом, возможна также индикация промежуточных результатов. Формула изобретения 1. Отсчетное устройство, содержащее распределитель импульсов, первый выход которого подключен ко входу регистра сдвига, второй - ко входам управления блока ввода информации и блока индикации, третий - к первым входам элементов И группы, четвертый - к управляющему входу шифратора, первый информационный вход которого подключен к выходу блока ввода информации, выход .шифратора подключен к первому информационному входу сумматора, вторая группа информационных входов , . -,---- v . которого соединена с выходами элементов И группы, выход сумматора соединен, с первым входом блока индикаци.и и с информационным входом регистра, первый выход которого подключен ко вторым входам элеуек ов И группы, отличающееся тем, что, с нелью расширения диапазона исходных чисел и повышения достоверности, устройство содержит блок переноса, блок определения знака и блок контроля, первые управляющие входы которых подключены к пятому выходу распределителя, второй управляющий вход блока переноса подключен к управляющему входу щифратора, информационный вход блока переноса соединен с выходом сумматора, выход - с третьим входом сумматора, выход регистра соединен со входом блока контроля, второй вход блока -индикации соединен с выходом блока определения знака, выход сумматора соединен с первым входом блока определения знака, второй вход которого соединен со вторым информационным входом шифратора. 2. Устройство по П.1, отличающееся тем, что блок переноса содержит два триггера, выходы которых соединены соответственно с первым и вторым входами элементов И-ИЛИ, единичные входы триггеров соединены с информационным входом блока переноса, нулевой вход первого триггера и третий вход элемента И-ИЛИ подключены к первому управляющему входу блока переноса, нулевой вход второго триггера и четвертый в,ход элемента И-ИЛИ подключены ко второму управляющему входу блока переноса. 3 Устройство по П.1, отличающееся тем, что блок определения знака содержит первый и второй элементы И, выходы которых подключены ко входам триггера, выходы которого подключены к первому и второму входам элемента 2И-ИЛИ, третий вход которого подключен к управляющему входу блока определения знака, выход элемента 2И-ИЛИ подключен к выходу блока определения знака, первые входы первого и второго элементов И подключены к первому входу блока определения знака, второй вход которого соединен с четвертым входом элемента 2И-ИЛИ. 4. Устройство по П.1, отличающееся тем, что блок контроля содержит четырехразрядный двоичный сумматор, вход которого соединен со входом блока контроля, управляющий вход которого подключен к единичному входу триггера и первому входу элемента И, вторая группа входов которого подключена к выходу сумматора, выход элемента И подключен к нулевому входу триггера, выход которого подключен ко входу сумматора. Источники информации, принятые во внимание при экспертизе 1.Бабурин А. А. и ,др. Эксплуатация и техническое обслуживание электронных вычислительных машин М. «Энергия, 1973, с. 16-22. 2.Заявка 7 2031233/18-24 G 06 F 7/38, от 31.05.1974, по которой принято положительное рещение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Отсчетное устройство | 1975 |

|

SU614435A1 |

| Отсчетное устройство | 1976 |

|

SU734676A1 |

| Отсчетное устройство | 1974 |

|

SU548858A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Устройство аналого-цифрового преобразования | 1989 |

|

SU1647894A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| ЦИФРОВОЙ МОНИТОР | 2005 |

|

RU2292664C1 |

13

15

7«

Фиг. г

661548

IS

17

13

20

Авторы

Даты

1979-05-05—Публикация

1976-01-19—Подача