(54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

| Устройство для диагностирования шин | 1987 |

|

SU1444640A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Многоканальный формирователь одиночных импульсов | 1985 |

|

SU1243115A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2051416C1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

Изобретение относится к импульс- НОЙ технике и может быть использовано в измерительной цифровой аппаратуре и в устройствах с программным управлением для измерения .временных параметров электронных узлов.

Известен управляемый делитель частоты, содержащий входную шину,. двоичный счетчик на.триггерах, вентили, подключенные к шинам кода управления, элемент ИЛИ, шину Остановки двоичного счетчика в единичное состояние, соединенную с выходом элемента ИЛИ, один из входов, которого соединен со входом двоичного счетчикаul.

Недостатком известного устройст- ва является функциональная ненадежность, связанная с тем, что при включении ус,тройства триггеры счетчийа могут устанавливаться в любое из двух состояний случайным образом, первый входной импульс может не соответствовать: коду, установленному на входных шинах управления, вследствие чего на выходе устройства - возможно появление лишних импульсов.

Наиболее близким по технической сущности, к изобретению является устройство, содержащее генератор мпуль iCOB, выход которого соединен со счет-i

ным входом счетчика импульсов, выходы которого соединены с первыми входами элементов совпадения, вторые входы которых подключены к выходам блока памяти с блоком набора кода, а выходы - ко входам элемента И-НЕ; выход которого подключен кустановочному входу счетчика импульсов (|2J .

Недостатком известного делителя

10 частоты является, низкая надежность, так как в нем отсутствует возможность синхронно управлять работой счетчика и памятью.

Цель изобретения - повышение на15дежности работы устройства путем синхронного управления счетчиком и блоком памяти.

Поставленная цель достигается тем, что в управляемый делитель частоты,

20 содержащий N sjFieMeHTOB совпадения элемент И-НЕ, блок памяти, последовательно включенные генератор импульсов и счетчик импульсов, а также блок набора кода, выходы которого,

25 подключены к входам блока памяти, выходы которого подключены к первым входам N элементов совпадения, вторые входы которых подключены к выходам счетчика импульсов, а выходьк30 .к входам элемента И-НЕ, введены ин

вертор и элемент ИЛИ, первый вход которого соединен с шиной управления, второй вход - с выходом элемента И-НЕ а выход - с установочным входом счетчика импульсов, и входом инвертора, выход которого подключен к входу синхронизации блока памяти.

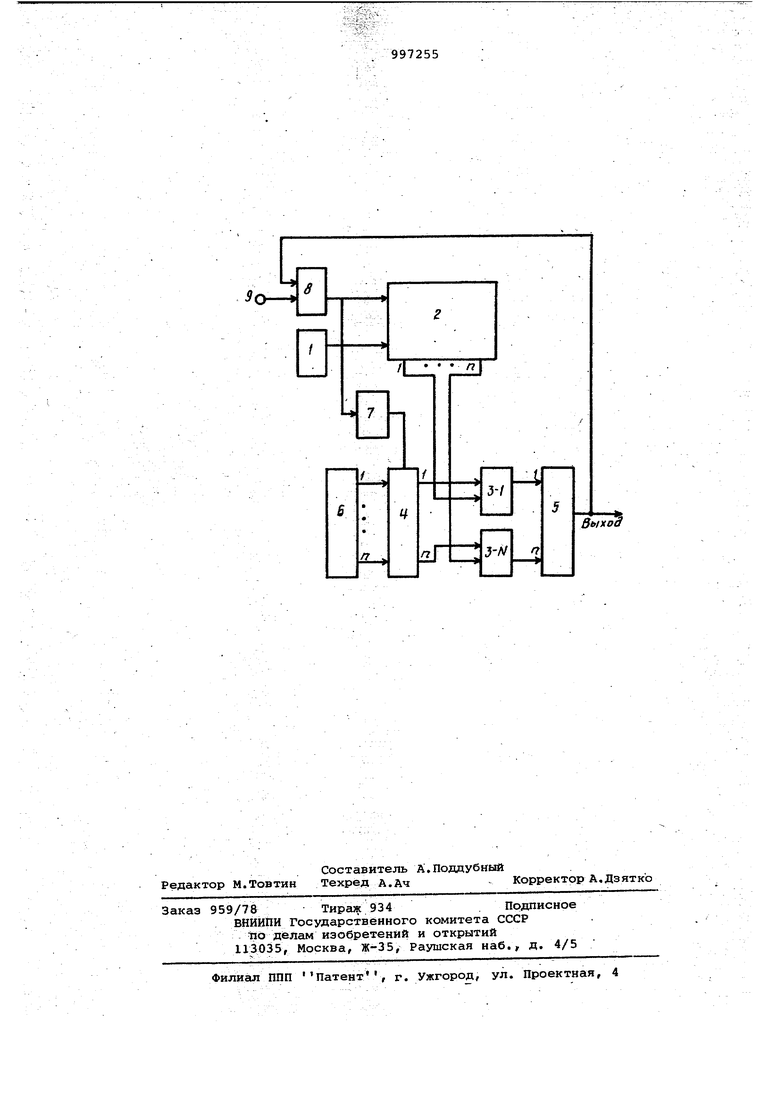

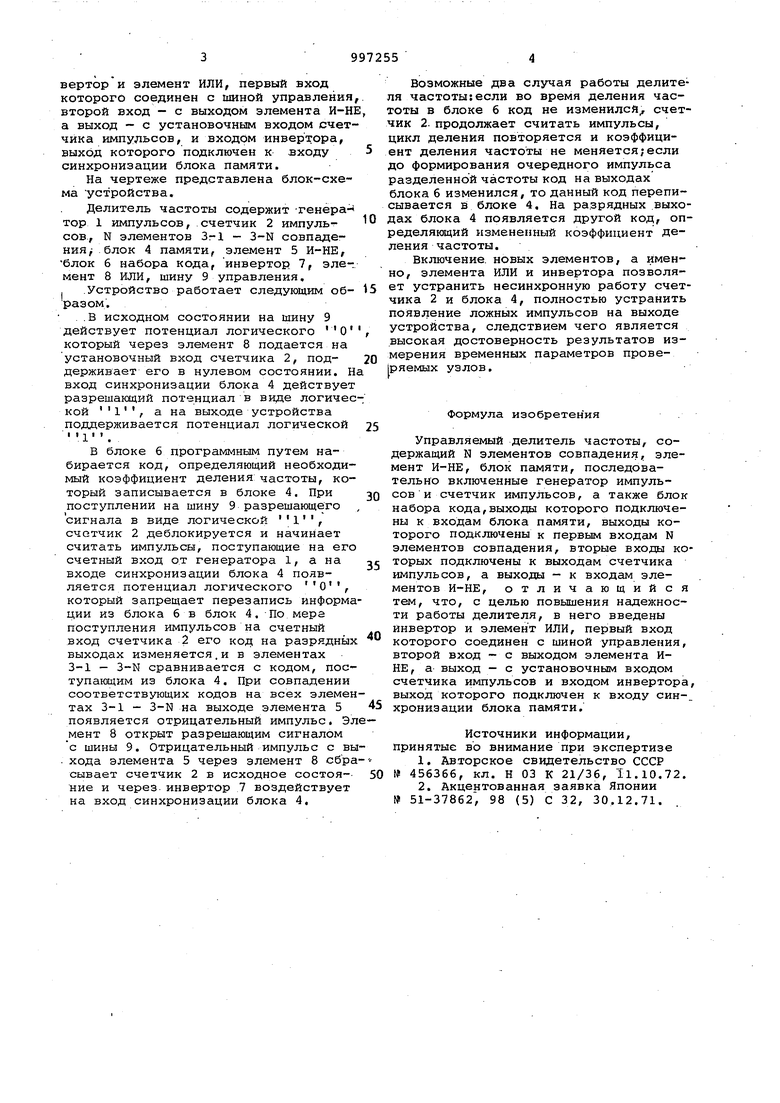

На чертеже представлена блок-схема устройства.

Делитель частоты содержит тенера- тор 1 импульсов, счетчик 2 импульсов, N элементов Зг-1 - 3-N совпадения/блок 4 памяти, элемент 5 И-НЕ, блок б набора кода, инвертор 7, элемент 8 ИЛИ, шину 9 управления, , .Устройство работает следующим образом.

.В исходном состоянии на шину 9 действует потенциал логического О который через элемент 8 подается на установочный вход счетчика 2, поддерживает его в нулевом состоянии. Н вход синхронизации блока 4 действует разрешающий потенциал в виде логической , а на выходе устройства поддерживается потенциал логической 1 .

В блоке 6 программным путем набирается код, определяющий необходимый коэффициент деления: частоты, который записывается в блоке 4, При поступлении на шину 9 разрешающего сигнала в виде логической , счетчик 2 деблокируется и начинает считать импульсы, поступающие на его счетный вход от генератора 1, а на входе синхронизации блока 4 появО

ляется потенциал логического

который запрещает перезапись информации из блока 6 в блок 4.-По мера поступления импульсов на счетный вход счетчика 2 его код на разрядных выходах изменяется.и в элементах 3-1 - 3-N сравнивается с кодом, поступающим из блока 4. При совпадении соответствующих кодов на всех элементах 3-1 - 3-N на выходе элемента 5 появляется отрицательный импульс. Элемент 8 открыт разрешающим сигналом с шины 9. отрицательный импульс с вы. хода элемента 5 через элемент 8 сбрасывает счетчик 2 в исходное состояние и через инвертор 7 воздействует на вход синхронизации блока 4,

Возможные два случая работы делителя частоты:если во время деления частоты в блоке 6 код не изменился счетчик 2. продолжает считать импульсы, цикл деления повторяется и коэффициент деления частоты не меняется;если до формирования очередного импульса разделенной частоты код на выходах блока 6 изменился, то данный код переписывается в блоке 4, На разрядных выходах блока 4 появляется другой код, определяющий измененный коэффициент деления частоты.

Включение, новых элементов, а именно, элемента ИЛИ и инвертора позволяет устранить несинхронную работу счетчика 2 и блока 4, полностью устранить появление ложных импульсов на выходе устройства, следствием чего является высокая достоверность результатов измерения временных параметров прове|ряемых узлов.

Формула изобретения .

Управляемый делитель частоты, содержащий N элементов совпадения, элемент И-НЕ, блок памяти, последовательно включенные генератор импульсов и счетчик импульсов, а также блок набора кода,выходы которого подключены к входам блока памяти, выходы которого подключены к первым входам N элементов совпадения, вторые входы которых подключены к выходам счетчика импульсов, а выходы - к входам элементов И-НЕ, отличающийся тем, что, с целью повышения надежности работы делителя, в него введены инвертор и элемент ИЛИ, первый вход которого соединен с шиной управления, второй вход - с выходом элемента ИНЕ, а выход - с установочным входом счетчика импульсов и входом инвертора выход которого подключен к входу синхронизации блока памяти.

Источники информации, принятые во внимание при экспертизе

№ 456366, кл. Н 03 К 21/36, 11.10.72.

8

о-

/ /7

Авторы

Даты

1983-02-15—Публикация

1981-04-08—Подача