(5) УСТРОЙСТВО ДЛЯ ОБСЛУЖИВАНИЯ ОБРАЩЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Устройство для управления обслужива-НиЕМ зАяВОК B пОРядКЕ пОСТуплЕНия | 1979 |

|

SU807297A1 |

| Устройство для программного управления | 1982 |

|

SU1108392A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

1

Изобретение относится к вычислительной технике, в частности к устройствам обработки обращений, и может быть использовано в коммутаторах внутреннего интерфейса в многопроцессорных вычислительных системах.

Известно устройство, содержащее регистры, триггеры занятости регистров, элементы И, ИЛИ { .

Недостатком этого устройства является низкое быстродействие, так как с бслуживание регистров осуществляется только после того, как обслужится канал с наивысшим приоритетом.

Наиболее близким к предлагаемому изобретению по технической сущности и достигаемому положительному эффекту является устройство для обслуживания запросов в порядке поступления, содержащее элементы И, группы элементов И, регистры, элементы ИЛИ, триггеры занятости Г2.

Недостатком данного устройства является низкая производительность. Целью изобретения является повышение производительности.

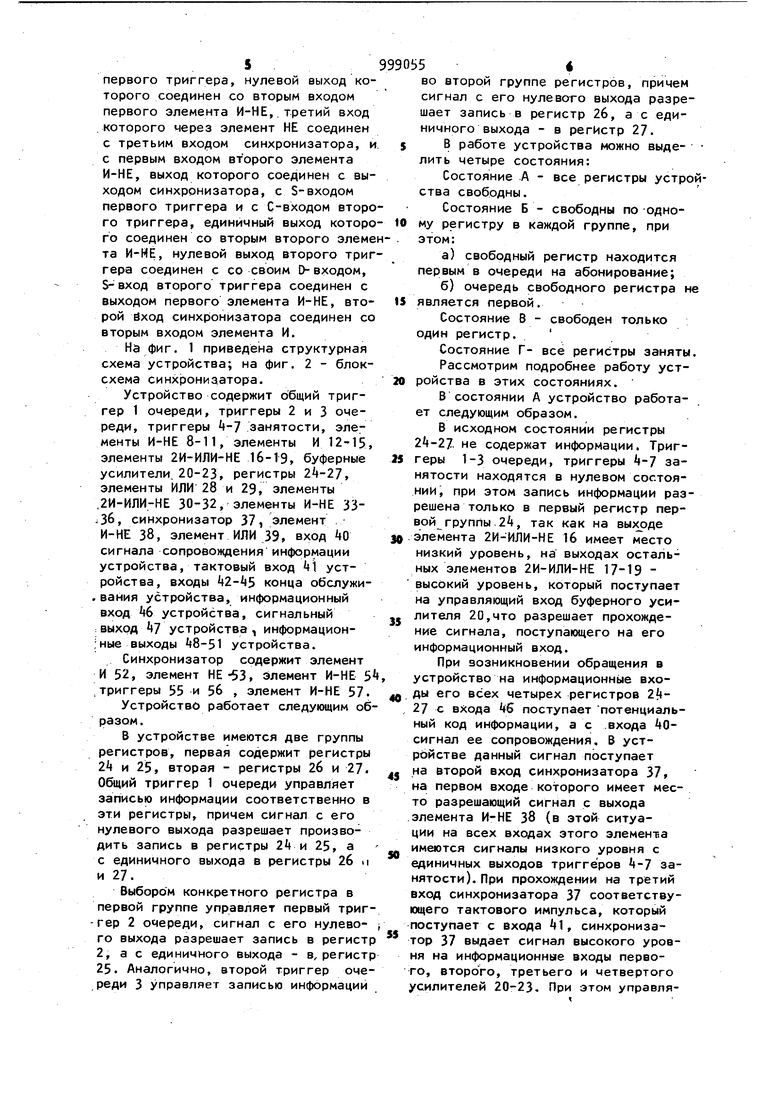

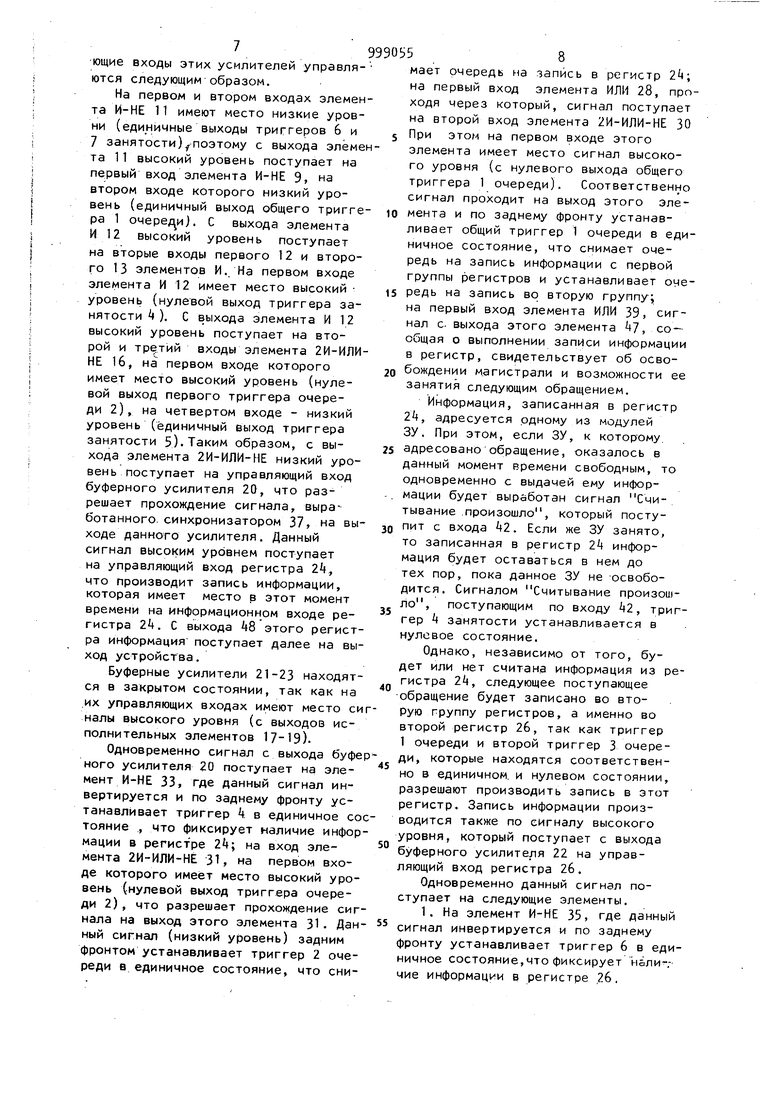

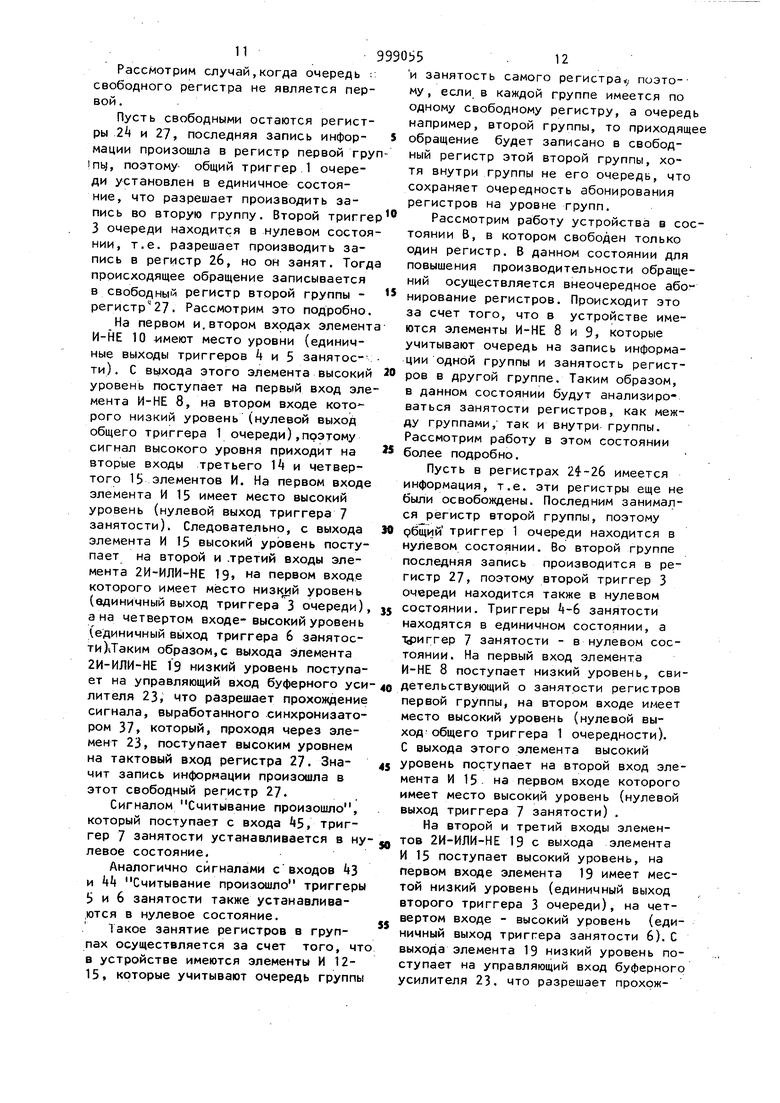

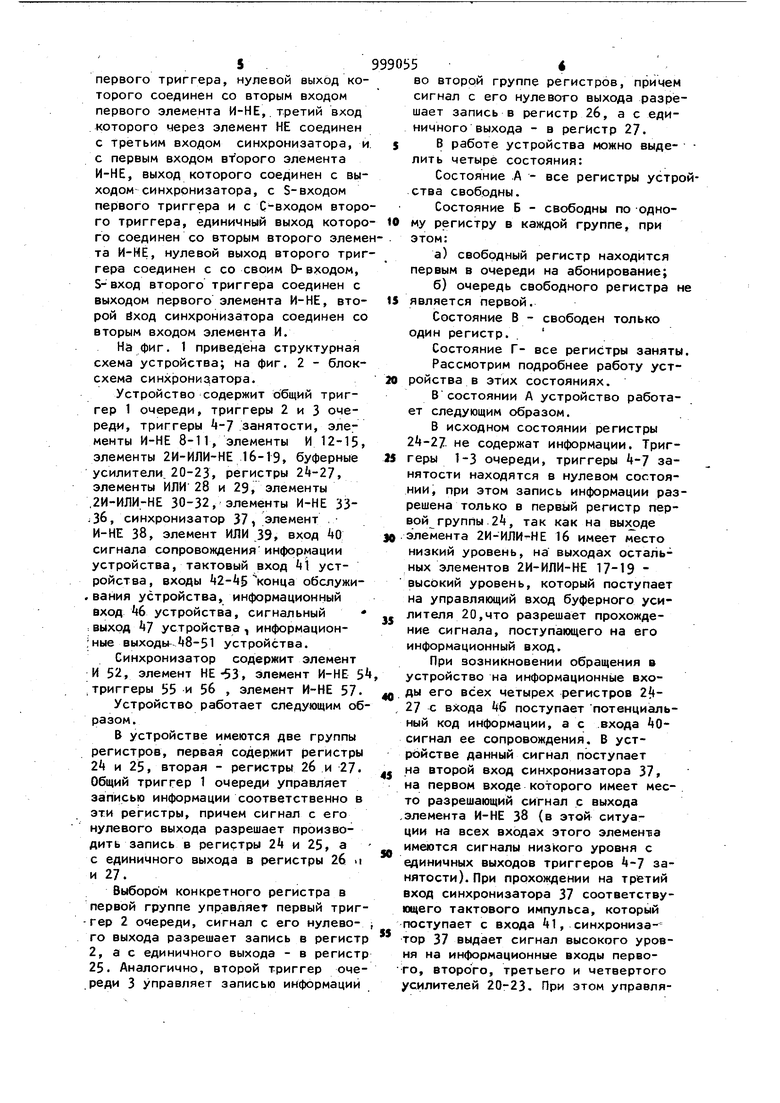

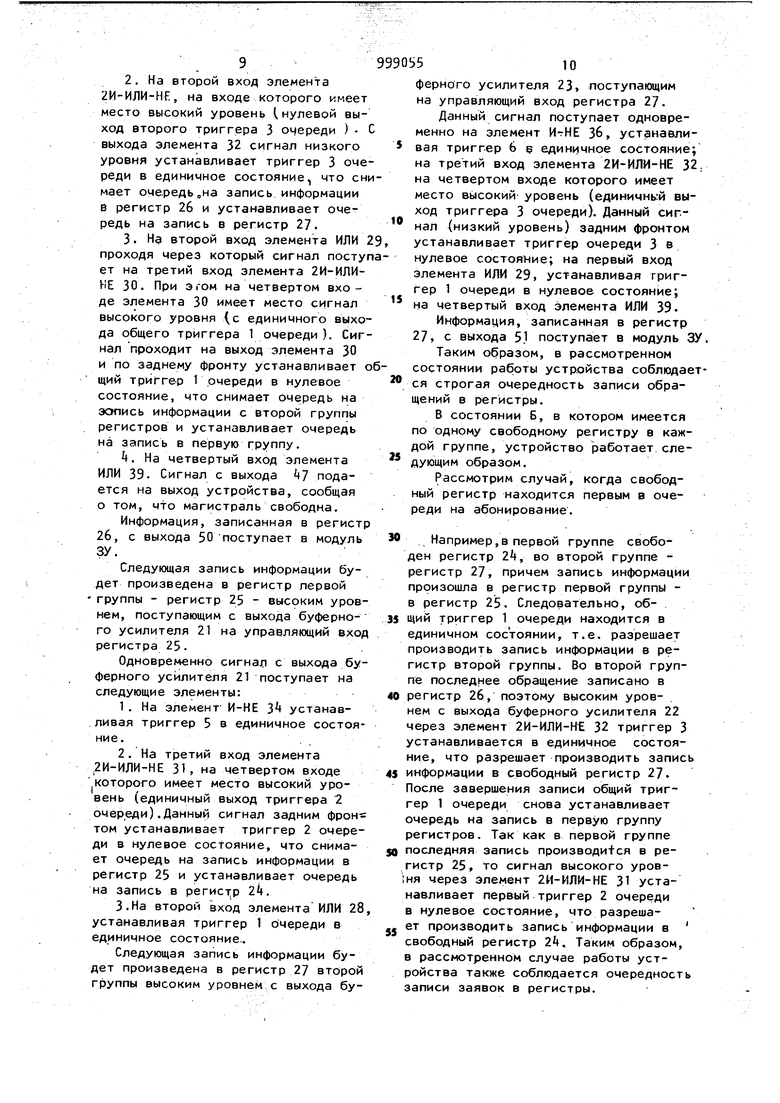

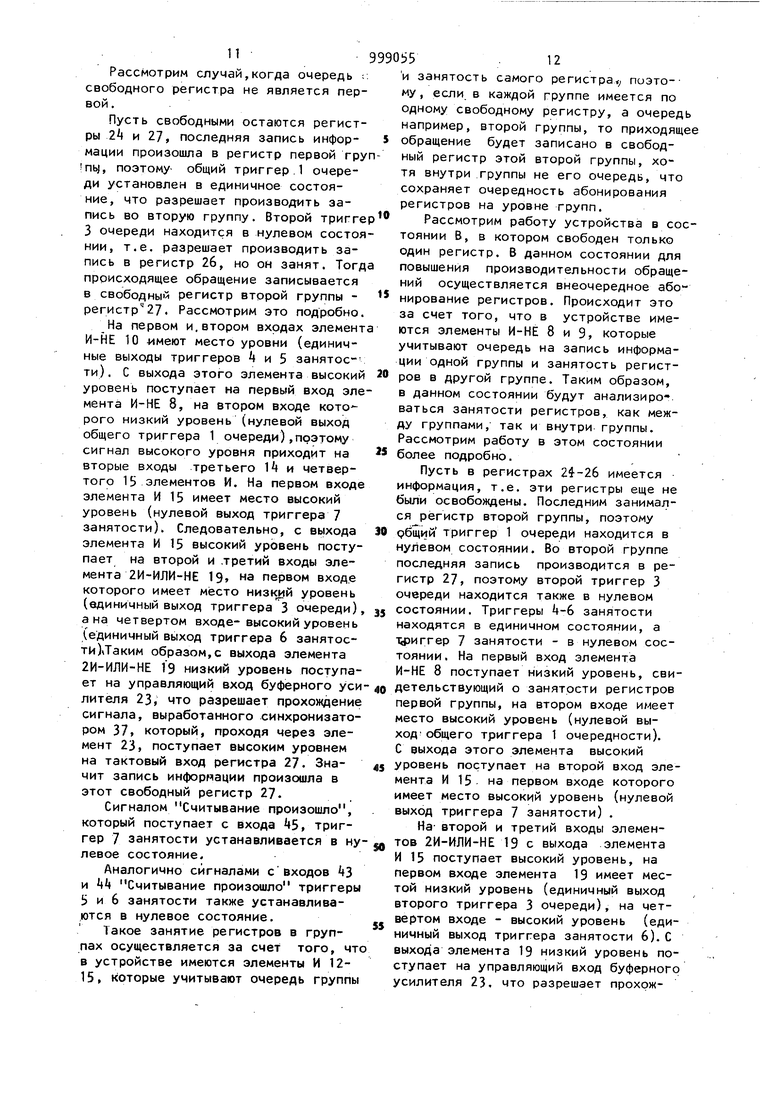

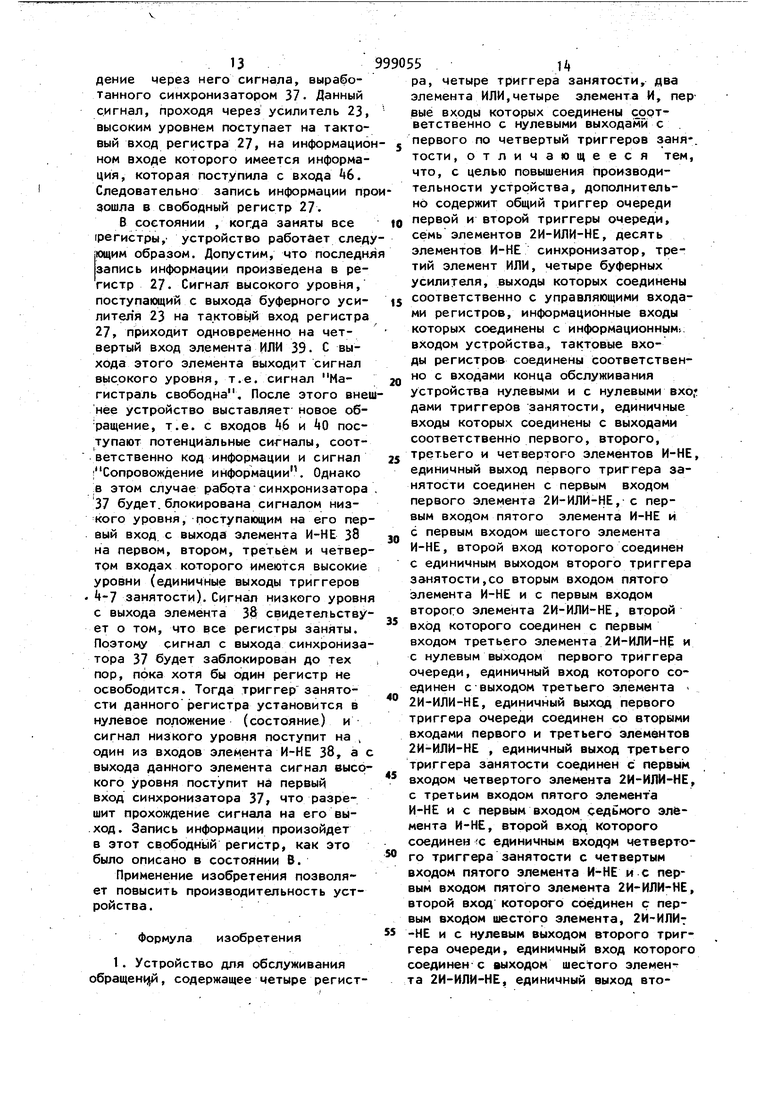

Поставленная цель достигается тем, что в устройство для обслуживания обращений, содержащее четыре регистра, четыре триггера занятости, два элемента ИЛИ, четыре элемента И, первые входы которых соединены соответственно с нулевыми выходами с первого по четвертый триггеров занятости, введены общий триггер очереди, первый и второй триггеры очереди, семь элементов 2И-ИЛИ-НЕ, десять элементов И-НЕ, синхронизатор, третий элемент ИЛИ, четыре )ерных усилителя, выходы которых соединены соответственно с управляющими входами 20 регистров, информационные входы котОЬых соединены с информационным входом /стройства, тактовые входы регистров соединены соответственно с входами конца обслуживания устройства и с нулевыми входами триггеров занятости, единичные входы которых соединены с выходами соответственно первого, второго, третьего и четвертого элементов , единичный выход первого триггера занятости соединен с первым входом первого элемента 2И ИЛИ-НЕ, с первым входом пятого, элемента И-НЕ и с первым входом шестого элемента И-НЕ, второй вход которого соединен с единичным выходом второго триггера занятости, со вторым входом пятого элемента И-НЕ и с первым входом второго элемента 2И- . ИЛИ-НЕ, второй вход которого соединен с первым входом третьего элемента 2И-ИЛИ-НЕ и с нулевым выходом первого триггера очереди, единичный .вход которо-г.о соединен с выходом третьего элемента 2И-ИЛИ-НЕ, единич ный выход первого триггера очереди соединен со вторыми входами первого и третьего элементов 2И-ИЛИ-НЕ, единичный выход третьего триггера занятости соединен с первым входом четвертого элемента 2И ИЛИ-НЕ, с ;Третьим входом пятого элемента И-НЕ и с первым входом седьмого эле1мента И-НЕ, второй вход которого соединен с единичным выходом четвер того триггера занятости с четвертым входом пятого элемента И-НЕ и с пер вым входом пятого элемента 2И-ИЛИвторой вход которого соединен с пер вым входом шестого элемента 2И-ИЛИНЕ и с нулевым выходом второго три гера очереди, единичный вход которого соединен с выходом шестого эле мента 2И-КЛИ-НЕ, единичный выход второго триггера очереди соединен со вторыми входами четвертого и шес того элементов 2И-ИЛИ-НЕ, вторые входы первого и второго элементов И соединены между собой и с выходом восьмого элемента И-НЕ; первый вхо которого соединен с выходом седьмого элемента И-НЕ, второй вход восьмого элемента И-НЕ соединен с первым входом седьмого элемента 2И-ИЛИ-НЕ и с единичным выходом общего триггера .очереди, единичный вход которого соединен с выходом седьмого элемента 2И-ИЛИ-НЕ, нулевой выход общего триггера очереди соединен со вторым входом седьмого элемента 2И-ИЛИ-НЕ и с первым входом девятого элемента И-НЕ, второй вход Которого соединен с выходом шестого элемента И-НЕ, выход девятого элемента И-НЕ соединен с первыми входами третьего и четвертого элементов И, выходы элементов И с первого по четвертый соединены соответственно с третьим и четвертым входами соответственно второго, первого, пятого и четвертого элементов 2И-ИЛИ-НЕ, выходы которых соединены с управляющими входами буферных усилителей,с первого по четвертый информационные входы которых соединены между собой и с выходом синхронизатора, первый вход которого соединен с выходом пятого элемента И-НЕ, второй вход синхронизатора соединен с входом сигнала сопровождение информации устройства,третий вход синхронизатора соединен с тактовым входом устройства, выход первого буферного усилителя соединен с первым входом первого элемента ИЛИ с входом Первого элемента И-НЕ с третьим входом третьего элемента, 2И-ИЛИ-НЕ, с первым входом второго элемента ИЛИ, выход которого соединен с третьим входом седьмого элемента 2И-ИЛИ-НЕ, второй вход второго элемента ИЛИ соединен с четвертым входом третьего элемента 2И-ИЛИ-НЕ, с входом второго элемента И-НЕ, со вторым входом первого элемента ИЛИ и с выходом второго буферного усилителя,выход третьего буферного усилителя соединен с третьим входом первого элемента ИЛИ, с входом третьего элемента И-НЕ, с 5ретьим входом шест го элемента 2И-ИЛИ-НЕ, и с первым входом третьего элемента ИЛИ, выход которого соединен с четвертым входом седьмого элемента 2И-ИЛИ-НЕ, второй вход третьего элемента ИЛИ соединен с четвертым входом шестого элемента 2И-ИЛИ-НЕ с входом четвертого элемента И-НЕ, с четвертым входом первого элемента И-НЕ и с выходом четвертого буферного усилителя, выход первого элемента ИЛИ является сигнальным выходом устройства, выходы первого, второго третьего и четвертого регистров являются информационными выходами устройства. Кроме того, синхронизатор содержит два элемента И-НЕ, элемент НЕ, элемент И и два триггера, причем первый вход синхронизатора соединен с первым входом элемента И, выход которого соединен с первым входом первого элемента И-НЕ и с R-входом первого триггера, нулевой выход которого соединен со вторым входом первого элемента И-НЕ,.третий вход которого через элемент НЕ соединен с третьим входом синхронизатора, и с первым входом второго элемента И-НЕ, выход которого соединен с выходом синхронизатора, с S-входом первого триггера и с С-входом второ го триггера, единичный выход которо го соединен со вторым второго элеме та И-НЕ, нулевой выход второго триг гера соединен с со своим О-входом, S-вход второго триггера соединен с выходом первого элемента И-НЕ, второй йход синхронизатора соединен со вторым входом элемента И. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - блоксхема синх(эониаатора. Устройство содержит общий три|- гер 1 очереди, триггеры 2 и 3 очереди, триггеры -7 занятости, элементы И-НЕ 8-11, элементы И 12-15, элементы 2И-ИЛИ-НЕ 16-19, буферные усилители. 20-23, регистры 24-27, элементы ИЛИ 28 и 29, элементы .2И-ИЛИ-НЕ 30-32, элементы И-НЕ 33j36, синхронизатор 37, элемент И-НЕ 38, элемент ИЛИ 39, входЧо сигнала сопровождения информации устройства, тактовый вход k устройства, входы конца обслужи,вания устройства, информационный вход k6 устройства, сигнальный :выход kj устройства , информацион;ные выходы tS-SI устройства. Синхронизатор содержит элемент И 52, элемент НЕ-53, элемент И-НЕ 5 триггеры 55 и 5б , элемент И-НЕ 57. Устройство работает следующим об разом. В устройстве имеются две группы регистров, первая содержит регистры 24 и 25, вторая - регистры 2б и 27. Общий триггер 1 очереди управляет записью информации соответственно в эти регистры, причем сигнал с его нулевого выхода разрешает производить запись в регистры 24 и 25, а с единичного выхода в регистры 26 ч и 27. Выбором конкретного регистра в первой группе управляет первый триг гер 2 очереди, сигнал с его нулевого выхода разрешает запись в регистр 2, а с единичного выхода - в, регистр 25. Аналогично, второй триггер очереди 3 управляет записью информации во второй группе регистров, причем сигнал с его нулевого выхода разрешает запись в регистр 2б, ас единичного выхода - в регистр 27. В работе устройства можно выде- лить четыре состояния: Состояние А - все регистры устройства свободны. Состояние Б - свободны по одному регистру в каждой группе, при этом: а)свободный регистр находится первым в очереди на абонирование; б)очередь свободного регистра не является первой. Состояние В - свободен только один регистр. Состояние Г- все регистры заняты. Рассмотрим подробнее работу устройства в этих состояниях. В состоянии А устройство работает следующим образом. В исходном состоянии регистры 24-27 не содержат информации. Триггеры 1-3 очереди, триггеры 4-7 занятости находятся в нулевом состоянии, при этом запись информации разрешена только в первый регистр первой группы. 24, так как на выходе элемента 2И-ИЛИ-НЕ 16 имеет место низкий уровень, на выходах остальных элементов 2И-ИЛИ-НЕ 17-19 высокий уровень, который поступает на управляющий вход буферного усилителя 20, что разрешает прохождение сигнала, поступающего на его информационный вход. При возникновении обращения в устройство на информационные входы его всех четырех регистров 2427 с входа 46 поступает потенциальный код информации, а с .входа 40сигнал ее сопровождения. В устройстве данный сигнал поступает на второй вход синхронизатора 37, на первом входе которого имеет место разрешающий сигнал с выхода элемента И-НЕ 38 (в этой ситуации на всех входах этого элементна имеются сигналы низкого уровня с единичных выходов триггеров 4-7 занятости). При прохождении на третий вход синхронизатора 37 соответствующего тактового импульса, который поступает с входа 41, синхронизатор 37 выдает сигнал высокого уровня на информационные входы первого, второго, третьего и четвертого усилителей 20-23, При этом управля7ющие входы этих усилителей управляются следующим образом. На первом и втором входах элемен та И-НЕ 11 имеют место низкие уровни (единичные выходы триггеров 6 и 7 занятости)у поэтому с выхода элеме та 11 высокий уровень поступает на первый вход элемента И-НЕ 9, на втором входе которого низкий уровень (единичный выход общего тригге ра 1 очере и). С выхода элемента И 12 высокий уровень поступает на вторые входы первого 12 и второго 13 элементов И. На первом входе элемента И 12 имеет место высокий уровень (нулевой выход триггера занятости ). С выхода элемента И 12 высокий уровень поступает на второй и третий входы элемента 2И-ИЛИ НЕ 16, на первом входе которого имеет место высокий уровень (нулевой выход первого триггера очереди 2), на четвертом входе - низкий уровень (единичный выход триггера занятости 5). Таким образом, с выхода элемента 2И-ИЛИ-НЕ низкий уровень поступает на управляющий вход буферного усилителя 20, что разрешает прохождение сигнала, выработанного, синхронизатором 37, на вы ходе данного усилителя. Данный сигнал высоким уровнем поступает на управляющий вход регистра 2, что производит запись информации, которая имеет место в этот момент времени на информационном входе регистра 2. С выхода 48 этого регист ра информация поступает далее на вы ход устройства. Буферные усилители 21-23 находят ся в закрытом состоянии, так как на .их управляющих входах имеют место с налы высокого уровня (с выходов исполнительных элементов 17-19). Одновременно сигнал с выхода буф ного усилителя 20 поступает на элемент И-НЕ 33, где данный сигнал инвертируется и по заднему фронту устанавливает триггер 4 в единичное с тояние ,, что фиксирует наличие инфо мации в регистре 24; на вход элемента 2И-ИЛИ-НЁ 31, на первом входе которого имеет место высокий уро вень (нулевой выход триггера очереди 2), что разрешает прохождение си нала на выход этого элемента 31. Да ный сигнал (низкий уровень) задним фронтом устанавливает триггер 2 оче реди в единичное состояние, что сни мает очередь на запись в регистр 24; на первый вход элемента ИЛИ 28, проходя через который, сигнал поступает на второй вход элемента 2И-ИЛИ-НЕ 30 При этом на первом входе этого элемента имеет место сигнал высокого уровня (с нулевого выхода общего триггера 1 очереди). Соответственно сигнал проходит на выход этого элемента и по заднему фронту устанавливает общий триггер 1 очереди в единичное состояние, что снимает очередь на запись информации с пербой группы регистров и устанавливает очередь на запись во вторую группу; на первый вход элемента ИЛИ 39, сигнал с. выхода этого элемента 47, сообщая о выполнении записи информации в регистр, свидетельствует об освобождении магистрали и возможности ее занятия следующим обращением. Информация, записанная в регистр 24, адресуется одному из модулей ЗУ. При этом, если ЗУ, к которому. адресовано обращение, оказалось в данный момент времени свободным, то одновременно с выдачей ему информации будет выработан сигнал Считывание .произошло, который поступит с входа 42. Если же ЗУ занято, то записанная в регистр 24 информация будет оставаться в нем до тех пор, пока данное ЗУ не освободится. Сигналом Считывание произошrio, поступающим по входу 42, триггер 4 занятости устанавливается в нулевое состояние. Однако, независимо от того, будет или нет считана информация из регистра 24, следующее поступающее обращение будет записано во вторую группу регистров, а именно во второй регистр 2б, так как триггер 1 очереди и второй триггер 3 очереди, которые находятся соответственно в единичном, и нулевом состоянии, разрешают производить запись в этот регистр. Запись информации производится также по сигналу высокого уровня, который поступает с выхода буферного усилителя 22 на управляющий вход регистра 2б. Одновременно данный сигнал поступает на следующие элементы. 1. На элемент И-НЕ 35, где данный сигнал инвертируется и по заднему фронту устанавливает триггер 6 в единичное состояние,что фиксирует нали-,чие информации в регистре ,2б. 2.На второй вход элемента 2И-ИЛИ-НЕ, на входе которого имеет место высокий уровень нулевой выход второго триггера 3 очереди ) выхода элемента 32 сигнал низкого уровня устанавливает триггер 3 оче реди в .единичное состояние, что сн мает очередь„на запись информации в регистр 26 и устанавливает очередь на запись в регистр 27. 3.На второй вход элемента ИЛИ проходя через который сигнал посту ет на третий вход элемента 2И-ИЛИНЕ 30. При этом на четвертом входе элемента 30 имеет место сигнал высокого уровня (с единичного выхо да общего триггера 1 очереди ). Сиг нал проходит на выход элемента 30 и по заднему фронту устанавливает щий тригге-р 1 очереди в нулевое состояние, что снимает очередь на эсгпись информации с второй группы регистров и устанавливает очередь на запись, в первую группу, k. На четвертый вход элемента ИЛИ 39. Сигнал с выхода подается на выход устройства, сообщая о том, что магистраль свободна. Информация, записанная в регист 2б, с выхода 50поступает в модуль ЗУ. Следующая запись информации будет произведена в регистр первой группы - регистр 25 - высоким уров нем, поступающим с выхода буферного усилителя 21 на управляющий Вхо регистра 25. Одновременно сигнал с выхода бу ферного усилителя 21 поступает на следующие элементы: 1 . На элемент И-НЕ З устанав.лишая триггер 5 в единичное состоя ние. 2. На третий вход элемента .2И-ИЛИ-НЕ 31, на четвертом входе .которого имеет место высокий уровень (единичный выход триггера 2 очереди).Данный сигнал задним фрон том устанавливает триггер 2 очере ди в нулевое состояние, что снимает очередь на запись информации в регистр 25 и устанавливает очередь на запись в регистр 2Ц. З.На второй вход элемента ИЛИ 2 устанавливая триггер 1 очереди в единичное состояние. Следующая запись информации будет произведена в регистр 27 второ группы высоким уровнем с выхода бу 5 ,10 ферного усилителя 23, поступающим на управляющий вход регистра 27. Данный сигнал поступает одновременно на элемент И-НЕ Зб, устанавливая триггер 6 е единичное состояние; на трет1)й вход элемента 2И-ИЛИ-НЕ 32. на четвертом входе которого имеет место высокий уровень (единичный выход триггера 3 очереди). Данный сигнал (низкий уровень) задним фронтом устанавливает триггер очереди 3 в нулевое состояние; на первый вход элемента ИЛИ 29, устанавливая триггер 1 очереди в нулевое состояние; на четвертый вход элемента ИЛИ 39. Информация, записанная в регистр 27, с выхода 51 поступает в модуль ЗУ. Таким образом, в рассмотренном состоянии работы устр.ойства соблюдается строгая очередность записи обращений в регистры. В состоянии Б, в котором имеется по одному свободному регистру в каждой группе, устройство работает следующим образом. Рассмотрим случай, когда свободный регистр находится первым в очереди на абонирование. Например,в первой группе свободен регистр 2, во второй группе регистр 27, причем запись информации произошла в регистр первой группы в регистр 25. Следовательно, общий триггер 1 очереди находится в единичном состоянии, т.е. разрешает производить запись информации в регистр второй группы. Во второй группе последнее обращение записано в регистр 2б, поэтому высоким уровнем с выхода буферного усилителя 22 через элемент 2И-ИЛИ-Н 32 триггер 3 устанавливается в единичное состояние, что разрешает производить запись информации в свободный регистр 27. После завершения записи общий три1- гер 1 очереди снова устанавливает очередь на запись в первую группу регистров. Так как в первой группе последняя запись пpoизвoдиfcя в регистр 25, то сигнал высокого уровня через элемент 2И-ИЛИ-НЕ 31 устанавливает первый триггер 2 очереди в нулевое состояние, что разрешает производить запись информации в свободный регистр 24, Таким образом, в рассмотренном случае работы устройства также соблюдается очередность записи заявок в регистры. Рассмотрим случай,когда очередь ; свободного регистра не является первой . Пусть свободными остаются регистры 2 и 27, последняя запись информации произошла в регистр первой гру )пь|, поэтому- общий триггер.1 очереди установлен в единичное состояние, что разрешает производить запись во вторую группу. Второй тригге 3 очереди находится в нулевом состоя нии, т.е. разрешает производить запись в регистр 2б, но он занят. Тогд происходящее обращение записывается в свободный регистр второй группы регистр 27. Рассмотрим это подробно. На первом и.втором входах элемент И-НЕ 10 1меют место уровни (единичные выходы триггеров 4 и 5 занятоети). С вь1хода этого элемента высокий уровень поступает на первый вход эле мента И-НЕ 8, на втором входе которого низкий уровень (нулевой выход общего триггера 1 очереди),поэтому сигнал высокого уровня приходит на вторые входы третьего Т и четвертого 15 элементов И. На первом входе элемента И 15 имеет место высокий уровень (нулевой выход триггера 7 занятости). Следовательно, с выхода элемента И 15 высокий уровень поступает на второй и .третий входы элемента 2И-ИЛИ-НЕ 19 чэ первом входе которого имеет место низкий уровень (единичный выход триггера 3 очереди), а на четвертом входе-высокий уровень (единичный выход триггера 6 занятоети)Таким образом,с выхода элемента 2И-ИЛИ-НЕ 19 низкий уровень поступает на управляющий вход буферного уси лителя 23, что разрешает прохождение сигнала, выработанного синхронизатором 37, который, проходя через элемент 23, поступает высоким уровнем на тактовый вход регистра 27. Значит запись информации произошла в этот свободный регистр 27. Сигналом Считывание произошло, который поступает с входа 5, триггер 7 занятости устанавливается в ну левое состояние, Аналогично сигналами с входов 43 и kk Считывание произошло триггеры 5 и 6 занятости также устанавливаются в нулевое состояние. Такое занятие регистров в группах осуществляется за счет того, чт в устройстве имеются элементы И 1215, которые учитывают очередь группы 5 . 12 и занятость самого регистра / поэто- му, если, в каждой группе имеется по одному свободному регистру, а очередь например, второй группы, то приходящее обращение будет записано в свободный регистр этой второй группы, хотя внутри группы не его очередь, что сохраняет очередность абонирования регистров на уровне групп. Рассмотрим работу устройства в состоянии В, в котором свободен только один регистр. В данном состоянии для повышения производительности обращений осуществляется внеочередное або нирование регистров. Происходит это за счет того, что в устройстве имеются элементы И-НЕ 8 и 9, которые учитывают очередь на запись информации одной группы и занятость регистров в другой группе. Таким образом, в данном состоянии будут анализироваться занятости регистров, как между группами, так и внутри группы. Рассмотрим работу в этом состоянии более подробно. Пусть в регистрах имеется информация, т.е. эти регистры еще не были освобождены. Последним занимался регистр второй группы, поэтому рбщий триггер 1 очереди находится в нулевом состоянии. Во второй группе последняя запись производится в регистр 27, поэтому второй триггер 3 очереди находится также в нулевом состоянии. Триггеры -6 занятости находятся в единичном состоянии, а Тёриггер 7 занятости - в нулевом состоянии. На первый вход элемента И-НЕ 8 поступает низкий уровень, свидетельствующий о занятости регистров первой группы, на втором входе имеет место высокий уровень (нулевой выход общего триггера 1 очередности). С выхода этого элемента высокий уровень поступает на второй вход элемента И 15 на первом входе которого имеет место высокий уровень (нулевой выход триггера 7 занятости) . На второй и третий входы элементов 2И-ИЛИ-НЕ 19с выхода элемента И 15 поступает высокий уровень, на первом входе элемента 19 имеет местой низкий уровень (единичный выход второго триггера 3 очереди), на четвертом входе - высокий уровень (единичный выход триггера занятости 6). С выхода элемента 19 низкий уровень поступает на управляющий вход буферного усилителя 23. что разрешает прохржпервого триггера, нулевой выход которого соединен со вторым входом первого элемента И-НЕ,.третий вход которого церез элемент НЕ соединен с третьим входом синхронизатора, и с первым входом второго элемента И-НЕ, выход которого соединен с выходом синхронизатора, с S-входом первого триггера и с С-входом второ го триггера, единичный выход которо го соединен со вторым второго элеме та И-НЕ, нулевой выход второго триг гера соединен с со своим D-входом, S-вход второго триггера соединен с выходом первого элемента И-НЕ, второй бход синхронизатора соединен со вторым входом элемента И. На фиг. 1 приведена структурная схема устройства; на фиг, 2 - блоксхема си HXJDOHH затора. Устройство содержит общий триггер 1 очереди, триггеры 2 и 3 очереди, триггеры -7 занятости, элементы И-НЕ 8-11, элементы И 12-15, элементы 2И-ИЛИ-НЕ 16-19, буферные усилители. 20-23, регистры , элементы ИЛИ 28 и 29, элементы ,2И-ИЛИ-НЕ 30-32, элементы И-НЕ 33:3б, синхронизатор 37, элемент . И-НЕ 38, элемент ИЛИ 39, вход 40 сигнала сопровожденияинформации устройства, тактовый вход ti устройства, входы конца обслужи,вания устройства, информационный вход устройства, сигнальный :выход 7 устройства , информацион;ные выходы- 8-51 устройства. Синхронизатор содержит элемент И 52, элемент НЕ-53, элемент И-НБ 5 триггеры 55 и 5б , элемент И-НЕ 57. Устройство работает следующим об разом. В устройстве имеются две группы регистров, первая содержит регистры 2k и 25, вторая - регистры 2б и 27. Общий триггер 1 очереди управляет записью информации соответственно в эти регистры, причем сигнал с его нулевого выхода разрешает производить запись в регистры 2k и 25, а с единичного выхода в регистры 2б i и 27. Выбором конкретного регистра в первой группе управляет первый триг -гер 2 очереди, сигнал с его нулевого выхода разрешает запись в регистр 2, а с единичного выхода - в регистр 25. Аналогично, второй триггер очереди 3 управляет записью информации ВО второй группе регистров, причем сигнал с его нулевого выхода разрешает запись в регистр 26, а с единичного выхода - в регистр 27. В работе устройства можно выде- лить четыре состояния: Состояние .А - все регистры устройства свободны. Состояние Б - свободны по одному регистру в каждой группе, при этом: а)свободный регистр находится первым в очереди на абонирование; б)очередь свободного регистра не является первой. Состояние В - свободен только один регистр. . Состояние Г- все регистры заняты. Рассмотрим подробнее работу устройства в этих состояниях. В состоянии А устройство работает следующим образом. В исходном состоянии регистры не содержат информации. Триггеры 1-3 очереди, триггеры 4-7 занятости находятся в нулевом состоянии, при этом запись информации разрешена только в первый регистр первой группы 24, так как на выходе элемента 2И-ИЛИ НЕ 16 имеет место низкий уровень, на выходах остальных элементов 2И-ИЛИ-НЕ 17-19 высокий уровень, который поступает на управляющий вход буферного усилителя20,что разреш ает прохождение сигнала, поступающего на его информационный вход. При возникновении обращения в устройство на информационные входы его всех четырех регистров 2k 27 входа 46 поступает потенциальный код информации, ас .входа 40сигнап ее сопровождения. В устрЬйстве данный сигнал поступает на второй вход синхронизатора 37 на первом входе которого имеет место разрешающий сигнал с выхода элемента И-НЕ 38 (в этой ситуации на всех входах этого элемен-ра имеется сигналы низкого уровня с единичных выходов триггеров 4-7 занятости). При прохождении на третий вход синхронизатора 37 соответствующего тактового импульса, который поступает с входа 41, синхрониза- тор 37 выдает сигнал высокого уровня на информационные входы первого, второго, третьего и четвертого усилителей 20-23, При этом управля7. 9

ющие входы этих усилителей управля- ются следующим образом.

На первом и втором входах элемента И-НЕ 11 имеют место низкие уровни (единичные выходы триггеров 6 и 7 занятости)поэтому с выхода элемента 11 высокий уровень поступает на первый вход элемента И-НЕ 9, на втором входе которого низкий уровень (единичный выход общего триггеpa 1 очере/ и). С выхода элемента И 12 высокий уровень поступает на вторые входы первого 12 и второго 13 элементов И. На первом входе элемента И 12 имеет место высокий уровень (нулевой выход триггера занятости ), С выхода элемента И 12 высокий уровень поступает на второй и третий входы элемента 2И-ИЛИНЕ 16, на первом входе которого имеет место высокий уровень (нулевой выход первого триггера очереди 2),. на четвертом входе - низкий уровень (единичный выход триггера занятости 5.). Таким образом, с выхода элемента 2И-ИЛИ-НЕ низкий уровень поступает на управляющий вход буферного усилителя 20, что разрешает прохождение сигнала, выработанного синхронизатором 37, на выходе данного усилителя. Данный сигнал высоким уровнем поступает на управляющий вход регистра 24, что производит запись информации, которая имеет место в этот момент времени на информационном входе регистра 2k. С выхода 8 этого регистра информация поступает далее на выход устройства.

Буферные усилители 21-23 находятся В закрытом состоянии, так как на .их управляющих входах имеют место синалы высокого уровня (с выходов исполнительных элементов ).

Одновременно сигнал с выхода буфе ного усилителя 20 поступает на элемент И-НЕ 33,- где данный сигнал инвертируется и по заднему фронту устанавливает триггер k в единичное сотояние , что фиксирует наличие информации а регистре на вход элемента 2И-ИЛИ-НЕ 31, на первом входе которого имеет место высокий уровень (нулевой выход триггера очереди 2) , что разрешает прохождение сигнала на выход этого элемента 31. Дан ный сигнал (низкий уровень) задним фронтом устанавливает триггер 2 очереди в единичное состояние, что сни58

мает очередь на запись в регистр 24; на первый вход элемента ИЛИ 28, проходя через которь1й, сигнал поступает на второй вход элемента 2И-ИЛИ-НЕ 30 При этом на первом входе этого элемента имеет место сигнал высокого уровня (с нулевого выхода общего триггера 1 очереди). Соответственно сигнал проходит на выход этого элемента и по заднему фронту устанавливает общий триггер 1 очереди в единичное состояние, что снимает очередь на запись информации с первой группы регистров и устанавливает очередь на запись во вторую группу; на первый вход элемента ИЛИ 39, сигнал с. выхода этого элемента 47, сообщая о выполнении записи информации в регистр, свидетельствует об освобождении магистрали и возможности ее занятия следующим обращением.

Информация, записанная в регистр 24, адресуется одному из модулей ЗУ. При этом, если ЗУ, к которому, адресовано обращение, оказалось в данный момент времени свободным, то одновременно с выдачей ему информации будет выработан сигнал Счи-. тывание .произошло, который поступит с входа 42. Если же ЗУ занято, то записанная в регистр 24 информация будет оставаться в нем до тех пор, пока данное ЗУ не освободится. Сигналом Считывание произошло, поступающим по входу 42, триггер 4 занятости устанавливается в нулевое состояние.

Однако, независимо от того, будет или нет считана информация из регистра 24, следующее поступающее обращение будет записано во вторую группу регистров, а именно во второй регистр 2б, так как триггер 1 очереди и второй триггер 3 очереди, которые находятся соответственно в единичном, и нулевом состоянии, разрешают производить запись в этот регистр. Запись информации производится также по сигналу высокого уровня, который поступает с выхода буферного усилителя 22 на управляющий вход регистра 2б.

Одновременно данный сигнал поступает на следующие элементы.

41

J7

tH ff6

/i

Zfy

hW

1

Ш

t-/7

J/

1±E

je

а±и

u

38

J

w

Й/г./

Авторы

Даты

1983-02-23—Публикация

1981-07-03—Подача