Изобретение относится к вычислительной технике, предназначено для последовательного сложения чисел, представленных кодами золотой пропорции, и может быть использовано в специализированных вычислительных устройствах с повышенной достоверностью обработки информации.

Известен последовательный сумматор кодов с иррациональными основаниями, содержащий одноразрядный сумматор, регистр, элемент задержки и блок формирования дополнительных сигналов суммы и переноса [1] .

Недостатком устройства является низкая контролепригодность из-за недостаточного использования ошибкообнаруживающих свойств кодов золотой пропорции.

Наиболее близким по технической сущности к изобретению является последовательный сумматор, содержащий блок свертки, блок контроля свертки, блок перемещения, блок контроля перемещения и одноразрядный сумматор, причем первый и второй входы слагаемых соединены с входами одноразрядного сумматора, выход которого соединен с первым информационным входом блока перемещения, выход сигналов перемещения, второй и третий информационные входы которого соединены соответственно с первым информационным входом, прямым информационным выходом блока свертки и с информационным выходом блока контроля перемещения, информационный вход которого соединен с контрольным выходом блока перемещения, второй информационный вход и контрольный выход блока свертки соединены соответственно с информационными выходом и входом блока контроля свертки, контрольные выходы блоков контроля перемещения и свертки соединены соответственно с выходами ошибок перемещения и свертки последовательного сумматора, выход суммы которого является старшим разрядом прямого информационного выхода блока свертки, второй управляющий вход блока контроля перемещения соединен с третьим управляющим входом блока перемещения и входом контроля перемещения последовательного сумматора, вход разрешения перемещения которого соединен с вторым управляющим входом блока перемещения, вход начальной установки последовательного сумматора соединен с первыми управляющими входами блока свертки и блоков контроля перемещения и свертки, тактовый вход последовательного сумматора соединен с первым управляющим входом блока перемещения и вторым управляющим входом блока свертки, первый управляющий вход которого соединен с вторым управляющим входом блока контроля свертки и входом контроля свертки последовательного сумматора, вход разрешения свертки которого соединен с третьим управляющим входом блока свертки [2] .

Недостатком устройства является низкое быстродействие, обусловленное последовательным выполнением во время операций перемещения и свертки их контроля, а также тем, что длительность каждого такта работы сумматора равна времени формирования j-го разряда суммы при наиболее тяжелой кодовой ситуации.

Целью изобретения является увеличение быстродействия последовательного сумматора за счет совмещения во времени операции перемещения (свертки) кодов золотой пропорции с контролем предыдущей операции и организации цикла работы сумматора переменной длительности с анализом условия окончания операции формирования j-го разряда суммы.

Цель достигается тем, что в последовательный сумматор, содержащий одноразрядный сумматор, блок перемещения, блок контроля перемещения, блок свертки, блок контроля свертки, причем первый и второй входы слагаемых соединены с входами одноразрядного сумматора, выход которого соединен с первым информационным входом блока перемещения, выход сигналов перемещения, второй и третий информационные входы которого соединены соответственно с первым информационным входом, прямым информационным выходом блока свертки и с информационным выходом блока контроля перемещения, информационный вход которого соединен с контрольным выходом блока перемещения, второй информационный вход и контрольный выход блока свертки соединены соответственно с информационными выходом и входом блока контроля свертки, контрольные выходы блоков контроля перемещения и свертки соединены соответственно с выходами ошибок перемещения и свертки последовательного сумматора, выход суммы которого является старшим разрядом прямого информационного выхода блока свертки, введен блок микропрограммного управления, семь входов которого соединены соответственно с входом синхронизации слагаемых, первым и вторым тактовыми входами, входом запуска, входом числа циклов, входом запроса результата последовательного сумматора и с инверсным информационным выходом блока перемещения, три управляющих входа которого соединены соответственно с четвертым, пятым и шестым выходами блока микропрограммного управления, первые два выхода которого являются соответственно выходами синхронизации суммы и запроса слагаемых последовательного сумматора, выход состояния которого является третьим выходом блока микропрограммного управления и соединен с первыми управляющими входами блока свертки и блоков контроля перемещения и свертки, вторые управляющие входы которых соединены соответственно с четвертым, шестым и восьмым выходами блока микропрограммного управления, седьмой и восьмой выходы которого также соединены соответственно с третьим и четвертым управляющими входами блока свертки.

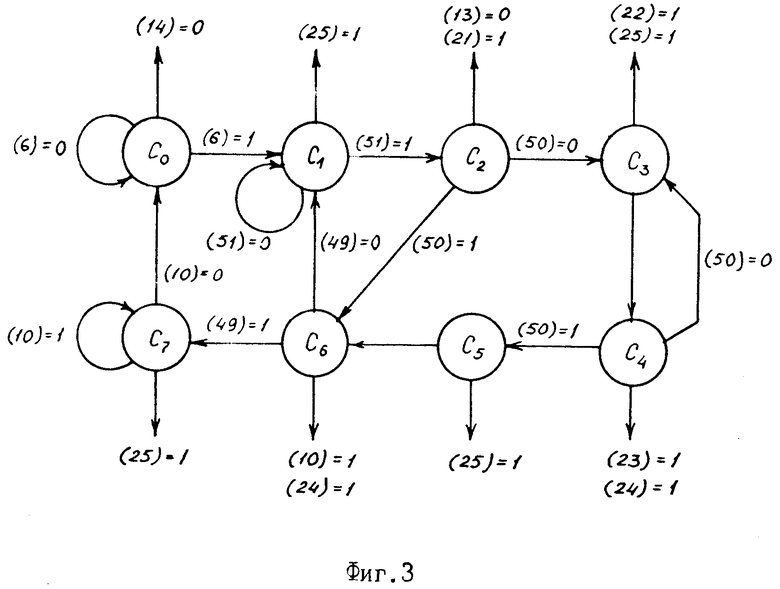

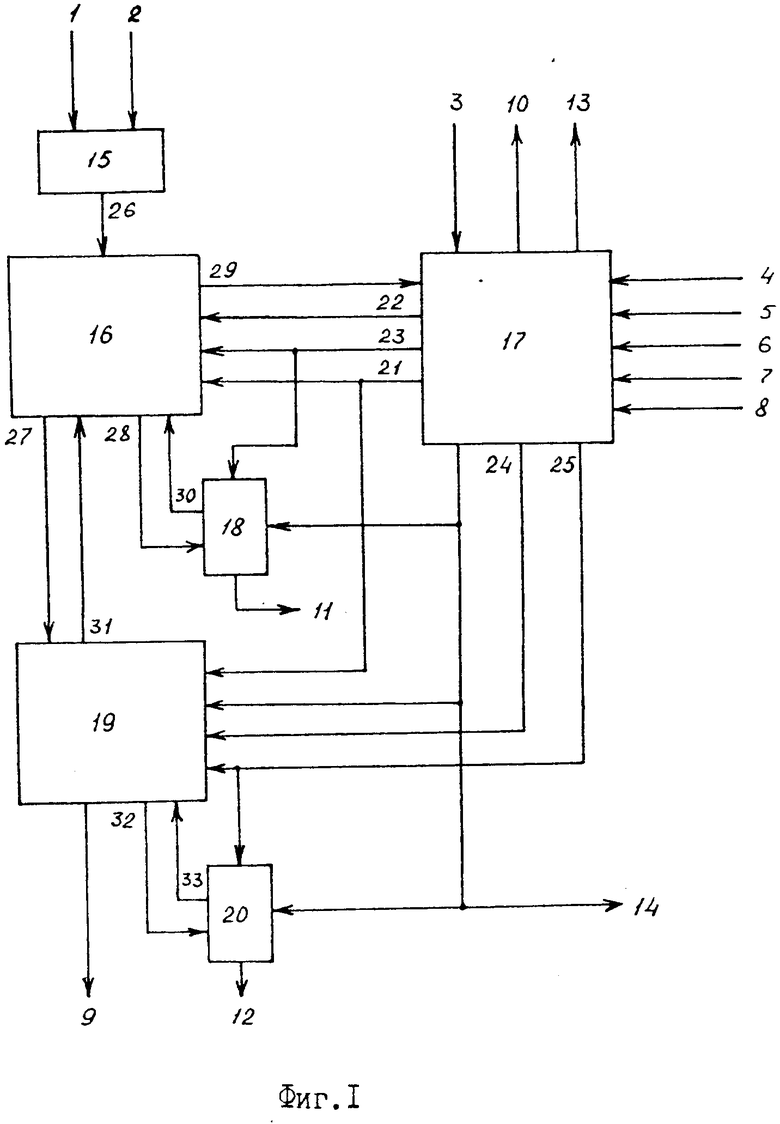

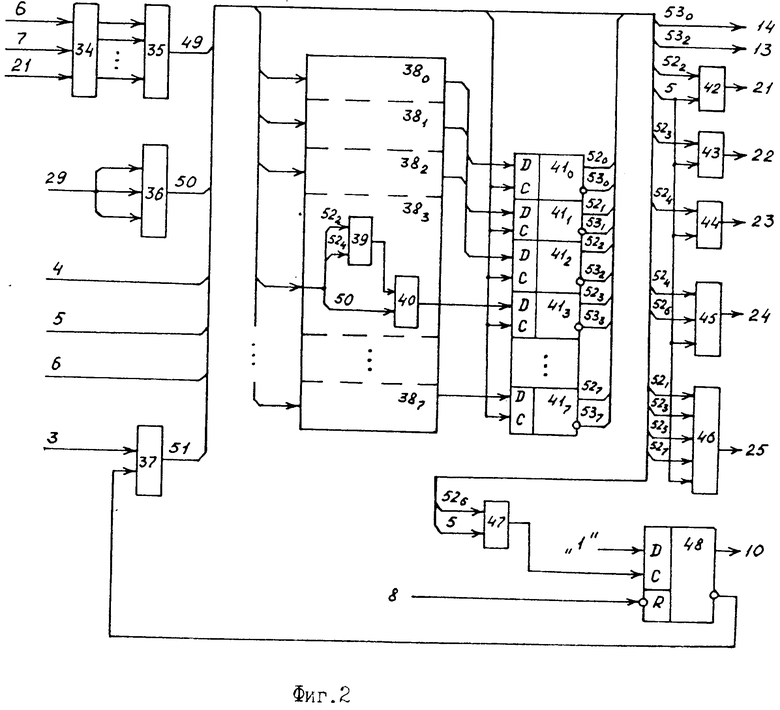

На фиг. 1 представлена схема последовательного сумматора; на фиг. 2 - пример построения блока микропрограммного управления; на фиг. 3 - граф состояний и переходов блока микропрограммного управления.

Последовательный сумматор (фиг. 1) содержит входы 1 и 2 первого и второго слагаемых, вход 3 синхронизации слагаемых, первый и второй тактовые входы 4 и 5, вход 6 запуска, вход 7 числа циклов, вход 8 запроса результата, выход 9 суммы, выход 10 синхронизации суммы, выход 11 ошибки перемещения, выход 12 ошибки свертки, выход 13 запроса слагаемых, выход 14 состояния последовательного сумматора, одноразрядный сумматор 15 с выходом 26, блок 16 перемещения с выходом 27 сигналов перемещения, контрольным выходом 28, инверсным информационным выходом 29, блок 17 микропрограммного управления с выходами 21 записи, 22 перемещения, 23 контроля перемещения, 24 свертки, 25 контроля свертки, блок 18 контроля перемещения с информационным выходом 30, блок 19 свертки с прямым информационным выходом 31 и контрольным выходом 32, блок 20 контроля свертки с информационным выходом 33.

Блок 17 микропрограммного управления (фиг. 2) содержит счетчик 34, элементы И 35, 36, 37, 42, 43, 44, 47, элементы И-ИЛИ 45, 46, восьмиразрядный узел 38 установки, в каждом i-м разряде которого реализуется логическая функция V f

f Cji, где ni - число состояний Cji блока 17, из которых возможен переход в состояние Ci, восьмиразрядный регистр 41 состояний с прямыми 52 и инверсными 53 выходами, триггер 48, выходы 49-51 элементов И. На фиг. 2 показан пример реализации разряда 383 узла 38, который содержит элемент ИЛИ 39 и элемент И 40.

Cji, где ni - число состояний Cji блока 17, из которых возможен переход в состояние Ci, восьмиразрядный регистр 41 состояний с прямыми 52 и инверсными 53 выходами, триггер 48, выходы 49-51 элементов И. На фиг. 2 показан пример реализации разряда 383 узла 38, который содержит элемент ИЛИ 39 и элемент И 40.

На графе состояний и переходов (фиг. 3) обозначены состояния блока 17, логические функции fji переходов и сигналы, формируемые на выходах блока 17 в каждом из состояний.

Блоки 15, 16, 18, 19, 20 аналогичны этим блокам в прототипе. Дополнительный выход 29 блока 16 перемещения соединен с инверсными выходами трехразрядного регистра блока 16. Одноразрядный сумматор 15 предназначен для сложения двух цифр слагаемых, представленных в кодах золотой пропорции. Блок 16 перемещения предназначен для выполнения операции перемещения над кодами, хранящимися в блоках 16 и 19. Блок 18 контроля перемещения предназначен для контроля правильности выполнения операции перемещения. Блок 19 свертки предназначен для выполнения операции свертки над кодом, хранящимся в блоке 19. Блок 20 контроля свертки предназначен для контроля правильности выполнения операции свертки.

Последовательный сумматор работает следующим образом.

При нахождении блока 17 в состоянии Со на выходе 14 находится нулевой потенциал, обнуляющий регистры в блоках 18, 19 и 20 и означающий, что последовательный сумматор готов к работе. При появлении сигнала "Пуск" ((6) = 1) блок 17 переходит в состояние С1, а в счетчик 34 записывается число n + 3 циклов работы сумматора, где n - разрядность мантиссы слагаемых. Изменение состояния блока 17 путем установки в "1" того или иного разряда регистра 41 происходит по синхросигналам, поступающим на первый тактовый вход 4.

Формирование набора управляющих сигналов блоком 17 микропрограммного управления для вычисления каждой цифры результата происходит при последовательном переходе блока 17 из состояния С1 в состояние С6 в соответствии с графом состояний и переходов.

В состоянии С1 блок 17 формирует управляющий сигнал контроля свертки ((25) = = 1), по которому в блоке 20 осуществляется контроль правильности выполнения операции свертки при вычислении предыдущей цифры суммы аналогично тому, как это делается в прототипе. При обнаружении ошибки формируется единичный сигнал на выходе 12 ошибки свертки. Управляющий сигнал на выходе 25 является логической функцией сигналов на выходах 521, 523, 525 и 527 регистра 41 состояний и синхросигнала на входе 5 последовательного сумматора. Временной сдвиг между синхросигналами на входах 4 и 5 равен максимальному времени между появлением сигнала на С-входе регистра 41 и установкой новых значений сигналов на его выходах. При наличии на входе 3 сигнала синхронизации слагаемых и нулевом значении на выходе 10 синхронизации суммы блок 17 переходит в состояние С2. При этом формируются управляющие сигналы на выходе 13 ((13) = 0), информирующий о захвате очередных разрядов слагаемых, и на выходе 21 ((21) = 1), по которому осуществляется запись суммы с выхода 26 одноразрядного сумматора 15 в блок 16 перемещения, сдвиг на один разряд в сторону старших разрядов содержимого регистра блока 19 свертки и вычитание единицы из счетчика 34.

Если сумма очередных разрядов слагаемых, записанная в блок 16, не равна нулю ((50) = 0), то блок 17 микропрограммного управления переходит в состояние С3. При этом вырабатываются сигналы разрешения перемещения ((22) = 1). По сигналу разрешения перемещения блоком 16 выполняется операция перемещения над трехразрядным кодом, хранящимся в регистре блока 16, и тремя младшими разрядами кода, хранящегося в регистре блока 19, аналогично тому, как это сделано в прототипе. Кроме того, сигналы о выполнении операции перемещения поступают с выхода 28 блока 16 в блок 18 контроля перемещения, устанавливая в "1" соответствующие разряды регистра контроля.

Затем блок 17 переходит в состояние С4, в котором формируются сигналы разрешения свертки ((24) = 1) и контроля перемещения ((23) = 1). По сигналу разрешения свертки выполняется операция свертки над шестиразрядным кодом, хранящимся в регистре блока 19. Сигналы о выполнении операции свертки поступают с выхода 32 блока 19 в блок 20 контроля свертки, устанавливая в "1" соответствующие разряды регистра контроля. По сигналу контроля перемещения в блоке 18 осуществляется контроль правильности выполнения этой операции с выдачей сигнала об ошибке на выход 11 последовательного сумматора.

Если после выполнения операции перемещения содержимое регистра блока 16 равно нулю ((50) = 1), то блок 17 переходит в состояние С5, в котором вырабатывается сигнал контроля свертки, а затем в состояние С6. При этом вырабатывается сигнал разрешения свертки, после выполнения которой на выходе 9 сумматора формируется очередная цифра суммы, которая сопровождается сигналом синхронизации суммы ((10) = 1). Если содержимое счетчика 34 не равно нулю ((49) = 0), то блок 17 из состояния С6 переходит в состояние С1 и начинается цикл вычисления очередной цифры суммы. Если содержимое счетчика 34 равно нулю, блок 17 переходит в состояние С7, в котором формируется сигнал контроля свертки. Блок 17 находится в состоянии С7 до тех пор, пока внешним сигналом на входе 8 не будет сброшен сигнал синхронизации суммы ((10) = 0). Это означает, что полученная цифра суммы передана для дальнейшей обработки. Из состояния С7 блок 17 переходит в состояние Со, и процесс сложения заканчивается.

Таким образом, изобретение позволяет повысить как минимальное, так и среднее быстродействие последовательного сумматора по сравнению с сумматором-прототипом. (56) 1. Авторское свидетельство СССР N 1170449, кл. G 06 F 7/49, 1983.

2. Авторское свидетельство СССР N 1691835, кл. G 06 F 7/49, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор | 1989 |

|

SU1691835A1 |

| Сумматор кодов с иррациональным основанием | 1991 |

|

SU1837279A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1986 |

|

SU1339551A1 |

| Устройство для последовательного деления | 1986 |

|

SU1304017A1 |

| Устройство для умножения | 1983 |

|

SU1200280A1 |

| Устройство для умножения | 1981 |

|

SU997031A1 |

| Устройство для деления | 1983 |

|

SU1151955A1 |

| Параллельный сумматор кодов фибоначчи | 1984 |

|

SU1180880A1 |

| Сумматор кодов Фибоначчи | 1981 |

|

SU981993A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах с повышенной достоверностью обработки информации. Целью изобретения является увеличение быстродействия сумматора. Это достигается тем, что последовательный сумматор, содержащий одноразрядный сумматор, блоки перемещения, свертки, контроля перемещения и свертки и функциональные связи, снабжен блоком микропрограммного управления и дополнительными функциональными связями, что позволяет увеличить минимальное и среднее быстродействие соответственно в 1,7 и 2,8 раза и более с сохранением контролеспособности сумматора. 3 ил.

ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР, содержащий одноразрядный сумматор, трехразрядный блок перемещения, блок контроля перемещения, шестиразрядный блок свертки и блок контроля свертки, причем первый и второй входы слагаемых последовательного сумматора соединены соответственно с входами одноразрядного сумматора, выход которого соединен с первым информационным входом блока перемещения, второй и третий информационные входы которого соединены соответственно с прямым информационным выходом блока свертки и с информационным выходом блока контроля перемещения, информационный вход которого соединен с контрольным выходом блока перемещения, информационный выход которого соединен с первым информационным входом блока свертки, второй информационный вход которого соединен с информационным выходом блока контроля свертки, информационный вход которого соединен с контрольным выходом блока свертки, контрольные выходы блока контроля перемещения и блока контроля свертки соединены соответственно с выходами ошибок перемещения и свертки последовательного сумматора, выход суммы которого соединен со старшим разрядом прямого информационного выхода блока свертки, отличающийся тем, что, с целью повышения быстродействия, в него введен блок микропрограммного управления, первый вход которого соединен с входом синхронизации слагаемых последовательного сумматора, первый и второй тактовые входы которого соединены соответственно с вторым и третьим входами блока микропрограммного управления, четвертый, пятый и шестой входы которого соединены соответственно с входами запуска, числа циклов и запроса результата последовательного сумматора, седьмой вход которого соединен с инверсным информационным выходом блока перемещения, первый и второй выходы блока микропрограммного управления являются соответственно выходом синхронизации суммы и выходом запроса слагаемых последовательного сумматора, выход состояния которого соединен с третьим выходом блока микропрограммного управления и с первыми управляющими входами блока свертки, блока контроля перемещения и блока контроля свертки, второй управляющий вход блока свертки соединен с первым управляющим входом блока перемещения и с выходом записи блока микропрограммного управления, выход сигнала перемещения которого соединен с вторым управляющим входом блока перемещения, третий управляющий вход которого соединен с вторым управляющим входом блока контроля перемещения и с выходом контроля перемещения блока микропрограммного управления, выход свертки которого соединен с третьим управляющим входом блока свертки, четвертый управляющий вход которого соединен с вторым управляющим входом блока контроля свертки блока микропрограммного управления.

Авторы

Даты

1994-01-30—Публикация

1991-01-08—Подача