вания сумматора, отличающее с я тем, что, с целью повышения быстродействия, в него введены регистр частичного произведения, четвертый блок контроля и коммутатор причем выход произведения сумматора соединен с информационным входом регистра частичного произведения, вход разрешения записи информации которого соединен с седьмым выходом программного блока управления, одиннадцатый выход которого соединен с входом разрешения записи сдвинутых переносов сумматора, информационный вход которого соединен с выходом коммутатора, первый информационный вход которого соединен с шиной логического нуля устройства, второй, третий, четвертый и пятый информационные входы коммутатора соединены с выходом регистра множимого, выход ре200280

гистра частичного произведения соединен с входом четвертого блока контроля и шестым информационным входом.. коммутатора, седьмой и восьмой информационные входы которого соединены- с выходом регистра обратного кода множимого, выход четвертого младшего разряда регистра множителя соединен с четвертым информационньм входом табличного умножителя, выход адреса канала которого соединен с управляющим входом коммутатора, а выходы формирования каналов с адресами 110 или 111 и канала с адресом 111 соединены соответственно с восьмыми девятым входами программно-.го блока управления, второй, двенадцатый и четвертый выходы которого соединены соответственно с входами блокировки и сдвига табличного умножителя и входом сдвига сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1986 |

|

SU1339551A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения | 1988 |

|

SU1615706A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее регистр множимого, регистр множителя, регистр обратного кода множимого, три блока контроля, блок преобразования золотого 1-кода множимого в обратный код, элемент И, табличный умножитель, программный блок управления и сз шатор, причем входы прямого золотого 1-кода множимого, инверсного значения золотого 1.-кода множимого и прямого золотого 1-кода множителя устройства соединены соответственно с информационными входа- , ми регистров множимого, обратного кода множимого и множителя, выходы Которых соединены соответственно с входами первого, второго и третьего блоков контроля, выходы которых по схеме монтажного ИЛИ соединены с первым входом программного блока управления и первым входом элемента И, выход которого соединен с выходом ошибки устройства, входы Пуск и синхронизации которого соединены с вторым и третьим входами программного блока управления. первый выход которого соединен с вторым входом элемента И, входы разрешения записи информации регистров множимого, обратного кода множимого и. множителя и блока преобразования золотого 1-кода множимого в обратный код соединены с вторым выходом программного блока управления, третий выход которого соединен с входом разрешения записи частично нормализованной информации регистра обратного кода множимого, вход, частично нормализованной информации которого соединен с выходом блока преобразования золотого 1-кода множимого в обратный код, информационный вход которого сое(Л динен с выходом регистра обратного кода множимого, выходы трех младших разрядов регистра множителя соединены с первыми тремя информационными входами табличного умножителя, а вход сдвига соединен с входом разрешения записи переноса табличного умножителя и четвертьм входом программного блока управления, четвертый и пятый входы которого соединены соответственно с выходами формирования конца нормализации и суммирования сумматора, входы ..разрешения записи кода множимого, частично нормализованной промежуточной суммы и вход сброса сумматора .соединены соответственно с пятым, шестым и седьмым выходами программного блока управления, восьмой, девятый и десятый выходы которого соединены соответственно с входами разрешения записи переноса, разрешения коррекции и разрешения суммиро

Изобретение относится к вычислительной технике, предназначено для умножения многоразрядных золотых 1-кодов, позволяет умножать как целое, так и дробные числа за счет умножения множимого одновременно на четыре разряда множителя, и может быть использовано в отказоустойчивых процессорах обработки данных.

Цель изобретения - повьшение быстродействия.

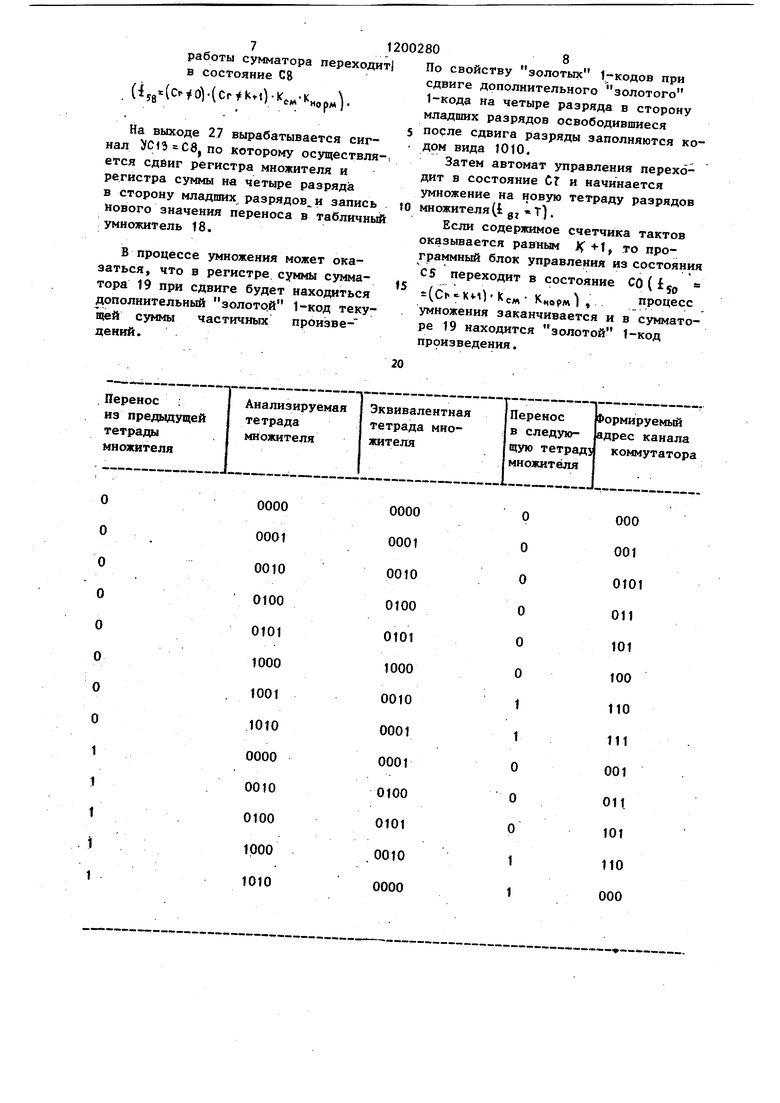

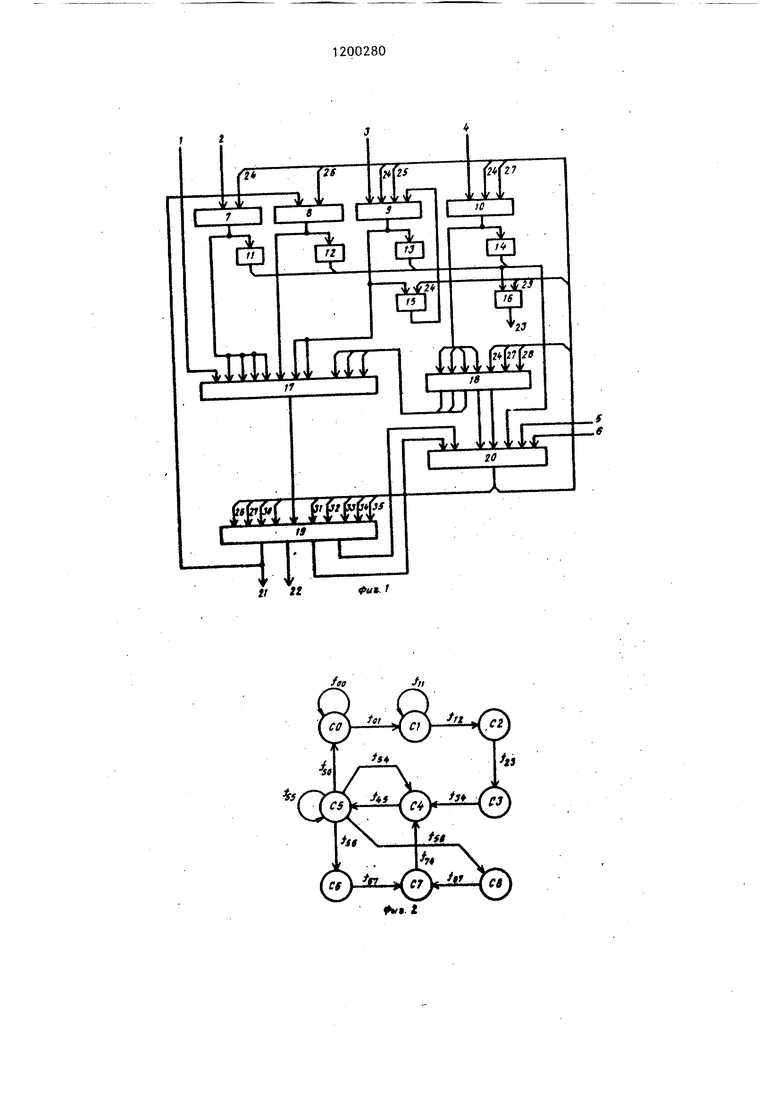

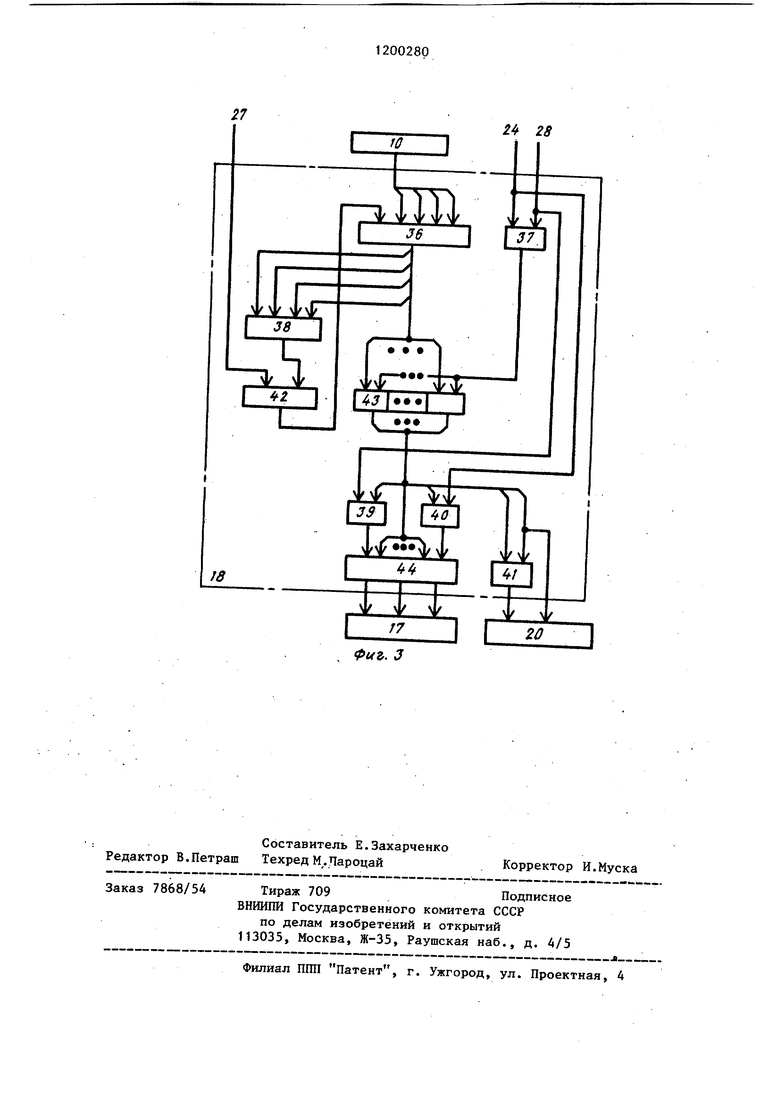

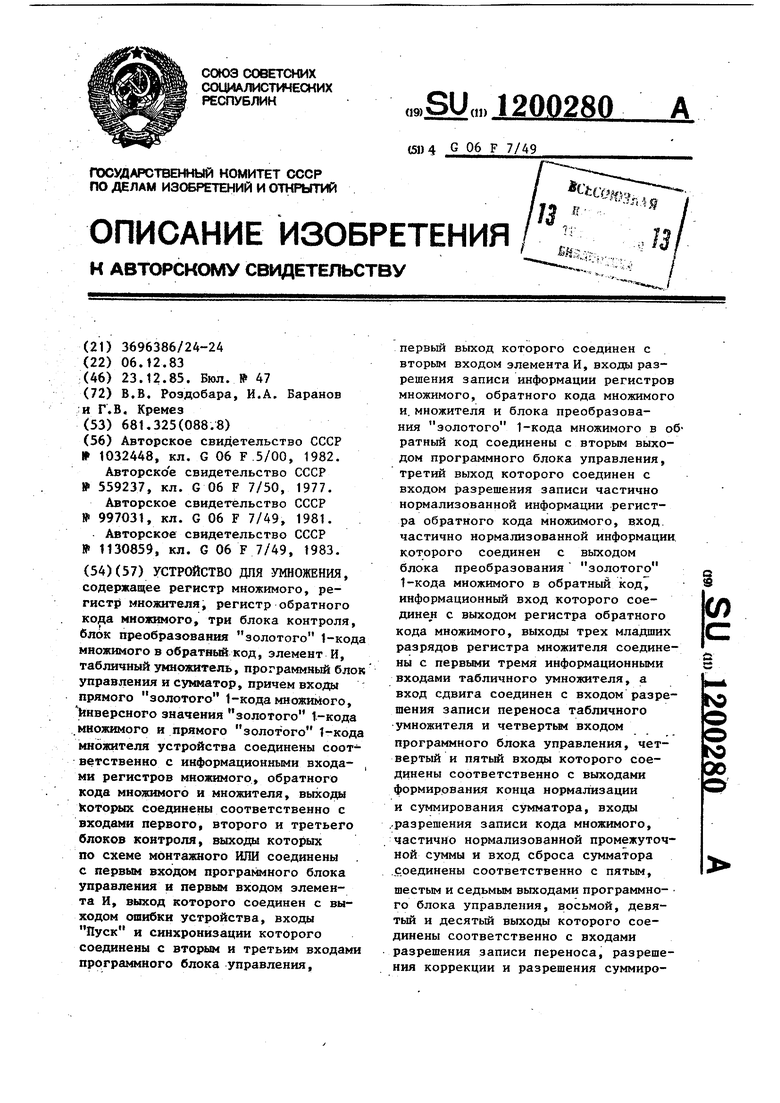

На фиг. 1 представлена схема устройстваJ на фиг. 2 - граф состояний и переходов блока программного управленияJ на фиг. 3 - один из вариантов реализации схемы табличного умножителя.

Устройство для умножения (фиг. 1) содержит входы 1-6 устройства, регистр 7 множимого, регистр 8 частичного произведения, регистр 9 обратного кода множимого, регистр 10 множителя, блоки 11-14 контроля, блок 15 преобразования золотого 1-кода множимого в обратный код, элемент И 16, коммутатор 17, табличный умножитель 18, сумматор 19, программны блок 20 управления, выход 21 произведения устройства, выход 22 ошибки сумматора устройства, выход 23 ошибки устройства, выходы 24-35 программного блока управления устройства.

На графе состояний и переходов программного блока управления (фиг. 2) изображены состояния автомата управления СЗ , J 0,1,..., и функции ijj переходов из состояния Cj в состояние CJ.

Табличный умножитель 18 (фиг. 3) может в частном случае содержать неполный дешифратор 36, элемент .ИЛИ-НЕ 37, элементы ИЛИ 38-41, триггер 42, группу элементов И 43, шифратор 44.

Регистр 7 множимого предназначен для хранения золотого 1-кода множимого, регистр 8 - для хранения частичного произведения ( oi +1).А, где А - код множимого, регистр 9 для хранения обратного кода произведения oi, А, регистр 10 множимого 10-для храненияи сдвига на четыре разряда золотого 1-кода множителя.

Блоки контроля 11-14 предназначены для контроля регистров 7-10 на нормальность хранимой информации, г.е. отсутствие единиц в двух соредних разрядах золотого 1-кода.

Блок 15 преобразования предназначен для образования обратного золотого 1-кода произведения Л, А, элемент И 16 - для управления шиной выходов блоков контроля 11-14, коммутатор 17 - для управления пропуском соответствующих частичных произведечий на сумматор, табличньй умножитель 18 - для управления коммутатором 17 в зависимости от значений анализируемых разрядов множителя.

Сумматор 19 предназначен Для сложения очередных частичных произведений с текущей суммой частичны произведений по правилам золотой 1-системы счисления, программный блок 20 управления - для управления работой устройства.

Устройство работает следующим образом.

Рассмотрим случай умножения прямых h -разрядных золотых 1-кодов причем будем считать, что знак произведения формируется отдельно, а число информационных разрядов (я-1) кратно четырем.

Перед началом умножения про- ,. граммный блок управления находится в состоянии C0( пуск).

Для выполнения умножения на входы устройства подается следующая информация: на вход 1 - О, на вход 2 - прямой золотой 1-код множимого, на вход 3 - инверсное значение сдвинутого на один разряд влево золотого 1-кода множимого, на вход 4 - прямой золотой 1-код множителя, на вход 5 - сигнал Пуск на вход 6 - серия синхроимпульсов ГО, по которой тактируются переходы программного блока управления из одного состояния в другое.

По сигналу Пуск программный блок управления переходит в состояние Cl(f|j, пуск), в котором на выходе 24 вырабатывается управляющий сигнал YCX С 1 . По переднему фронту этого сигнала осуществляется запись информации в регистрах 7, 10.

Для получения правильного результата умножения регистры 7-9, блоки 11-13 контроля, блок 15 преобразования, коммутатор 17 и сумматор 19 имеют четыре дополнительных старших разряда Кроме того, регистр 9 имеет два вспомогательных младших разряда, причем

последние не являются информационными и используются только для повышения точности образования обратного кода произведения «, А. При записи в регистр 9 они устанавливаются в единицу.,

Образование обратного золотого 1-кода произведения Л А осуществляется блоком 15 преобразования

0 по известному алгоритму. По управ.ляющему сигналу VC2 & ГО поступающему на вход 25, осуществляется запись частично нормализованного обратного 1-кода произведения с, А

5 в регистр 9. После окончания нормализации кода в регистре 9 с выходов блоков контроля на вход блока управления поступает сигнал окончания нормализации К„(,рм,° которому

0 автомат управления переходитв состояние С2, (4 К i

V-IZ 11 ЧОрМ I

При переходе программного блока управления в состояние С2 в блоке . 5 управления на выходе 29 формируется

сигнал СЗ COvcT открывающий, элемент И 16, через который сигналы об ошибках из блоков 11-14 контроля поступают на выход 23 устройства. Блоки 11-14 контроля реализуют функцию ошибки

Л)(., J

где OIJ - значение i -го разряда

регистра. Далее осуществляется образование частичного произведения ( otf -ь1)А. Для этого в состоянии CJ сигнал YCf Cf с выхода 24 поступает в

табличный умножитель 18. По этому сигналу блокировки на его выходе образуется адрес коммутатора, соответствующий пропуску через коммутатор на вход сумматора 1-кода множимого. При переходе программного блока управления в состояние С2 на выходе 30 образуется YC4 C2vC3VC7,no переднему фронту которого осуществляется запись информации с выхода коммутатора в регистр переносов сумматора. Далее в состоянии С2 на выходе 28 образуется сигнал YC5 С2 J поступающий в табличный умножитель 18 и образующий на выходе блока адрес коммутатора, соответствующий пропуску через коммутатор множимого, сдвинутого влево на два разряда.j . При переходе программного блока управления в состояние C3() на выходе 31 образуется сигнал yC6--C3vc4. По сигналам К-V и VC6 в состоянии СЗ осуществляется запись кода «i А с выхода коммутатора в регистр переносов и запись кода множимого с регистра переносов в регистр суммы через полусумматор. Далее в сумматоре осуществляется сложение содержимых регистра суммы и регистра переносов по правилам золотой 1-системы счисления в соответствии с известным алгоритмом Все образовавшиеся при этом переносы из t -го в (1-2)-й разряд записыва ются в регистр переносов по сигналу УСТ С4 на выходе 32 при переходе программного блока управления в состояние С4(). Сигналы записи VCB CS-TO частично нормализованной промежуточной суммы формируются на выходе 33 программного блока 20 управления пр -, его переходе в состояние С 5 нал об окончании нормализации 1-код вырабатывается на выходе сумматора 19 и поступает на вход блока 20. По этому сигналу программный блок управления снова переходит в состоя ние С4 для образования очередной промежуточной суммы и т.д. V ts SS HOpM cffi Процесс сложения 1-кодов в сумматоре 19 контролируется. Сигнал об ошибке сумматора поступает на выход 22 устройства. Процесс сложен промежуточных сумм с промежуточными переносами продолжается до тех пор, пока все промежуточные переносы не станут равны О, т.е. на выходе сумматора 19 вырабатывается сигнал П4 г конца суммирования ц . д рксГП см .,., I. J ПО которому завершается процесх: формирования произведения ()А. Программный блок управления переходит в состояние С б{155 к нррд, X KKg()) в котором на выходе 2Ь вырабатывается сигнал VC9 Сб , по которому произведение ( oi +1) А записывается в регистр , а регистр суммы cywtaTopa устанавливается в нуль Затем начинается процесс умножения множимого на тетрады разрядов множителя, начиная с младших разрядов. Программный блок управления переходит в состояние CI(f 7 котором вырабатывается сигнал :(С4 , и через коммутатор 17 в сумматор записывается соответтствующее частичное произведение. Управление коммутатором осуществляется с помощью табличного умножения 18, который в соответствии с анализируемой тетрадой разрядов множителя и значением переноса из предьщущей тетрады формирует адрес требуемого канала коммутатора. Функции табличного умножителя 18 иллюстрируются таблицей. Каждое из 13 возможных значений тетрады преобразуется в трехразрядный адрес, по которому выбирается соответствующий канал коммутатора. По сигналу на входе 27 в табличный умножитель записывается новое значение переноса. На выходах таблично го умножителя Формируются сигналы при выборе каналов с адресами 110 л л или 111 либо сигналы при выборе канала с адресом 111. Если очередное частичное произведение имеет вид 0001-А, то на вход сумматора через коммутатор поступает содержимое регистра 9, равное 0010А, со сдвигом на разряд вправо, причем старший освободившийся после сдвига разряд заполняется нулем и, кроме этого, к сумме добавляется корректирующий код вида 001. Для вьтолнения такой коррекции иа выходе ЗА формируется управляющий сигнал JfCIO СГ D 1 } программного блока. Если очередное частичное произ- ведение является обратным золотовым 1-кодом, то на выходе 35 блока 20 управления вырабатывается сигнал ) 1П). По этому сигналу при сложении 1-кодов в сумматоре в младший разряд промежуточной суммы прибавляется единица. При нахождении программного блока управления в состоянии С7 фор-, мируется сигнал С12 СТ, по которому к счетчику тактов программного блока 2D правления прибавляется единица. Если содержимое счетчика тактов К+1,. к.(пи)/4; 1 - разрядность множителя, то программный блок управления после завершейия работы сумматора переходи в состояние С8 . (58()-(Сг,1М-1,-К„,р), На выходе 27 вьфабатывается сигнал , по которому осзодествля ется сдйиг регистра множителя и регистра суммы на четыре разряда в сторону младших разрядов и запись Нового значения переноса в табличны умножитель 18. В процессе умножения может оказаться, что в регистре, суммы сумматора 19 при сдвиге будет находиться дополнительный золотрй 1-код текущей суммы частичных произве- дений.

0000 0001 0010 0100 0101 1000 1001 1010 0000 0010 0100 1000 1010

о о о о о о 1 1

000

001

0101

011

101

100

110

111

о о о 1 1

001 011 101 110 000 80 8 золотых По свойству золотых 1-кодов при сдвиге дополнительного золотого 1-кода на четыре разряда в сторону младших разрядов освободившиеся после сдвига разряды заполняются кодом вида 1010, Затем автомат управления переходит в состояние С7 и начинается умножение на новую тетраду разрядов множителя (t аг ) Если содержимое счетчика тактов оказывается равным if+if то программный блок управления из состояния С 5 переходит в состояние СО ( f ур « (6 - км). к см К«ор« ) , .РоЦесс умножения заканчивается и в сумматоре 19 находится золотой 1-код произведения.

f2

Irm

Ш1

f

i.

Г r

zs

127

г

.S

1

.

уф

.1

Л/

.2

27

l 28

J L

/7

2U

Фи&. 3

| Преобразователь прямого кода в обратный | 1982 |

|

SU1032448A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Параллельный сумматор | 1976 |

|

SU559237A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1981 |

|

SU997031A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-23—Публикация

1983-12-06—Подача