сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР | 1991 |

|

RU2006914C1 |

| Сумматор кодов с иррациональным основанием | 1991 |

|

SU1837279A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Последовательный сумматор | 1988 |

|

SU1571573A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для формирования остатков по модулю | 1986 |

|

SU1449986A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах с повышенной достоверностью обработки информации. изобретения является повышение достоверности функционирования последовательного сумматора. Последовательный сумматор, содержащий одноразрядный сумматор, снабжен блоком перемещения, блоком свертки, блоком контроля перемещения, блоком контроля свертки и дополнительными функциональными связями, что позволяет уменьшить вероятность пропуска ошибки. 5 ил,, 3 табл.

Изобретение относится к вычислительной технике, предназначено для последовательного сложения чисел, представленных кодами золотой пропорции, и может быть использовано в специализированных вычислительных устройствах с повышенной достоверностью обработки информации.

Целью изобретения является повышение достоверности функционирования последовательного сумматора.

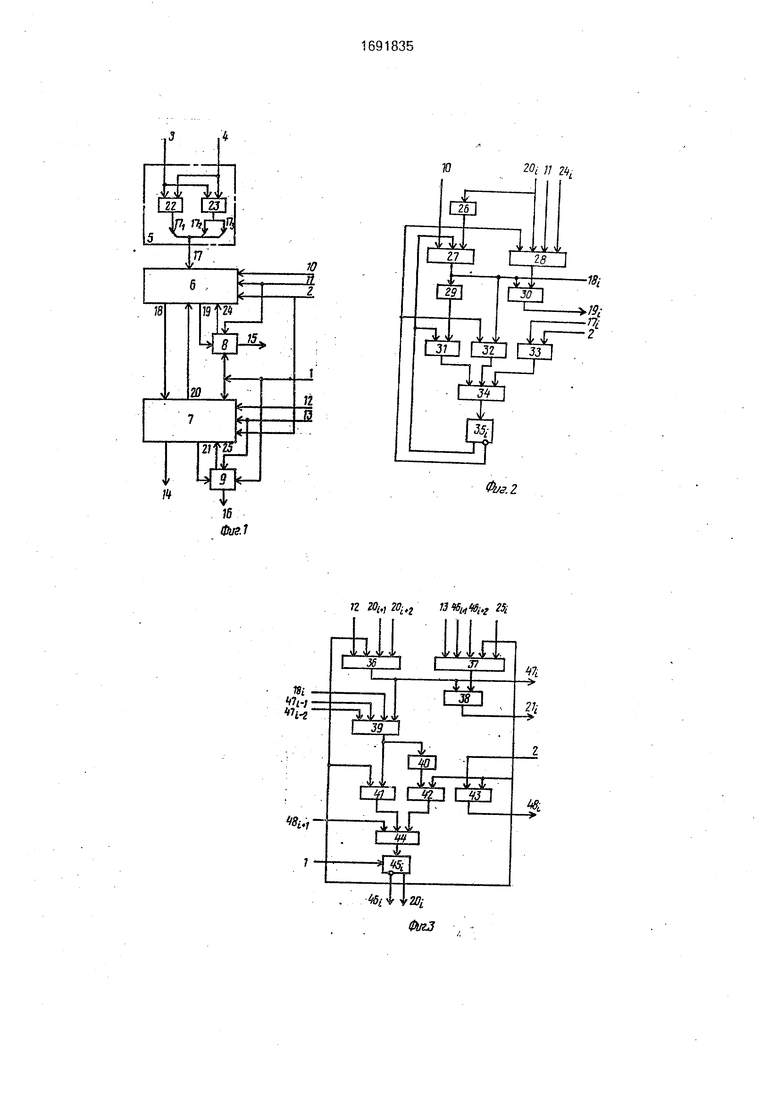

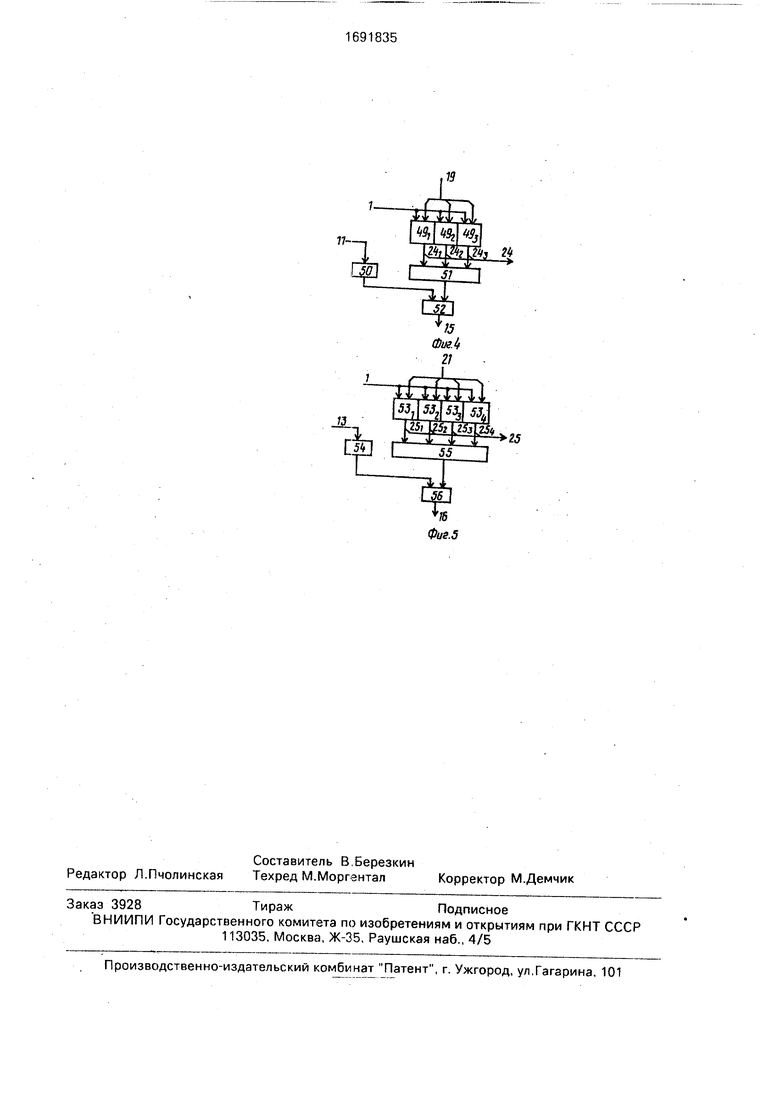

На фиг.1 представлена схема последовательного сумматора; на фиг.2 - схема одного разряда блока перемещения; на фиг.З - схема одного разряда блока свертки; на фиг.4 - схема блока контроля перемещения; на фиг.5 - схема блока контроля свертки,

Последовательный сумматор содержит вход 1 начальной установки, тактовый вхо д 2, входы 3 и 4-слагаемых, одноразрядный сумматор 5, блок 6 перемещения, блок 7 свертки, блок 8 контроля перемещения, блок 9 контроля свертки, вход 10 разрешения перемещения, вход 11 контроля перемещения, вход 12 разрешения свертки, вход 13 контроля свертки, выход 14 суммы, выход 15 ошибки перемещения, выход 16 ошибки свертки, выход 17 одноразрядного сумматора, выход 18 сигналов перемещения, контрольный выход 19 блока перемещения, прямой информационный 20 и контрольный 21 выходы блока свертки, элементы И 22 и ИЛИ 23 сумматора 5 и информационные выходы 24 и 25 блоков контроля перемещения и свертки.

Элемент И 22 одноразрядного сумматора 5 имеет выход 17i, элемент ИЛИ 23 - выходы 172 и 17з.

Каждый 1-й разряд блока 6 перемещения содержит входы 2, 10 и 11, 17j, 20i и 24i, входы 18i и 19i, элементы НЕ 26 и 29, элементы И 27, 28, 31, 32 и 33, элементы ИЛИ- 30 и 34 и D-триггер 35j.

Каждый i-й разряд блока 7 свертки содержит элементы И 36 и 37, элементы ИЛИ

с ю

00

со сл

38 и 39, элемент НЕ 40, элементы И 41 -43, элемент ИЛИ 44, триггер 45i, входы 1, 2, 12, 13, 20ifi, 20i+2, 18i, 25|, 46м, 46if2, 47i-2, 47|-1 и 48j+i, выходы 20i, 21i, 46i, 47| и 48|.

Блок 8 контроля перемещения содер- хит входы 1, 11 и 19, выходы 15 и 24, Т-триг- геры 49i, 492 и 49з, элемент 50 задержки, элемент ИЛИ 51 и элемент И 52.

Блок 9 контроля свертки содержит входы 1, 13 и 21, выходы 16 и 25, Т-триггеры 331-534, элемент 54 задержки, элемент ИЛИ 55 и элемент И 56.

Одноразрядный сумматор 5 предназначен для сложения двух слагаемых, представленных в кодах золотой пропорции.

Блок 6 перемещения выполняет операции перемещения над кодами, хранящимися в блоках 6 и 7.

Блок 7 свертки предназначен для выполнения операции свертки над кодом, хранящимся в блоке 7.

Блок 8 контроля перемещения контролирует правильность выполнения операции перемещения.

Блок 9 контроля свертки предназначен для контроля правильности выполнения операции свертки.

Последовательный сумматор работает следующим образом.

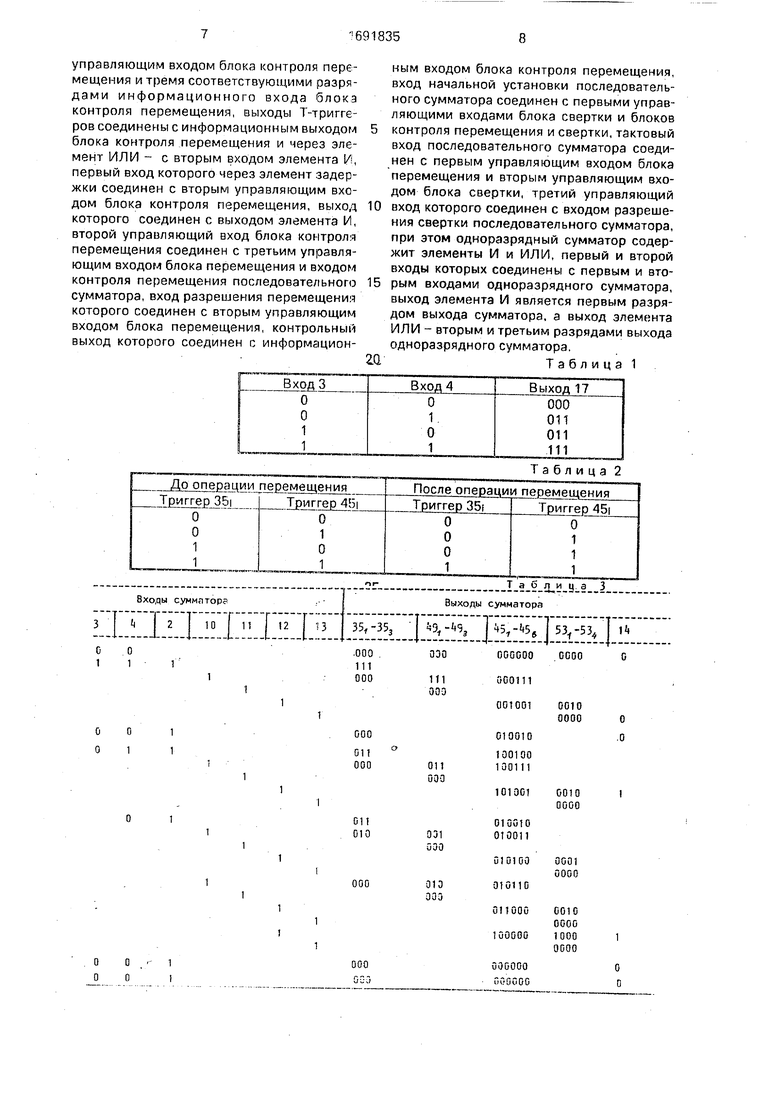

По сигналу начальной установки на входе 1 обнуляются триггеры 45j, в каждом разряде блока 7 свертки и Т-триггеры и в блоках 8 и 9. При поступлении на 3 и 4 первых разрядов слагаемых на Е ыходе сумматора 5 образуется сумма по правилам сложения в соответствии с табл.1. По сигналу на тактовом входе 2 код с Е)ыхода 17 сумматора 5 записывается через элементы И 33 и ИЛИ 34 в регистр блока перемещения, образованный D-триггерами 35. По этому же сигналу происходит сдвиг кода, хранящегося в регистре, образованном D-триггерами 45, в блоке 7 на 1 разряд Е сторону старших разрядов.

По сигналу на входе 10 разрешения перемещения в блоке 6 выполняется операция перемещения над трехразрядным кодом, хранящимся на D-триггерах 351-35з, и тремя младшими разрядами кода, хранящегося на D-триггерах (см. табл.2).

При наличии условий перемещения в i-м разряде блока 6 единичный сигнал с выхода элемента И 27, поступая через элементы И 32 и ИЛИ 34 на выход D-триггера 35i и с 18i через элементы ИЛИ 39, И 41 и ИЛИ 44 на вход D-триггера 45i, изменяет их состояние на обратное. Кроме того, этот сигнал поступает с выхода 19| на вход соот- Е етствующего Т-триггера 49i блока контроля перемещения, устанавливая

формируется единичный сигнал, поступающий с выхода 19 на вход соответствующего Т-триггера 49, блока 8, вследствие чего Т- триггер 49i должен снова перейти в нулевое состояние. В противном случае на

0 выходе 15 через время, достаточное для контроля операции перемещения и задаваемое элементом 50 задержки, появляется сигнал ошибки операции перемещения. По сигналу на входе 12 разрешения свертки в

5 блоке 7 свертки выполняется операция свертки над кодом, хранящимся на D-триггерах 45. Суть этой операции сводится к приведению кода 011 к коду 100. При наличии условий выполнения операций

0 свертки в i-м разряде блока 7 единичный сигнал с выхода элемента И 36 устанавливает в 1 D-триггер 45i блока 7, а поступая через выход 47i на соответствующие входы (i+1)-ro и (1+2)-го разрядов блока 7, устэнав5 ливает нулевые значения D-триггеров 45н-1, 45ц-2. Кроме того, этот сигнал через выход 21| проходит на вход соответствующего Т- триггера 53i блока 9 контроля свертки, устанавливая его в 1.

0 По сигналу с входа 13 осуществляется контроль правильности выполнения операции свертки. В случае отсутствия ошибки при выполнении операции свертки в i-м разряде блока 7 на выходе элемента И 37 фор5 мируется сигнал, который, поступая через выход 211 на вход Т-триггера 53j, переводит его в нулевое состояние. В случае ошибки в любом из четырех старших разрядов блока 7 на выходе 16 формируется сигнал ошибки

0 свертки.

Далее операции перемещения и свертки повторяются еще три раза, вследствие чего код, хранящийся на D-триггерах 35 блока 6, становится равным нулю, а в триг5 гере 45i записывается значение (i-2)-ro разряда суммы, которое поступит на выход 14 суммы. Четыре последовательных такта выполнения операций перемещения и свертки соответствуют наиболее тяжелой кодовой

0 ситуации, которая может возникнуть при сложении j-x разрядов слагаемых, когда значения j-x цифр слагаемых равны 1, а значение кода, хранящегося на D-триггерах , равно 1010.

5Затем начиная с выдачи сигнала на тактовом входе 2 выполняется сложение вторых разрядов слагаемых и формирование (И)-го разряда суммы путем выполнения последовательности описанных действий. Для сложения n-разрядных кодов золотой пропорции и формирования n-разрядного кода суммы требуется (n+З) такта работы последовательного сумматора.

Пример работы последовательного сумматора при сложении кодов 01001 и 01010 приведен в табл.3. Такты холостых операций перемещения и свертки, не вызывающие изменений в процессе сложения, в табл.3 опущены.

Формула изобретения Последовательный сумматор, содержащий одноразрядный сумматор, причем первый и второй входы слагаемых последовательного сумматора соединены с входами одноразрядного сумматора, отличающийся тем, что, с целью повышения достоверности функционирования, в него введены трехразрядный блок перемещения, шестиразрядный блок свертки, блок контроля перемещения и блок контроля свертки, причем выход одноразрядного сумматора соединен с первым информационным входом блока перемещения, 1-й разряд которого содержит два элемента НЕ, пять элементов И, два элемента ИЛИ и D-триг- гер, прямой выход которого соединен с вторым входом первого элемента И и первым входом третьего элемента И, второй вход и выход которого соединены соответственно с выходом второго элемента НЕ и первым входом второго элемента ИЛИ, второй и третий входы которого соединены с выходами соответственно четвертого и пятого элементов И, первые входы которых соединены соответственно с инверсным выходом D- триггера, вход которого соединен с выходом второго элемента ИЛИ, и 1-м разрядом первого информационного входа блока перемещения, три управляющих входа которого соединены соответственно с вторым входом пятого элемента И, первым входом первого элемента И и третьим входом второго элемента И, первый, второй и четвертый входы которого соединены соответственно с инверсным выходом D-тригге- ра, 1-ми разрядами третьего и второго информационных входов блока перемещения, который также через первый элемент НЕ соединен с третьим входом первого элемента И, выход которого соединен с входом второго элемента НЕ, вторым входом четвертого элемента И, i-м разрядом выхода сигналов перемещения блока перемещения и первым входом первого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго элемента И и 1-м разрядом контрольного выхода блока перемещения, третий и второй информационные входы которого соединены соответственно с информационным выходом блока контроля перемещения и прямым информационным выходом блока свертки, каждый 1-й разряд которого содержит пять элементов И, три элемента ИЛИ, элемент 5 НЕ и D-триггер, прямой вход которого соединен с вторым входом четвертого элемента И, первым входом пятого элемента И и пятым входом второго элемента И, первые четыре входа и выход которого соединены

10 соответственно с четвертым управляющим входом блока свертки (i-M)-M и (+2)-м разрядами инверсного информационного выхода блока свертки, i-м разрядом второго информационного входа 5пока свертки и вторым

15 входом первого элемента ИЛИ, выход которого соединен с i-м разрядом контрольного выхода блока свертки, i-й разряд инверсного информационного выхода которого соединен с инверсным выходом D-триггера,

0 первым входом третьего элемента И и вторым входом первого элемента И, остальные три входа которого соединены соответственно с третьим управляющим входом блока свертки, (1+1)-м и (i+2)-M разрядами

5 прямого информационного выхода блока свертки, 1-й разряд выхода сигналов свертки которого соединен с первым входом первого элемента ИЛИ, выходом первого элемента И и четвертым входом второго элемента

0 ИЛИ, первые три входа которого соединены соответственно с (1-2)-м и (И)-м разрядами выхода сигналов свертки блока свертки и i-м разрядом информационного входа блока свертки, а выход второго элемента ИЛИ

5 соединен с вторым входом третьего элемента И и через элемент НЕ - с первым входом четвертого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, первый и второй входы и выход кото0 рого соединены соответственно с (1+1}-м разрядом выхода сигналов сдвига блока свертки, выходом третьего элемента И и первым входом D-тригера, второй вход которого соединен с первым управляющим

5 входом блока свертки, второй управляющий вход которого соединен с вторым входом пятого элемента И, выход которого соединен с i-м разрядом выхода сигналов сдвига блока свертки, старший разряд прямого ин0 формационного выхода которого является выходом суммы последовательного сумматора, первый и второй информационные входы и контрольный выход блока свертки соединены соответственно с выходом сиг5 налов перемещения блока перемещения, информационными выходом и входом блока контроля свертки, содержащего четыре -Т- триггера, элемент задержки, элементы ИЛИ и И, причем первые и вторые входы Т-триггеров соединены соответственно с первым

управляющим входом блока контроля перемещения и тремя соответствующими разрядами информационного входа блока контроля перемещения, выходы Т-тригге- ров соединены с информационным выходом блока контроля перемещения и через элемент ИЛИ - с вторым входом элемента И, первый вход которого через элемент задержки соединен с вторым управляющим входом блока контроля перемещения, выход которого соединен с выходом элемента И, второй управляющий вход блока контроля перемещения соединен с третьим управляющим входом блока перемещения и входом контроля перемещения последовательного сумматора, вход разрешения перемещения которого соединен с вторым управляющим входом блока перемеи1ения, контрольный выход которого соединен с информационным входом блока контроля перемещения, вход начальной установки последовательного сумматора соединен с первыми управляющими входами блока свертки и блоков

контроля перемещения и свертки, тактовый вход последовательного сумматора соединен с первым управляющим входом блока перемещения и вторым управляющим входом блока свертки, третий управляющий

вход которого соединен с входом разрешения свертки последовательного сумматора, при этом одноразрядный сумматор содержит элементы И и ИЛИ, первый и второй входы которых соединены с первым и вторым входами одноразрядного сумматора, выход элемента И является первым разрядом выхода сумматора, а выход элемента ИЛИ - вторым и третьим разрядами выхода одноразрядного сумматора.

Таблица1

Таблица 2

001001

0010 0000

011 000

010010

100100 100111

101001

0010 0000

031 030

010 333

010010 010011

010100 010110

опооо

100000

000000 UC-GOOO

0001 0000

0010 0000 1000 0000

о

о

8

ISP

L

a .

Ј

in

CO

oo

en иэ

&W«Mi

«n

wf i

fsj

51

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1983 |

|

SU1170449A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-15—Публикация

1989-12-22—Подача