Изобретение относится к вьтисли- тельной технике и может быть использовано в специализированных и универсальных ЭВМ.

Цель изобретения - упрощение устройства.

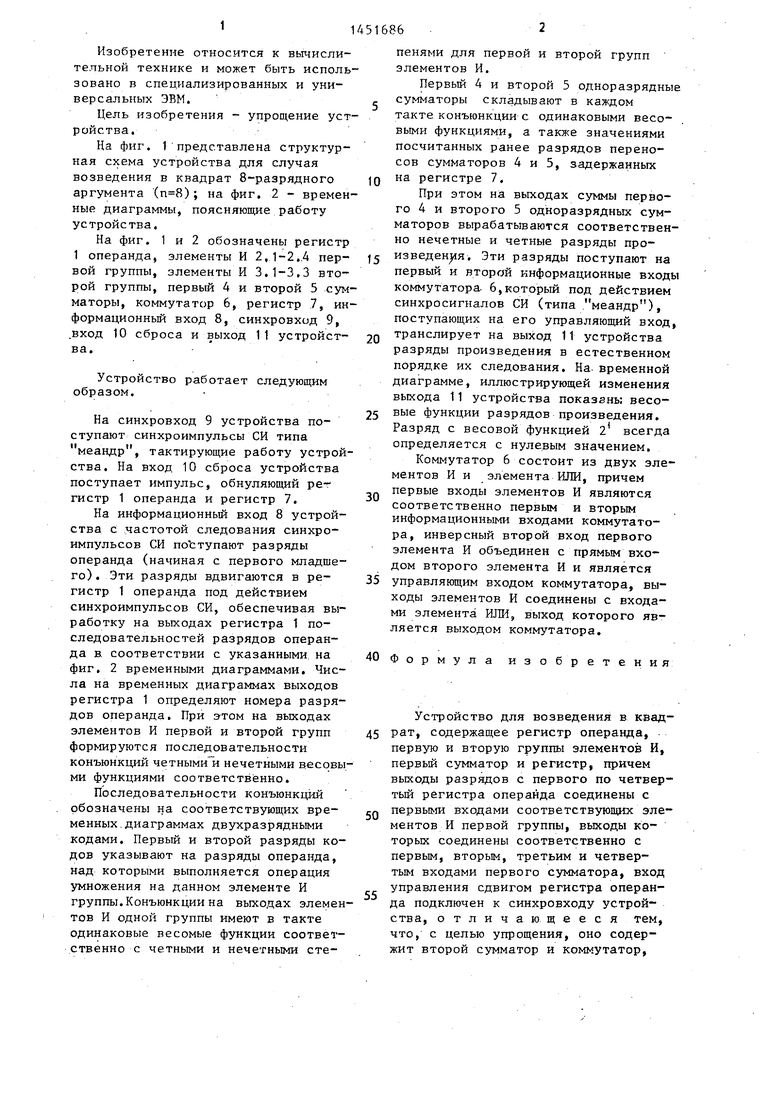

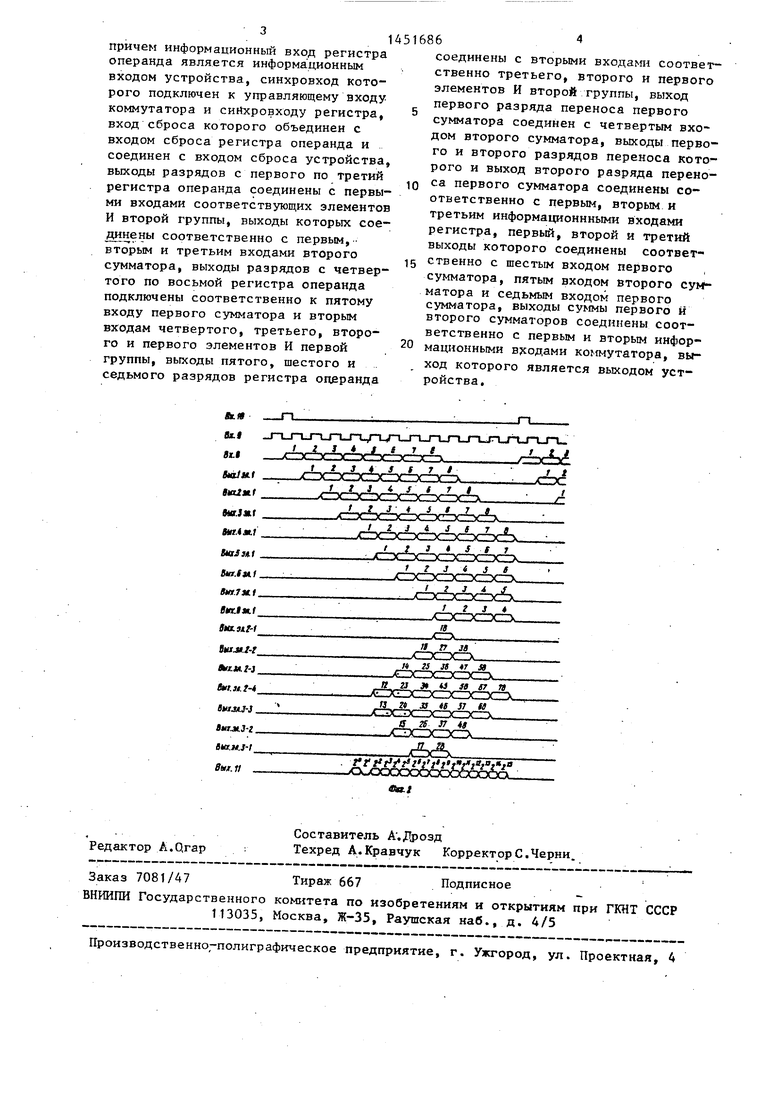

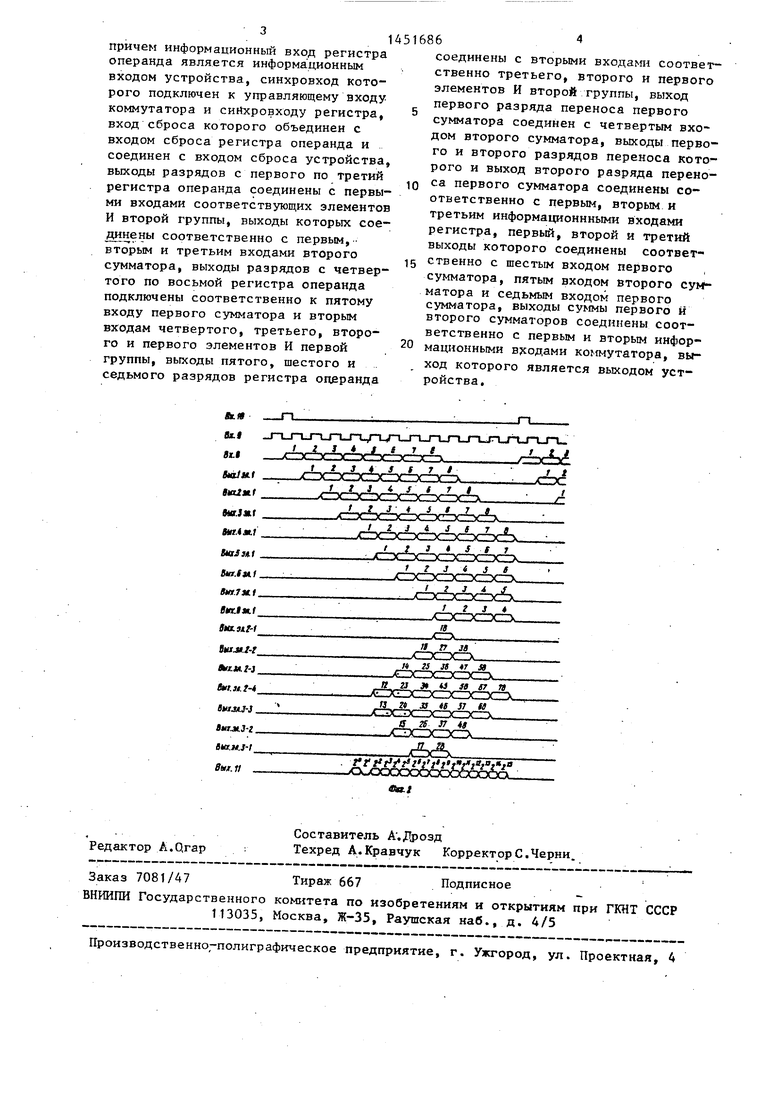

На фиг, 1 представлена структурная схема устройства для случая возведения в квадрат 8-разрядного аргумента (); на фиг. 2 - временные диаграммы, поясняющие работу устройства.

На фиг, 1 и 2 обозначены регистр 1 операнда, элементы И 2,1-2,Л первой группы, элементы И 3,1-3.3 второй группы, первый 4 и второй 5 сумматоры, коммутатор 6, регистр 7, ин формационньй вход 8, синхровход 9, .вход 10 сброса и выход 11 устройства.

Устройство работает следующим образом.

На синхровход 9 устройства поступают синхроимпульсы СИ типа меандр, тактирующие работу устройства. На вход 10 сброса устройства поступает импульс, обнуляющий регистр 1 операнда и регистр 7,

На информационный вход 8 устройства с частотой следования синхроимпульсов СИ поступают разряды операнда (начиная с первого младшего) , Эти разряды вдвигаются в регистр 1 операнда под действием синхроимпульсов СИ, обеспечивая выработку на выходах регистра 1 последовательностей разрядов операнда в. соответствии с указанными на фиг. 2 временными диаграммами. Числа на временных диаграммах выходов регистра 1 определяют номера разрядов операнда. При э-том на выходах элементов И первой и второй групп формируются последовательности конъюнкций четными нечетными весовыми функциями соответственно.

Последовательности конъюнкций обозначены на соответствующих временных, диаграммах двухразрядными кодами. Первый и второй разряды кодов указывают на разряды операнда, над которыми выполняется операция умножения на данном элементе И группы,Конъюнкции на выходах элементов И одной группы имеют в такте одинаковые весомые функции соответственно с четными и нечетньми сте

4516862

пенями для первой и второй групп элементов И,

Первый А и второй 5 одноразрядные с сумматоры складывают в каждом

такте конъюнкции с одинаковыми весовыми функциями, а также значениями посчитанных ранее разрядов переносов сумматоров 4 и 5, задержанных

Q на регистре 7.

При этом на выходах суммы первого 4 и второго 5 одноразрядных сумматоров вырабатываются соответственно нечетные и четные разряды про15 изведен я. Эти разряды поступают на первый и второй информационные входы коммутатора. 6,который под действием синхросигналов СИ (типа меандр), поступающих на его управляющий вход,

20 транслирует на выход 11 устройства разряды произведения в естественном порядке их следования. На. временной диаграмме, иллюстрирующей изменения выхода 11 устройства показаны весо25 вые функции разрядов произведения. Разряд с весовой функцией 2 всегда определяется с нулевым значением.

Коммутатор 6 состоит из двух элементов И и элемента ИЛИ, причем

3Q первые входы элементов И являются соответственно первым и вторым информационными входами коммутатора, инверсный второй вход первого элемента И объединен с прямым входом второго элемента И и является

35 управляющим входом коммутатора, выходы элементов И соединены с входами элемента ИЛИ, выход которого является выходом коммутатора.

40 Формула изобретения

Устройство для возведения в квад- 5 рат, содержащее регистр операнда, первую и вторую группы элементов И, первьй сумматор и регистр, причем выходы разрядов с первого по четвертый регистра операнда соединены с первыми входами соответствующих элементов И первой группы, выходы которых соединены соответственно с первым, вторым, третьим и четвертым входами первого сумматора, вход управления сдвигом регистра операнда подключен к синхровходу устройства, отличающееся тем, что, с целью упрощения, оно содержит второй сумматор и коммутатор.

причем информационньш вход регистра операнда является информационным входом устройства, синхровход которого подключен к управляющему входу коммутатора и сийхровходу регистра, вход сброса которого объединен с входом сброса регистра операнда и соединен с входом сброса устройства, выходы разрядов с первого по третий регистра операнда соединены с первыми входами соответствующих элементов И второй группы, выходы которых сое- соответственно с первым, вторым и третьим входами второго сумматора, выходы разрядов с четвертого по восьмой регистра операнда подключены соответственно к пятому входу первого сумматора и вторым входам четвертого, третьего, второго и первого элементов И первой группы, выходы пятого, шестого и седьмого разрядов регистра операнда

1451686

соединены с вторыми входами соответственно третьего, второго и первого элементов И второй группы, выход первого разряда переноса первого сумматора соединен с четвертым входом второго сумматора, выходы первого и второго разрядов переноса которого и выход второго разряда перено- са первого сумматора соединены соответственно с первым, вторым и третьим информационнными входами регистра, первый, второй и третий выходы которого соединены соответ- ственно с шестым входом первого

сумматора, пятым входом второго сумматора и седьмым входом первого сумматора, выходы суммы первого и второго сумматоров соединены соот- ветственно с первым и вторым информационными входами коммутатора, вьг- ход которого является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1532918A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1509877A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1711152A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1587498A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Устройство для задержки цифровой информации | 1986 |

|

SU1383325A1 |

Изобретение относится к вычислительной технике и позволяет выполнять операцию возведения в квадрат операнда, поступающего на вход устройства в последовательном коде. Цель изобретения - упрощение устройства. Устройство содержит регистр 1, в который вдвигаются разряды операнда, элементы И первой 2 и второй 3 групп, вычисляющие: конъюнкции с одинаковыми в такте весовыми функциями соответственно.нечетных и четных разрядов произведения, одноразрядные сумматоры 4 и 5, складывакяцие конъюнкции с вькодов соответственно первой 2 и второй 3 групп элементов И, а также значения разрядов переноса с выходов,сумматоров 4. и 5, задержанные на необходимое количество тактов на регистре 7, коммутатор 6, подключающий на выход устройства значения разрядов произведения с выходов суммы сумматоров 4 и 5 соответственно в. первых и вторых половинах тактов работы устройства. 2 ил.. i (Л

| Устройство для возведения в квадрат п-разрядных двоичных чисел | 1978 |

|

SU699521A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1987-02-16—Подача