Изобретение относится к импульсной технике и может быть использовано при построении универсальных и специализированных цифровых устройств, в том числе ЗУ, генераторов, формирователей импульсов, электрически регулируемых линий задержки на интегральных МДП-структурах.

Известны управляемые линии задержки, содержащие линии задержки с отводами, мультиплексор, инверторы, дискретные компоненты. Недостатком известных схем является сложность, относительно высокое потребление тока в статическом режиме и зависимость диапазона регулирования задержки от сложности схемы.

Известна линия задержки, содержащая последовательно соединенные инверторы на КМДП-транзисторах. Недостатком известной схемы является невозможность изменения ее временных параметров электрическим способом, что снижает ее функциональные возможности.

Наиболее близкой по технической сущности является управляемая линия задержки, входящая в состав схемы управляемого формирователя импульсов, содержащая первую и вторую шины питания, входы управления, группу инвертирующих звеньев задержки, входы и выходы которых соединены соответственно с входом и выходом линии задержки, каждое звено задержки содержит последовательно соединенные два МДП-транзистора первого, два МДП-транзистора второго типа проводимости соответственно между первой, второй шиной питания и выходом звена, вход которого соединен с затворами двух транзисторов разного типа проводимости, а затворы двух других транзисторов разного типа проводимости соединены с входом и выходом инвертора, вход которого соединен с входом управления звена.

Недостатками известной схемы являются относительно небольшой диапазон регулирования задержки вследствие изменения формы выходного сигнала в процессе регулировки (т. е. зависимость фронта выходного сигнала от сигналов управления), а также относительно низкие функциональные возможности, вследствие невозможности регулировки времени задержки только одного из фронтов при неизменном (и минимальном) значении задержки по другому фронту при заданном числе звеньев задержки.

Цель изобретения - расширение диапазона регулирования времени задержки схемы.

Это достигается за счет того, что в управляемой линии задержки, содержащей первую и вторую шины питания, входы управления, четные и нечетные звенья задержки, каждое из звеньев выполнено из двух МДП-транзисторов первого и второго типов проводимости, стоки которых соединены с выходом звена, исток МДП-транзистора первого типа проводимости нечетного звена соединен с первой шиной питания, исток МДП-транзистора второго типа проводимости четного звена соединен с второй шиной питания, управляющий МДП-транзистор первого, второго типа проводимости в четном, нечетном звене, соответственно, затвор управляющего МДП-транзистора соединен с входом управления звена, в каждом четном звене исток управляющего МДП-транзистора соединен с первой шиной питания, а сток подключен к истоку МДП-транзистора первого типа проводимости, а в каждом нечетном звене исток управляющего МДП-транзистора соединен с второй шиной питания, а сток подключен к истоку МДП-транзистора второго типа проводимости, в каждое четное звено введен дополнительный МДП-транзистор первого типа проводимости, исток которого подключен к первой шине питания, затвор к второй, а сток соединен со стоком управляющего МДП-транзистора первого типа проводимости, в каждое нечетное звено введен дополнительный МДП-транзистор второго типа проводимости, исток которого подключен к второй шине питания, затвор к первой, а сток соединен со стоком управляющего МДП-транзистора второго типа проводимости, а звенья задержки соединены последовательно, так, что вход первого звена является входом, а выход последнего звена является выходом схемы, вход последующего звена соединен с выходом предыдущего.

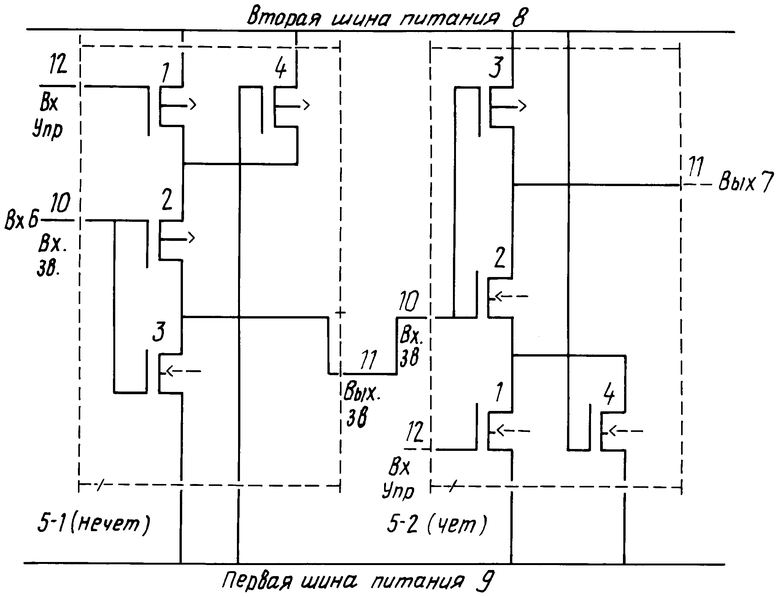

На чертеже показан вариант схемы управляемой линии задержки.

Она содержит первый 1 (управляющий), второй 2, третий 3 и четвертый 4 (дополнительный) МДП-транзисторы в каждом звене 5 (5-1 - нечетное, 5-2-четное) линии задержки, вход 6 и выход 7 управляемой линии задержки, вторую 8, первую 9 шины питания, вход 10 нечетного звена 5-1 соединен с входом 6 схемы, выход 11 четного звена 5-2 соединен с выходом 7 схемы, вход 10 звена 5-2 соединен с выходом 11 звена 5-1. В каждом звене 5 стоки транзисторов 2 и 3 разного типа проводимости соединены с выходом 11, затворы с входом 10, а затвор транзистора 4 подключен к управляющему входу 12 звена. В звене 5-1 транзисторы 1 и 4 второго (p-) типа проводимости включены параллельно между шиной 8 (питание) и истоком транзистора 2 второго (p-) типа проводимости, а затвор транзистора 4 первого (n-) типа проводимости соединен с шиной 9 (общая). В звене 5-2 транзисторы 1 и 4 первого (n-) типа проводимости включены параллельно между шиной 9 и истоком транзистора 2 первого (n-) типа проводимости, а затвор транзистора 4 первого (n-) типа проводимости и исток транзистора 3 второго (p-) типа проводимости соединены с шиной 8.

Управляемая линия задержки работает следующим образом.

Каждое звено 5 осуществляет задержку входного сигнала, инвертируя его. Поэтому если число звеньев 5 четно (нечетно), то суммарная задержка схемы от входа 6 до выхода 7 будет без инверсии (с инверсией) входного сигнала. Каждое четное звено 5-2 имеет задержку по фронту 1->> 0 входного сигнала меньше, чем задержку по фронту 0 - 1 входного сигнала. Напротив, каждое нечетное звено (5-1) имеет задержку по фронту 0->> 1 входного сигнала меньше, чем задержку по фронту 1->> 0 входного сигнала.

Транзисторы 4 в каждом звене нормально всегда открыты, т. е. на исток транзистора 2 подается потенциал шины 9 (уровень логического 0) для звена 5-1 или потенциал шины 8 (уровень логической 1) для звена 5-2. Транзисторы 1 могут быть открыты или закрыты в зависимости от управляющих сигналов на входе 12 звена. Так транзистор 1 звена 5-1 открыт/закрыт, если на вход 12 подан сигнал (Up= 0 / Up= 1, а транзистор 1 звена 5-2 открыт/закрыт, если на вход 12 подан сигнал Un= 1/Un= 0.

Открытый транзистор 1, включенный параллельно транзистору 4, увеличивает проводимость проводящей (формирующей) ветви звена 5, т. е. возможно управление фронтом (задержкой) 0 ->> (нарастания) выходного сигнала звена 5-1 и фронтом (задержкой) 1->> 0 (спада) выходного сигнала звена 5-2, соответственно при помощи сигналов Up и Un.

При этом фронт (задержка) выходного сигнала 1->> 0/0->> 1 в звене 5-1/5-2 не регулируются. (56) Патент США N 4379265, кл. 328/55, 1982.

Авторское свидетельство СССР N 1309302, кл. H 03 K 5/13.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемая линия задержки | 1987 |

|

SU1525881A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1312567A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1291969A1 |

| Узел формирования переноса | 1986 |

|

SU1363189A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| Формирователь импульсов на МДП-транзисторах | 1987 |

|

SU1473072A1 |

| Узел синхронизации | 1987 |

|

SU1469549A1 |

| Формирователь импульсов считывания для блоков памяти | 1985 |

|

SU1273996A1 |

| Линия задержки | 1989 |

|

SU1706024A1 |

| Логическое устройство | 1986 |

|

SU1378047A1 |

Сущность изобретения: линия задержки содержит первый, второй, третий и четвертый МДП-транзисторы в каждом звене линии задержки, причем вход первого звена соединен с входом, а выход последнего звена соединен с выходом управляемой линии задержки, вторую и первую шину питания, причем вход последующего звена задержки соединен с выходом предыдущего звена задержки. В каждом звене затворы транзисторов разного типа проводимости соединены с входом, а стоки с выходом затвор транзистора соединен с управляющим входом. В каждом нечетном звене транзисторы второго типа проводимости включены параллельно между шиной и истоком транзистора второго типа проводимости, затвор транзистора второго типа проводимости и исток транзистора первого типа проводимости соединены с шиной. В каждом четном звене транзисторы первого типа проводимости включены параллельно между шиной и истоком транзистора первого типа проводимости, а затвор транзистора первого типа проводимости и исток транзистора второго типа проводимости соединены с шиной. 1 ил.

УПРАВЛЯЕМАЯ ЛИНИЯ ЗАДЕРЖКИ, содержащая первую и вторую шины питания, входы управления, соединенные последовательно четные и нечетные звенья задержки, каждое из звеньев выполнено из двух МДП-транзисторов первого и второго типов проводимости, стоки которых соединены с выходом звена, затворы - с входом звена, исток МДП-транзистора первого типа проводимости нечетного звена соединен с первой шиной питания, исток МДП-транзистора второго типа проводимости четного звена соединен с второй шиной питания, управляющий МДП-транзистор первого типа проводимости в четном звене, управляющий МДП-транзистор второго типа проводимости в нечетном звене, затвор каждого из которых соединен с управляющими входами, в каждом четном звене исток управляющего МДП-транзистора соединен с первой шиной питания, сток подключен к истоку МДП-транзистора первого типа проводимости в каждом нечетном звене исток управляющего МДП-транзистора соединен с второй шиной питания, сток подключен к истоку МДП-транзистора второго типа проводимости, отличающаяся тем, что, с целью расширения диапазона регулирования, в каждое четное звено введен дополнительный МДП-транзистор первого типа проводимости, исток которого подключен к первой шине питания, затвор - к второй, а сток соединен со стоком управляющего МДП-транзистора первого типа проводимости, в каждое нечетное звено введен дополнительный МДП-транзистор второго типа проводимости, исток которого подключен к второй шине питания, затвор - к первой, а сток соединен со стоком управляющего МДП-транзистора второго типа проводимости.

Авторы

Даты

1994-05-15—Публикация

1990-07-09—Подача