Изобретение касается устройства коммутации широкополосных сигналов с матрицей точек связи на полевых транзисторах, входы которого оснащены входными блоками усилителей-формирователей, а выходы могут быть оснащены выходными блоками усилителей-формирователей, причем выходные линии матрицы через блоки предварительного заряда, управляемые тактовым сигналом, который подразделяют интервал времени переключения двоичного разряда на фазу предварительного заряду и саму фазу переключения, могут заряжаться в течение каждой фазы предварительного заряда потенциала предварительного заряда, действующего между обоими рабочими потенциалами, или также до одного из обоих рабочих потенциалов. Это устройство отличается в соответствии с изобретением тем, что выход того или иного входного блока усилителя-формирователя соединен через управляемый пороговой величиной пороговый элемент обратной связи с одним запирающим входом входного блока усилителя-формирователя, через который завершается перезаряд выхода соответствующей входной схемы усилителя-формирователя.

Цель изобретения - снижение мощности потерь.

Преимущество изобретения заключается в точном ограничении изменения сигналов во входных линиях. Уменьшение изменения сигналов во входных линиях ведет к уменьшению потерь на перезаряд, что равнозначно уменьшению потребления тока. При уменьшенном потреблении тока достигается соответственно меньшая мощность потерь, которая позволяет добиться увеличения плотности расположения элементов связи или частоты переключений. В соответствии с этим из уменьшенного потребления тока вытекает уменьшение обусловленных выбросами тока помех рабочего напряжения устройства связи широкополосных сигналов. Кроме того, в результате ограничения изменения сигналов снижается степень нежелательных влияний на соседние тракты прохождения сигналов.

На фиг. 1 изображено предложенное устройство связи широкополосных сигналов; на фиг. 2-4 его коммутационно-техническая реализация.

Устройство связи широкополосных сигналов (см. фиг. 1) содержит матрицу связи 1 на полевых транзисторах, входные линии е1. . . еj которой через вентильные схемы G1. . . Gj управляемые общим для них тактовым сигналом ТРС и выходные блоки усилителей-формирователей соединены с входными линиями матрицы столбцевыми линиями S1-Sj матрицы связи, а последние через индивидуальные для столбцов пороговые элементы 3 обратной связи соединены с одним запирающим входом S′ cоответствующего входного блока 2 усилителя-формирователя. Входы горизонталей матрицы связи соединены с блоками 4 предварительного заряда и управляются одним общим для них тактовым сигналом ТРС. Выходы матрицы связи через выходные блоки 5 усилителей-формирователей соединены с удерживающими ячейками L1. . . Lm, которые также управляются одним общим для них тактовым сигналом ТРС.

Матрица связи 1 содержит точки КР11. . . КPmj связи, элементы связи которых могут управляться индивидуальной для точки связи удерживающей ячейкой Hij памяти (при точке КРij связи), выход r которой подключен к управляющему входу r того или иного элемента (Kij применительно к точке КP связи) связи.

Удерживающие ячейки Hij связи управляются двумя управляющими декодерами, а именно декодером DХ строки и декодером DY cтолбца, по двум координатам через соответствующие управляющие линии х1. . . хm, y1. . . ym. . .

С этой целью, как показано на фиг. 1, оба управляющих декодера DХ, DY могут нагружаться в направлении от входных регистров Reg Х, Reg Y общим для ряда (строка или столбец) точек связи матрицы адресом строк точек связи или столбцов точек связи, по которому они выдают управляющий сигнал "1" в линию управления, которая соответствует тому или иному адресу рядов точек связи. Совпадение управляющего сигнала "1" строк и управляющего сигнала "1" столбцов в точке пересечения соответствующим строки матрицы с соответствующим столбцом матрицы при установлении соответствующего соединения обуславливает в этом случае активацию расположенной там удерживающей ячейки памяти, например ячейки Нij памяти, в результате чего управляемый соответствующей удерживающей ячейкой (Hij) памяти элемент связи, например элемент Kij связи, переводится в проводящее состояние.

Чтобы обеспечить повторное запирание рассмотренного в данном примере элемента Kij связи при ликвидации соответствующего соединения, управляющий декодер DХ нагружается в направлении от входного регистра Reg Х cоответствующим адресом строки, в результате чего декодер DХ строки вновь выдает в свою выходную линию хi управляющий сигнал "1" строки, и одновременно декодер DУ cтолбца нагружается от своего входного регистра Reg У, например, холостым адресом или адресом столбца некоммутированных точек связи, в результате чего он выдает в свою выходную линию Yj управляющий сигнал "0" столбца, совпадение управляющего сигнала "1" строки и управляющего сигнала "0" столбца обуславливает в этом случае сброс удерживающей ячейки Нij памяти в исходное состояние, в результате чего происходит запирание управляемого элемента Кij связи.

На фиг. 2 показано, могут быть реализованы входные блоки 2. Входной блок 2 усилителя-формирователя выполнен на КМОП-инвертирующем усилителе, образованном двумя транзисторами Т2, Т3, один вывод рабочего напряжения которого непосредственно соединен с источником UDD - USS рабочего напряжения, другой вывод рабочего напряжения которого соединен через транзистор Т1 с источником UDD - USS рабочего напряжения. Управляющий электрод транзистора Т1 образует запирающий вход S′ входного усилителя Е, соединение управляющих электродов транзисторов Т2 и Т3 образует вход е' входной схемы Е усилителя-формирователя, а соединение главных электродов транзисторов Т2 и Т3 образует выход входной схемы Е усилителя-формирователя, который соединяется с той или иной линией S cтолбца.

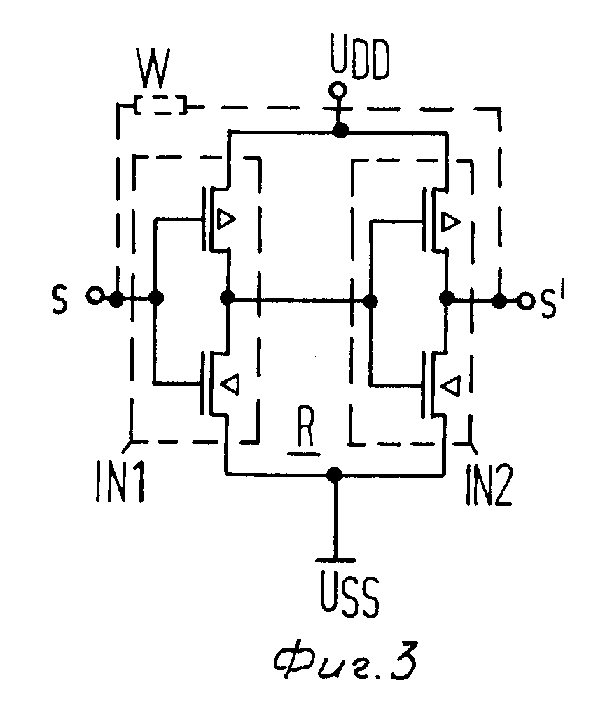

На фиг. 3 поясняется возможность технической реализации звеньев пороговых элементов 3 обратной связи.

Пороговые элементы обратной связи образованы в данном случае цепочкой двух КМОП-инверторов 1N1, 1N2, причем та или иная линия столбца соединена с управляющими электродами пары транзисторов, которая образует первый КМОП-инвертор YN1, а точка соединения главных электродов первой пары транзисторов соединена с управляющими электродами пары транзисторов, которая образует второй КМОП-инвертор 1N2. Соединение обоих главных электродов второй пары транзисторов образует выход S′ того или иного порогового элемента обратной связи. Характеристический порог переключения такого звена R обратной связи, образованного КМОП-инверторами 1N1, 1N2, зависит от порогового напряжения Uтн первого инвертора 1N1 и составляет около 40% от рабочего напряжения, используемого для питания порогового элемента 3 обратной связи. В соответствии с этим для порогового элемента 3 обратной связи порог переключения составляет приблизительно 2В при рабочем напряжении UDD-USS5В.

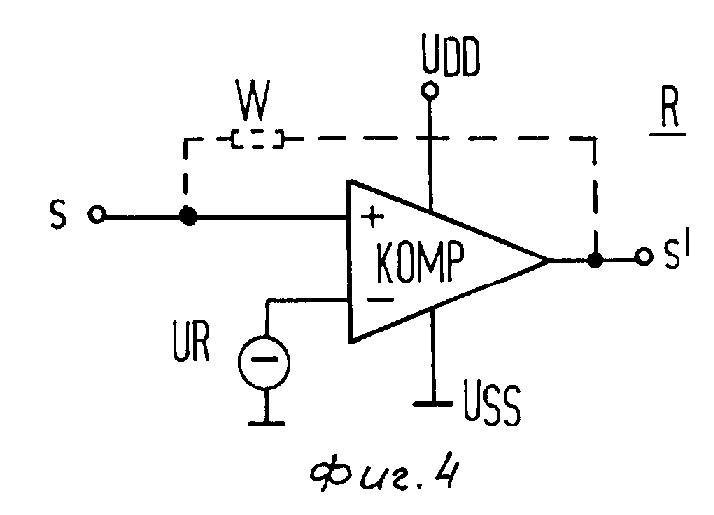

Пороговый элемент 3 обратной связи может быть выполнен в соответствии с изображенным на фиг. 4 блоком сравнения КМОП, например, в виде операционного усилителя, неинвертирующий вход (+) которого соединен с той или иной (входной линией матрицы) линией S столбца, инвертирующий вход (-) которого соединен с одним выводом источника UR эталонного напряжения, другой вывод которого соединен с выводом источника UDD - USSрабочего напряжения. Выход блока сравнения КОМР образует вывод для запирающего входа S' входного блока 2 усилителя-формирователя. Порог Uтн переключения такого порогового элемента 3 обратной связи соответствует величине напряжения на инвертирующем входе (-) блока КОМР сравнения. Пороговые элементы 3 обратной связи по фиг. 3 или 4 могут находиться в состоянии обратной связи с помощью высокоомного резистора W, соединяющего выход S' c входом S порогового элемента 3 обратной связи, который обуславливает, с одной стороны, увеличение усиления в области порога переключения и, с другой стороны, небольшой гистерезис порога переключения. Оба эффекта улучшают коммутационные характеристики порогового элемента 3 обратной связи.

Выходные блоки 4 усилителя-формирователя могут быть выполнены аналогично пороговым элементам обратной связи по фиг. 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1989 |

|

RU2106755C1 |

| ШИРОКОПОЛОСНОЕ УСТРОЙСТВО КОММУТАЦИИ | 1991 |

|

RU2103841C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2103832C1 |

| СПОСОБ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1987 |

|

RU2105428C1 |

| УСТРОЙСТВО ПРОСТРАНСТВЕННОЙ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1986 |

|

RU2011304C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1991 |

|

RU2105431C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2105430C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ИНТЕГРАЛЬНЫМ МОДУЛЕМ | 1987 |

|

RU2071636C1 |

| Устройство коммутации широкополосных сигналов | 1989 |

|

SU1838888A3 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1738105A3 |

В устройстве коммутации широкополосных сигналов с матрицей связи в технике полевых транзисторов для питания входных линий матрицы предусмотрен входной блок усилителя-формирователя, который при достижении заданного уровня сигнала в соответствующей входной линии матрицы, который оеспечивает надежное переключение связанного с входной линией матрицы элемента связи, запирается через управляющий вход, в результате чего предотвращается дальнейший перезаряд входной линии матрицы. 4 ил.

Авторы

Даты

1994-05-30—Публикация

1990-07-20—Подача