Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств высокой производительности, обрабатывающих числа удвоенной точности.

Известно устройство сложения [1] , содержащее входные регистры, сдвигатель, сумматор порядков, сумматор мантисс, нормализатор результата, выходной регистр.

Недостатком устройства является низкое быстродействие.

Наиболее близким по технической сущности к изобретению является устройство сложения [2] , содержащее два входных регистра, дешифратор, входной сумматор порядков, сумматор, три регистра, нормализатор результата, формирователь порядка коррекции, узел управления нормализатором результата, выходной сумматор порядков, выходной регистр, узел сдвига мантиссы, причем входная шина первого операнда устройства через первый входной регистр соединена с информационным входом узла сдвига мантиссы, выход которого подключен через первый регистр к первому информационному входу сумматора, второй информационный вход которого соединен с выходом второго регистра, входная шина второго операнда устройства подключена к входу второго входного регистра, выход третьего регистра соединен с первым информационным входом нормализатора результата, первый управляющий вход которого подключен к выходу узла управления нормализатором результата, входная шина порядка первого операнда и входная шина порядка второго операнда устройства соединены соответственно с первым и вторым информационными входами входного сумматора порядков, выход которого подключен к первому управляющему входу узла сдвига мантиссы и к первому информационному входу выходного сумматора порядков, второй информационный вход которого соединен с выходом формирователя порядка коррекции, выход выходного сумматора порядков подключен к первому информационному входу выходного регистра, выход которого является шиной результата устройства, входная шина знака первого операнда, входная шина знака второго операнда и входная шина кода операций устройства соединены соответственно с одноименными входами дешифратора, выход которого соединен с вторым управляющим входом узла сдвига мантиссы.

Недостатком устройства является низкая производительность, обусловленная тем, что сложение чисел удвоенной точности выполняется за одну машинную команду, требует двенадцати тактов и устройство выдает результат один раз за девять тактов.

Целью изобретения является повышение производительности устройства.

Цель достигается тем, что в устройство для сложения, содержащее два входных регистра, дешифратор, входной сумматор порядков, сумматор, три регистра, нормализатор результата, формирователь порядка коррекции, узел управления нормализатором результата, выходной сумматор порядков, выходной регистр, узел сдвига мантиссы, причем входная шина первого операнда устройства через первый входной регистр соединена с информационным входом узла сдвига мантиссы, выход которого подключен через первый регистр к первому информационному входу сумматора, второй информационный вход которого соединен с выходом второго регистра, входная шина второго операнда устройства подключена к входу второго входного регистра, выход третьего регистра соединен с первым информационным входом нормализатора результата, первый управляющий вход которого подключен к выходу узла управления нормализатором результата, входная шина порядка первого операнда и входная шина порядка второго операнда устройства соединены соответственно с первым и вторым информационными входами входного сумматора порядков, выход которого подключен к первому управляющему входу узла сдвига мантиссы и к первому информационному входу выходного сумматора порядков, второй информационный вход которого соединен с выходом формирователя порядка коррекции, выход выходного сумматора порядков подключен к первому информационному входу выходного регистра, выход которого является шиной результата устройства, входная шина знака первого операнда, входная шина знака второго операнда и входная шина кода операций устройства соединены соответственно с одноименными входами дешифратора, выход которого соединен с вторым управляющим входом узла сдвига мантиссы, введены дополнительный узел сдвига мантиссы, два коммутатора, три дополнительных регистра, сдвигатель, формирователь сигнала обращения результата, при этом выход первого входного регистра соединен с первым информационным входом первого коммутатора, второй информационный вход которого и информационный вход дополнительного узла сдвига мантиссы подключены к выходу второго входного регистра, выход первого коммутатора через первый дополнительный регистр соединен с информационным входом сдвигателя, управляющий вход которого, управляющий вход коммутатора и первый управляющий вход дополнительного узла сдвига мантиссы подключены к выходу входного сумматора порядков, выход сумматора соединен с входом второго дополнительного регистра, выход которого подключен к входам формирователя порядка коррекции и узла управления нормализатором результата, к первым информационным входам формирователя сигнала обращения результата и второго коммутатора, выход которого соединен с входом третьего регистра, выход сдвигателя соединен с входом третьего дополнительного регистра, выход которого подключен к вторым информационным входам второго коммутатора и нормализатора результата, выход которого соединен с информационным входом узла обращения, выход которого подключен к второму информационному входу выходного регистра, выход дешифратора соединен с вторыми управляющими входами дополнительного узла сдвига мантиссы и нормализатора результата, с управляющим входом второго коммутатора, с вторым и третьим информационными входами формирователя сигнала обращения результата, выход которого подключен к управляющему входу узла обращения, кроме того, узел сдвига мантиссы содержит сдвигатель с инверсным выходом и элемент 2И-НЕ, причем информационный вход узла сдвига мантиссы соединен с информационными входами сдвигателя и элемента 2И-НЕ, первый и второй управляющие входы узла являются соответственно управляющими входами сдвигателя и элемента 2И-НЕ, выходы которых соединены и являются выходом узла сдвига мантиссы.

Сущность изобретения заключается в конвейерной организации устройства за счет разделения процесса сложения старших и младших частей числа. Введение первого коммутатора, первого дополнительного регистра, сдвигателя, второго дополнительного регистра, второго коммутатора, формирователя сигнала обращения результата позволяет осуществлять новые команды - сложение с выдачей младших и с выдачей старших частей числа. При этом старшие и младшие части удвоенного числа обрабатываются отдельно, что приводит к организации конвейера с частотой в один такт.

Сравнение заявляемого технического решения с прототипом позволило установить его соответствие критерию "новизна". При изучении других технических решений в данной области техники признаки, отличающие изобретение от прототипа, не были выявлены, поэтому они обеспечивают заявляемому техническому решению соответствие критерию "изобретательский уровень".

Математическое моделирование, а также предварительные испытания устройства показали возможность промышленной применимости изобретения.

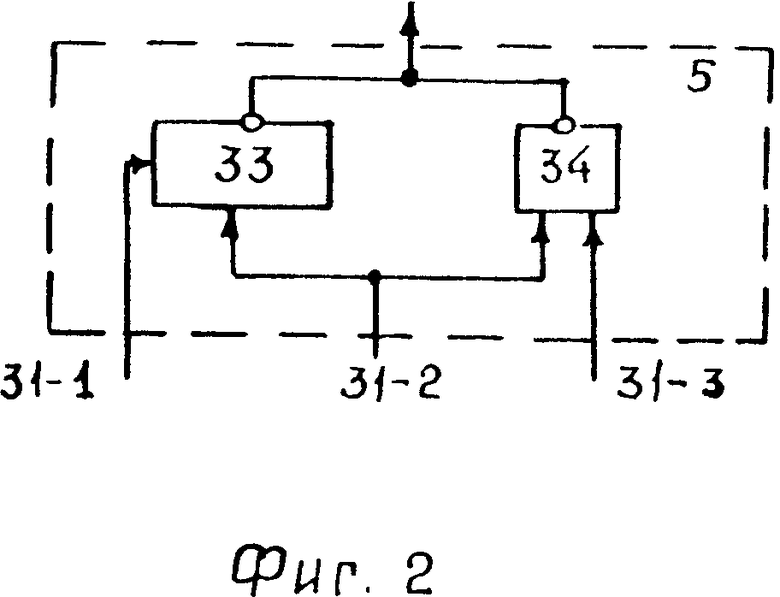

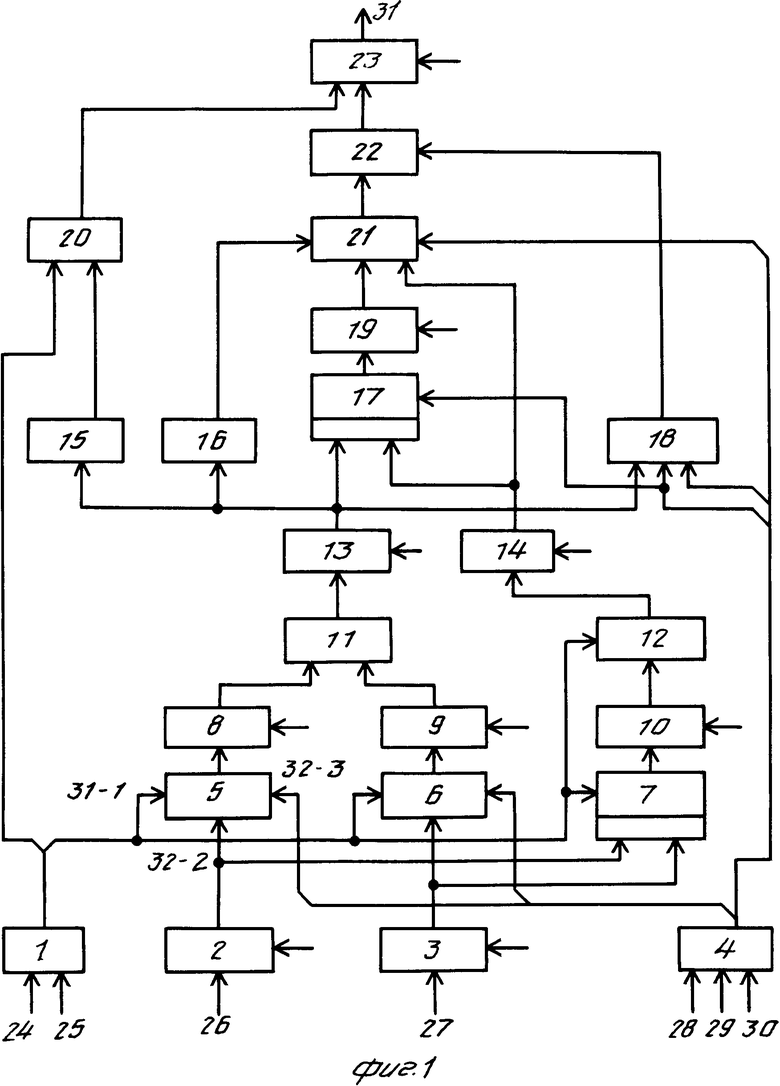

На фиг. 1 представлена блок-схема устройства для сложения; на фиг. 2 - узел сдвига мантиссы.

Устройство для сложения содержит входной сумматор 1 порядков, первый и второй входные регистры 2 и 3, дешифратор 4, узел 5 сдвига мантиссы, дополнительный узел 6 сдвига мантиссы, первый коммутатор 7, первый и второй регистры 8 и 9, первый дополнительный регистр 10, сумматор 11, сдвигатель 12, второй и третий дополнительные регистры 13 и 14, формирователь 15 порядка коррекции, узел 16 управления нормализатором результата, второй коммутатор 17, формирователь 18 сигнала обращения результата, третий регистр 19, выходной сумматор 20 порядков, нормализатор 21 результата, узел 22 обращения, выходной регистр 23.

В устройстве имеются входная шина 24 порядка первого операнда, входная шина 25 порядка второго операнда, входная шина 26 первого операнда, входная шина 27 второго операнда, входная шина 28 знака первого операнда, входная шина 29 знака второго операнда, входная шина 30 кода операций, выходная шина 31 результата.

Узел сдвига мантиссы имеет первый управляющий вход 32-1, информационный вход 32-2, второй управляющий вход 32-3 и содержит сдвигатель 33 с инверсным выходом и элемент 2И-НЕ 34.

Входная шина 24 порядка первого операнда подключена к первому информационному входу входного сумматора 1 порядков. Входная шина 25 порядка второго операнда соединена с вторым информационным входом сумматора 1. Входом первого входного регистра 2 является входная шина 26 первого операнда. Входом второго входного регистра 3 является входная шина 27 второго операнда. Входом знака первого операнда, входом знака второго операнда, входом кода операций дешифратора 4 являются соответственно одноименные шины 28, 29, 30 устройства. Выход входного сумматора 1 порядков соединен с первым информационным входом выходного сумматора 20 порядков, с первыми управляющими входами узлов 5, 6 сдвига мантиссы, с управляющими входами сдвигателя 12 и первого коммутатора 7. Выход первого входного регистра 2 подключен к информационному входу узла 5 сдвига мантиссы и к первому информационному входу первого коммутатора 7. Выход второго входного регистра 3 соединен с информационным входом дополнительного узла 6 сдвига мантиссы и с вторым информационным входом первого коммутатора 7. Выход узла 5 сдвига мантиссы через регистр 8 подключен к первому информационному входу сумматора 11. Выход дополнительного узла 6 сдвига мантиссы через регистр 9 соединен с вторым информационным входом сумматора 11. Выход сумматора 11 через регистр 13 подключен к входам формирователя 15 порядка коррекции и узла 16 управления нормализатором результата, к первым информационным входам второго коммутатора 17 и формирователя 18 сигнала обращения результата. Выход формирователя 15 порядка коррекции соединен с вторым информационным входом выходного сумматора 20 порядков, выход которого подключен к первому информационному входу выходного регистра 23. Выход первого коммутатора 7 соединен через регистр 10 с информационным входом сдвигателя 12. Выход второго коммутатора 17 подключен через регистр 19 к первому информационному входу нормализатора 21 результата. Второй информационный вход нормализатора 21 результата соединен через регистр 14 с выходом сдвигателя 12. Выход узла 16 управления нормализатором результата подключен к первому управляющему входу нормализатора 21 результата, выход которого соединен с информационным входом узла 22. Выход дешифратора 4 подключен к управляющему входу коммутатора 17, к вторым управляющим входам узлов 5 и 6 сдвига мантиссы, нормализатора 21 результата, второму и третьему информационным входам формирователя 18 сигнала обращения результата. Выход формирователя 18 соединен с управляющим входом узла 22, выход которого подключен к второму информационному входу выходного регистра 23. Выход регистра 23 является выходной шиной 31 результата устройства.

Входной сумматор 1 порядков, сумматор 11, формирователь 15 порядка коррекции, узел 16 управления нормализатором результата, выходной сумматор 20 порядков могут быть выполнены как аналогичные устройства в прототипе. Коммутатор 7 выполнен по схеме обычного коммутатора с двух направлений. Сдвигатель 12 выполнен по схеме двухуровневого сдвигателя вправо, при этом формируются разряды, выталкиваемые за разрядную сетку.

Формирователь 18 сигнала обращения результата реализует следующую логику:

ОББРЕЗ= ВЫДМЛ*ОБРЧ*НОР*15СБН, где ВЫДМЛ - сигнал, говорящий о том, что выполняется операция сложения с выдачей младших;

ОБРЧ - перед суммированием производилось обращение одной из мантисс;

НОР - производится нормализация результата;

15СБН - в младшей тетраде суммы содержится хотя бы одна единица.

Нормализатор 21 результата представляет собой двухуровневой сдвигатель влево. Узел 22 обращения может быть выполнен на элементе ИСКЛЮЧИТЕЛЬНОЕ ИЛИ. Все входящие в устройство узлы могут быть выполнены на элементах серии И300Б.

В устройстве используется однофазная система синхронизации. Рассмотрим процесс сложения двух удвоенных чисел. Приняты следующие обозначения: первый операнд - число А, второй операнд - число В, результат сложения - число С, порядок первого операнда - ПА, порядок второго операнда - ПВ, знак первого операнда - ЗнА, знак второго операнда - ЗнВ, код операции - КОП.

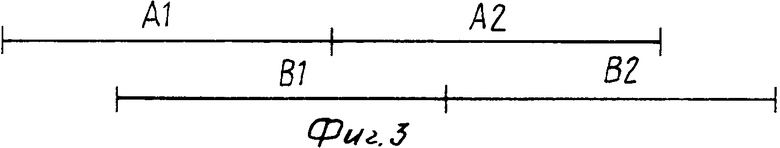

Число удвоенной точности задается двумя вещественными числами, каждое из которых содержит знак мантиссы, знак порядка, порядок и мантиссу. Первое число имеет тег старшей части удвоенного числа и содержит старшие разряды мантиссы, второе число имеет тег младшей части удвоенного числа и содержит младшие разряды мантиссы. Порядок первого числа на 14 больше порядка второго числа. Первое число должно быть нормализовано, кроме случая нулевой мантиссы.

Обозначим (А1, А2) пару чисел, задающую число А удвоенной точности, (В1, В2) число В удвоенной точности и (С1, С2) результат сложения двух чисел удвоенной точности. Введем две операции - сложение с выдачей младших (оно представляет собой обычное сложение, но в качестве результата выдаются разряды мантиссы, выдвинутые за разрядную сетку при выравнивании порядков, нулевым порядком является больший из порядков, уменьшенный на 14) и сложение с выдачей старших (это обычное сложение вещественных, но в этом случае не выполняется округление, которое обычно делается, когда при выравнивании порядков теряются разряды мантиссы с меньшим порядком). Тогда процесс сложения двух чисел удвоенной точности можно описать формулой

C

С M M

(С1, С2) = (А1 + В1) + (А1 + В1) + (А2 + В2),

4 5 2 3 1

6 где С - означает сложение с выдачей стар-

+ ших; М - сложение с выдачей младших,

+ + - обычное сложение, а цифры внизу - порядок выполнения команд. Каждая команда выполняется четыре такта.

Рассмотрим пример сложения двух удвоенных чисел. Пусть числа располагаются относительно друг друга как показано на фиг. 3.

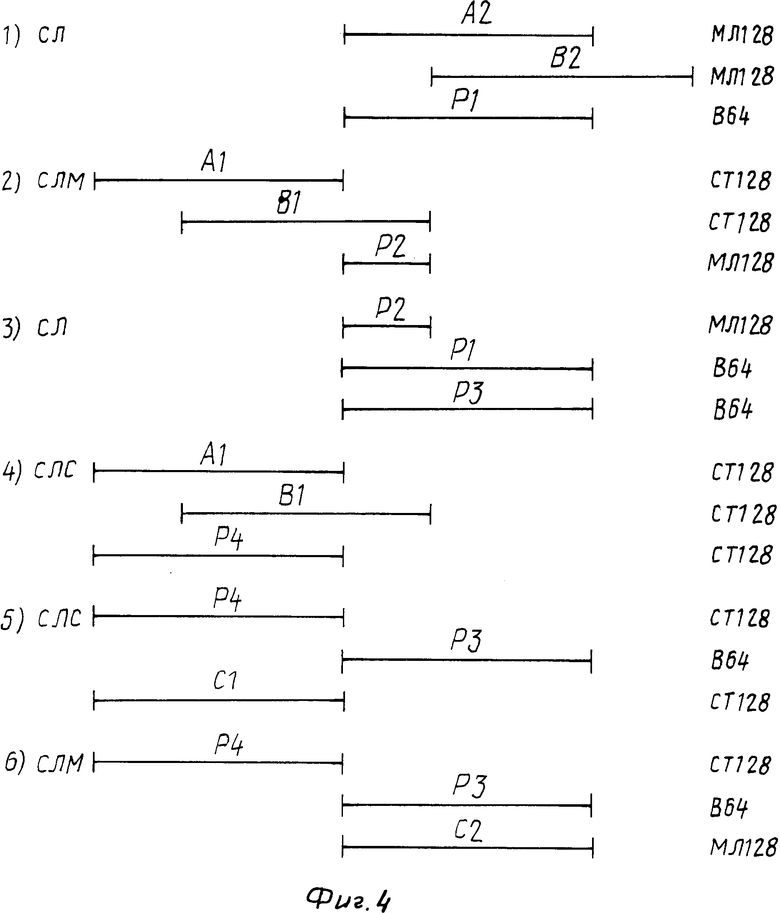

Тогда процесс сложения можно представить как показано на фиг. 4.

(слева написан код операции, справа - теги операндов и результата, Р1 - результат первой операции).

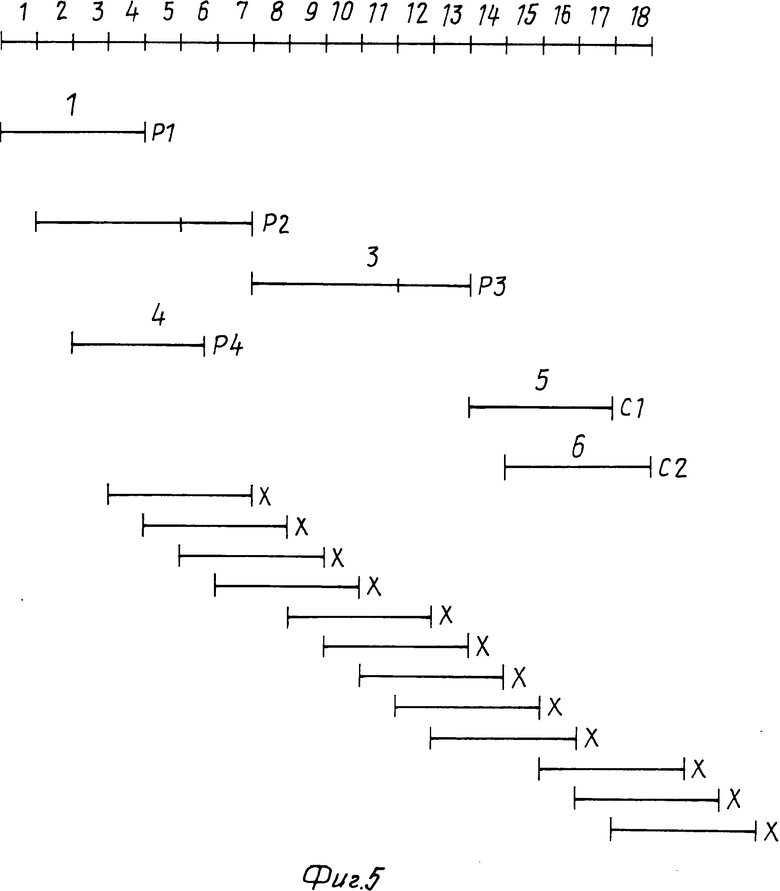

Процесс сложения удвоенных чисел занимает 18 тактов и развивается следующим образом (см. фиг. 5).

После второй и третьей команд отводятся два такта на доставку результата на вход устройства. Знаком Х помечены те промежутки времени, когда устройство свободно. Видно, что 12 из 18 тактов устройство свободно, т. е. в это время можно выполнять другие команды.

Устройство работает следующим образом.

При выполнении процесса удвоенного сложения на вход первого операнда (числа А) устройства подаются в разные моменты времени старшая и младшая части одного удвоенного числа А1 и А2 соответственно, на вход второго операнда (числа В) подаются старшая и младшая части другого удвоенного числа В1 и В2 соответственно.

При обычном сложении в устройство по шинам 26 и 27 приходят числа А и В, по шинам 24 и 25 - порядки ПА и ПВ, по шинам 28, 29 и 30 - соответственно знак левого и правого операндов и код операции. Порядки ПА и ПВ сравниваются в сумматоре 1, по разности порядков вырабатывается код сдвига левой мантиссы или правой мантиссы, который поступает на первый управляющий вход узлов 5 и 6 сдвига мантиссы соответственно. Мантиссы чисел с выхода регистров 2 и 3 поступают на первый информационный вход узлов 5 и 6 и на первый и второй информационные входы коммутатора 7. Мантиссы числа с меньшим порядком сдвигаются в узле 5 или 6, другая мантисса в случае необходимости обращается в узле 6 или 5 (сигналы ОБРЛ и ОБРП, которые вырабатываются из знаков мантисс ЗнА, ЗнВ и кода операции КОП в дешифраторе 4, поступают на второй управляющий вход узлов 5 и 6 соответственно). Далее мантиссы попадают в регистры 8 и 9, а затем в сумматор 11 на первый и второй информационные входы и регистр 13. Сборки нулей попадают в узел 16 управления и в формирователь 15 порядка коррекции. Порядок коррекции попадает на второй информационный вход выходного сумматора 20 порядков, где складывается с большим порядком, поступающим на его первый информационный вход, и дает порядок результата. Мантиссы из регистра 13 через первый информационный вход коммутатора 17 попадают на первый информационный вход нормализатора 21 результата, где в случае необходимости сдвигаются на величину СДН, поступающую на первый управляющий вход. В нормализаторе 21 происходит округление, если при выравнивании порядков за разрядную сетку попала хотя бы одна единица, о чем говорит сигнал, поступающий на второй информационный вход. В выходной регистр 23 на первый и второй информационные входы поступают порядок и мантисса результата. С выхода регистра 23 по шине 31 выходит результат.

Сложение с выдачей старших отличается от обычного сложения отсутствием округления.

Сложение с выдачей младших отличается от обычного сложения тем, что мантиссы с входных регистров 2 и 3 кроме узлов 5, 6 сдвига мантиссы попадают в коммутатор 7, через который проходит мантисса числа с меньшим порядком. Она проходит через регистр 10 на информационный вход сдвигателя 12, в котором формируются разряды мантиссы, выталкиваемые за разрядную сетку при выравнивании порядков. Затем эти разряды через регистр 14 и второй информационный вход коммутатора 17 попадают в нормализатор 21 результата. Там происходит сдвиг, который определяется по результату сложения разрядов мантисс, которые остались в разрядной сетке. Если было переполнение, то младшая тетрада из сумматора 11 попадает в старшую тетраду результата, а мантисса из регистра 14 сдвигается вправо на одну тетраду. Если в сумматоре 11 получились старшие нулевые тетрады, то происходит сдвиг мантиссы из регистра 14 влево, если сдвиг не нужен, то мантисса проходит через нормализатор 21 без изменений.

Если перед суммированием одна из мантисс обращалась, то в случае, когда старшая выдвинутая при выравнивании порядков за разрядную сетку тетрада отличается от нуля и не требуется нормализация, в формирователе 18 обращения результата происходит обращение мантиссы из регистра 14.

Знак результата операции сложения с выдачей младших совпадает со знаком результата обычного сложения с такими же операндами, но в случае необходимости нормализации и в случае отсутствия нормализации и нулевой старшей выдвинутой тетрады знак результата противоположен знаку результата соответствующей обычной операции сложения.

Порядок результата операции сложения с выдачей младших на регистр 14 меньше, чем при аналогичной операции обычного сложения.

Использование предлагаемого устройства обеспечивает по сравнению с существующим следующие преимущества. Старшие и младшие части удвоенного числа обрабатываются отдельно, что приводит к организации конвейера с частотой в один такт. Сложение чисел удвоенной точности выполняется за шесть команд и требует 18 тактов. Устройство выдает результат один раз в шесть тактов, т. е. в случае бесперебойной подачи операндов производительность предлагаемого устройства в 1,5 раза выше, чем устройства-прототипа, даже при одинаковой длительности такта. (56) 1. Процессор. Техническое описание МВК "Эльбрус-Б", часть 4. Арифметическое устройство И613.055.045. ТОЗ - М. : ИТМ и ВТ АН СССР, 1988, с. 84-124, рис. 5-22.

2. Процессор центральный. Техническое описание МВК "Эльбрус-2". Арифметические исполнительные устройства БМЗ. 050.037. ТОЭ - М. : ИТМ и ВТ АН СССР, 1982, с. 9-80, рис. 2-7.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ | 1992 |

|

RU2018921C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для сложения (I) | 1989 |

|

SU1837281A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Сумматор порядков чисел (II) | 1989 |

|

SU1837282A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств высокой производительности, обрабатывающих числа удвоенной точности. Устройство для сложения содержит два входных регистра, дешифратор, входной сумматор порядков, сумматор, три регистра, нормализатор результата, формирователь порядков коррекции, узел управления нормализатором результата, выходной сумматор порядков, выходной регистр, узел сдвига мантиссы. Новым является введение дополнительного узла сдвига мантиссы, двух коммутаторов, трех дополнительных регистров, сдвигателя, формирователя сигнала обращения результата. Введение новых блоков позволяет повысить производительность за счет конвейерной организации устройства путем разделения процесса сложения старших и младших частей чисел. 1 з. п. ф-лы. , 5 ил.

Авторы

Даты

1994-01-30—Публикация

1991-12-27—Подача