Изобретение относится к вычислительной технике и может быть использовано в устройствах адресации памяти в средствах вычислительной техники.

В качестве устройства, выбранного прототипом к предлагаемому изобретению, принимается устройство, соcтоящее из n регистров условных адресов и n схем сравнения (где n - количество блоков памяти), регистра последнего адреса, схемы сравнения последних адресов, счетчиков условных и физических адресов, мультилексора и дешифратора.

Недостатками данного способа и устройства являются большие затраты на оборудование устройств, реализованных по данному способу, в случае повышения эффективности конфигурации памяти (число блоков памяти обратно пропорционально их емкости).

Целью изобретения является повышение эффективности устройств для адресации памяти при сравнительно небольших затратах на оборудование.

Устройство конфигурации памяти, реализующее предложенный способ, содержащее n линеек элементов, где n - число разрядных шин адреса, в каждую линейку входит регистр порядковых номеров разрядов адреса, схема сравнения, соединенная информационными входами с различными шинами адреса и выходами регистра неисправной области памяти, и блок управления, вводятся в каждую линейку первые и вторые триггеры, элементы И, сумматоры по модулю два и мультиплексор, причем входная разрядная шина адреса соединена с инверсным входом второго триггера и первыми входами сумматоров по модулю два, второй вход и выход первого сумматора по модулю два соединены соответственно с выходом второго триггера и входом первого элемента И, другой вход и выход последнего соединены соответственно с выходом и информационным входом первого триггера, первый и второй входы второго элемента И соединены соответственно с выходами первого и второго триггеров, второй вход и выход второго сумматора по модулю два соединены соответственно с выходом второго элемента И и соответствующими порядковому номеру разряда адреса информационными входами мультиплексоров, адресные входы которых соединены с выходами соответствующих регистров линеек, информационные и синхронизирующие входы последних соединены соответственно с адресными и соответствующими разрядными выходами блока управления, первый, второй и третий выходы и входы данных последнего соединены соответственно с третьими входами вторых элементов И, с синхронизирующими и установочными входами первых и вторых триггеров, синхронизирующим входом первых триггеров и выходами последних, информационные, управляющие и сбросовый входы регистра области неисправной памяти соединены соответственно с разрядными, четвертым и пятым выходами блока управления, шестой и седьмой выходы последнего соединены соответственно с управляющим входом схемы сравнения и шиной "Занято", выходы мультиплексоров и схемы сравнения соединены с соответствующими разрядными шинами адреса памяти и шиной "Недействительный адрес". Существенными признаками предлагаемых изобретений являются изменения порядка подключения разрядных шин условных адресов к шинам физического адреса памяти с инвертированием сигналов отмеченных разрядов, имеющих нулевые значения сигналов, причем отмеченные разряды подключаются к шинам старших разрядов физического адреса.

Данные операции проводятся с целью создания адресного пространства неисправной области памяти, смещенной в сторону старших разрядов и выраженной единичными значениями старших разрядов условных адресов памяти. Обращение к области неисправной памяти блокируется сигналом "Недействительный адрес".

Покажем на примере выполнение операций для адресации памяти.

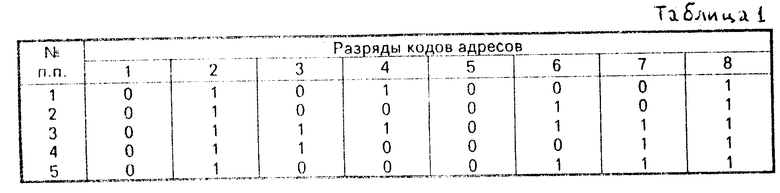

Ниже приведена таблица 1 кодов неисправных ячеек памяти.

Отмеченные разряды кодов условных адресов - 1, 2, 5, 8.

В таблице 2 приведен порядок подключения шин физических адресов к шинам условных адресов после проведения операций адресации.

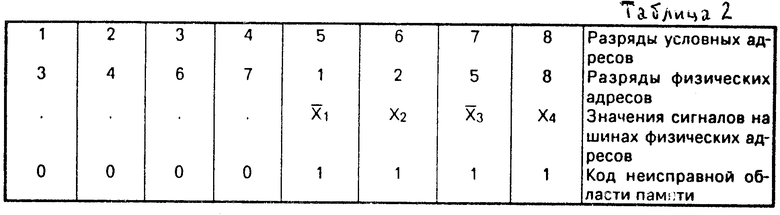

На фиг.1 представлена структурная схема включения устройства в систему процессор - оперативная память, на которой изображены процессор 1, устройство 2 конфигурации памяти и оперативная память 3.

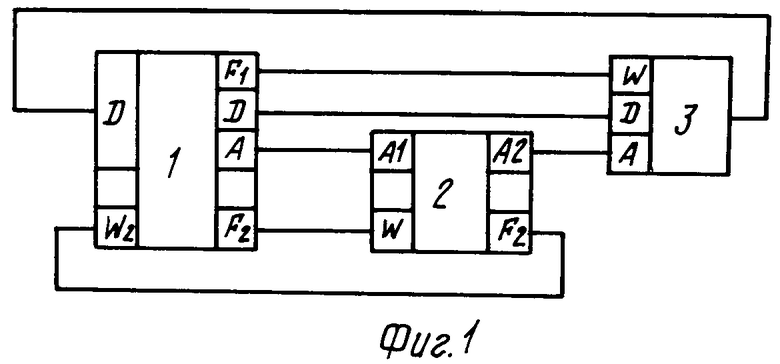

На фиг.2 представлена функциональная схема каналов преобразования адресов, на которой изображены первая группа элементов И 41, 42,...,4i, 4i+1,.. . , 4k, первая группа сумматоров по модулю два 51, 52,...,5i, 5i+1,...,5k, регистр отмеченных разрядов кодов условных адресов, состоящий из триггеров 61, 62,..,6i, 6i+1,...,6k, регистр адресного кода первой неисправной ячейки памяти, состоящий из триггеров 71, 72,...,7i, 7i+1,...,7k, вторая группа элементов И 81, 82,...,8i, 8i+1,...,8k, вторая группа сумматоров по модулю два 91, 92,...,9i, 9i+1,...,9k, группа регистров условных адресов 101, 102, ...,10i, 10i+1,...,10k и группа мультиплексоров подключения шин физического адреса 111, 112,...,11i, 11i+1,...,11k, блок 12 управления, регистр 13 области неисправной памяти и блок 14 сравнения.

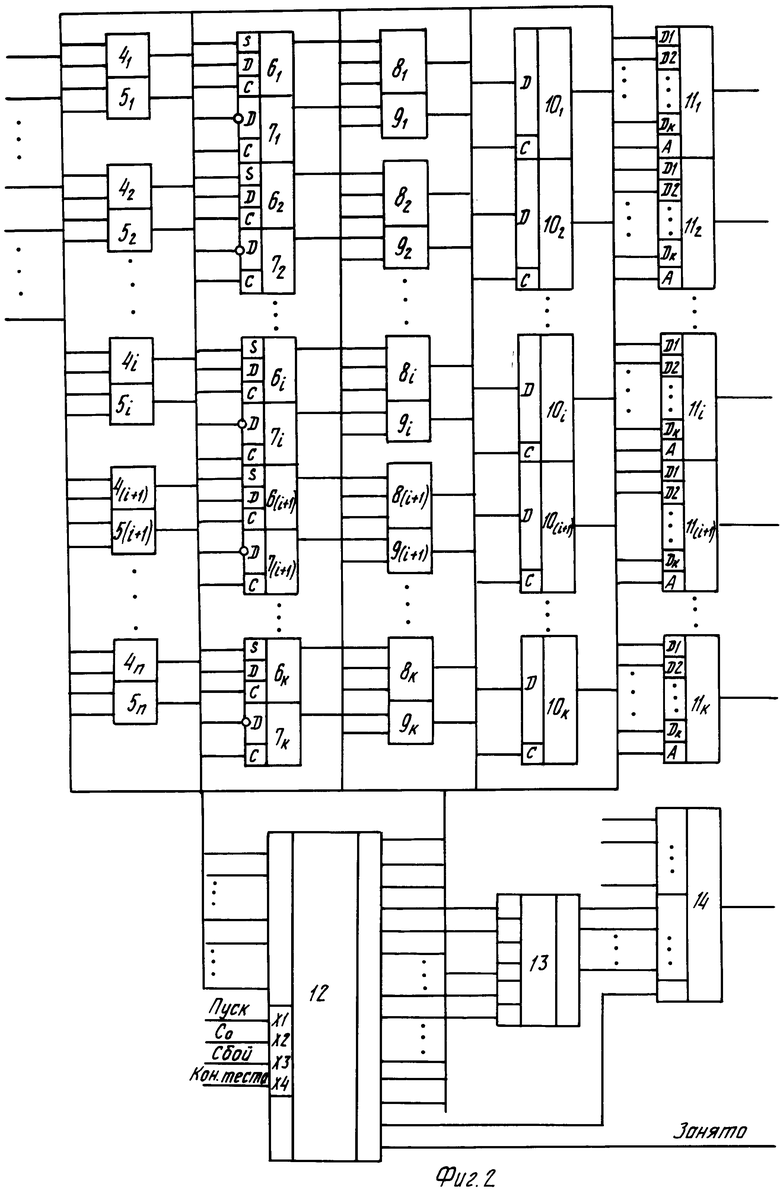

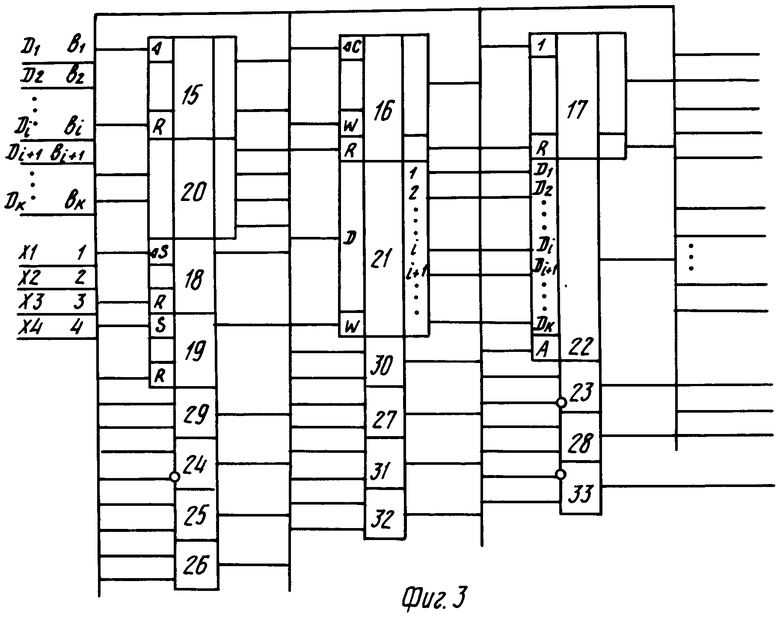

На фиг.3 представлена функциональная схема блока 12 управления, включающая счетчик 15 операций, двоичный счетчик 16, счетчик 17 переадресации, триггер 18 конфигурации, триггер 19 синхронизации, дешифратор 20 операций, дешифратор 21, мультиплексор 22, сумматор по модулю два 23, элементы И 24-28 и элементы ИЛИ 29-33.

На фиг.4 представлен алгоритм работы устройства.

Рассмотрим назначение узлов схем устройства. Группы элементов И 41,..., 4k и сумматоров по модулю два 51,...,5k предназначены для отметки разрядов входного кода адреса. Отметка разрядов осуществляется путем гашения триггеров 61, ...,6k в случае несравнения значений разрядов входного кода адреса со значением соответствующих разрядов в регистре, включающем триггеры 71,.. .,7k (при обнаружении первой неисправной ячейки памяти в процессе тестового контроля в регистре триггеров 61,...,6kустанавливаются единичные значения, а в регистре триггеров 71, ...,7k - инверсные значения кода адреса). После окончания тестового контроля единичные значения, установленные на соответствующих триггерах 61,...,6k, соответствуют отмеченным разрядам входного кода адреса. Группы элементов И 81,...,8k и сумматоров по модулю два 91,..., 9k служат для инвертирования отмеченных разрядов кода адреса, соответствующих кодам 11, установленных на соответствующих триггерах 6, 7. Группа регистров 101,...,10k необходима для хранения порядковых номеров разрядных шин входного кода адреса, подключенного через мультиплексоры 111,...,11k к шинам адреса памяти.

Блок 12 управления служит для выработки управляющих сигналов, необходимых для формирования отмеченных разрядов входных шин адреса, занесения кодов в регистры 101,...,10k и формирования кода неисправностей области памяти.

Регистр 13 необходим для хранения кода неисправной области памяти.

Блок 14 сравнения предназначен для сравнения кода на шинах входного адреса с кодом информации, установленной в регистре 13, и в случае, если последний код меньше первого, вырабатывается сигнал "Недействительный адрес".

Счетчик 15 служит для задания кодов режимов работы устройства. Различаются следующие режимы работы:

код 00 - режим установки последовательно возрастающих кодов порядковых номеров разрядных шин адреса в соответствующие регистры 101,...,10k. Данный режим предназначен для подготовки устройства к тестовой проверке памяти;

код 01 - режим отметки разрядов входного адреса;

код 10 - режим установки в регистры 101,...,10k последовательно возрастающих кодов порядковых номеров шин адреса, соответствующих неотмеченным разрядам;

код 11 - режим установки в регистры 101,...,10k последовательно возрастающих кодов порядковых номеров шин адреса, соответствующих отмеченным разрядам.

Счетчик 16 предназначен для определения кодов порядковых номеров шин адреса при занесении информации в соответствующие регистры 101,...,10k.

Счетчик 17 служит для выработки кодов адреса порядковых номеров регистров 101,...,10k, определяющих занесение информации в последние.

Триггер 18 предназначен для фиксации условия конфигурации памяти, устанавливается в состояние "1" при обнаружении в последней неисправных ячеек.

Триггер 19 необходим для выработки сигналов синхронизации в режимах, определенных кодами 00, 10, 11, установленными на счетчике 15.

Дешифратор 20 операций предназначен для дешифрации кодов, установленных на счетчике 15.

Дешифратор 21 необходим для выработки сигналов занесения информации в регистры 101,...,10k и 13.

Мультиплексор 22 служит для выработки разрешающих сигналов, возбуждающих счетный вход счетчика 17, и управляющего входа дешифратора 21.

Сумматор 23 по модулю два и элементы И 24,...,28 и ИЛИ 22,...,33 предназначены для возбуждения управляющих входов счетчиков 16, 15, 17, триггеров 18 и 19 и дешифратора 21 при выполнении устройством различных режимов работы.

Для рассмотрения работы устройства введем обозначения переменных Х и функций Y блока 12 управления. Х1 - входной сигнал "Пуск"; Х2 - сигнал синхронизации Со; Х3 - сигнал "Сбой", Х4 - сигнал "Конец теста"; Х5 - сигнал переполнения счетчика 17; Х6 - сигнал переполнения счетчика 16; Х7 - выходной сигнал мультиплексора 22; Y1 - сигнал возбуждения счетного входа счетчика 16; Y2 - сигнал возбуждения управляющего входа счетчика 16; Y3 - сигнал гашения счетчика 16; Y4 - сигнал возбуждения счетного входа счетчика 17; Y5 - сигнал гашения счетчика 17; Y6 - сигнал возбуждения счетного входа счетчика 15; Y7 - сигнал гашения счетчика 15; Y8 - выходной сигнал "Занято"; Y9 - сигнал управления дешифратора 21; Y10 - сигнал установки в "1" триггера 19; Y11 - сигнал гашения триггера 19; Y12 - сигнал установки в "1" триггера 18; Y13 - сигнал гашения триггера 19; Y14 - выходной сигнал установки кода адреса на триггерах 71,...,7k и единичных значений на тpиггерах 61, ...,6k; Y15 - сигнал гашения триггеров 61,...,6k, соответствующих разрядам триггеров 71,...,7k, не совпадающих в режиме отметки с сигналами на соответствующих разрядах входных шин адреса.

Работа устройства осуществляется в соответствии с алгоритмом, представленным на фиг.4.

Рассмотрим работу устройства.

В состоянии 1 проверяется условие Х1 = 1, при выполнении которого устройство переходит в состояние 2. В состоянии 2 вырабатываются функции Y3, Y5, Y7, Y10, Y13 = =1 и устройство переходит в состояние 3.

В состоянии 3 проверяется условие Х2 = =1, при выполнении которого устройство переходит в состояние 4, в противном случае - в состояние 6.

В состоянии 4 проверяется условие Х7 = =1, при выполнении которого устройство переходит в состояние 5, в противном случае - в состояние 3.

В состоянии 5 вырабатываются функции Y1, Y2, Y4 = 1 и устройство переходит в состояние 3.

В состоянии 6 проверяется условие Х5 = =1, при выполнении которого устройство переходит в состояние 7, в противном случае - в состояние 3.

В состоянии 7 вырабатываются функции Y6, Y11 = 1 и устройство переходит в состояние 8.

В состоянии 8 проверяется условие Х4 = =1, при выполнении которого устройство переходит в состояние "Конец конфигурации", в противном случае - в состояние 9.

В состоянии 9 проверяется условие Х3 = =1, при выполнении которого устройство переходит в состояние 10, в противном случае - в состояние 8.

В состоянии 10 вырабатываются функции Y12, Y14, Y15 = 1 и устройство переходит в состояние 11.

В состоянии 11 проверяется условие Х3 = 1, при выполнении которого устройство переходит в состояние 12, в противном случае - в состояние 13.

В состоянии 12 вырабатывается функция Y14 = 1 и устройство переходит в состояние 11.

В состоянии 13 проверяется условие Х4 = 1, при выполнении которого устройство переходит в состояние 14, в противном случае - в состояние 11.

В состоянии 14 вырабатываются функции Y6, Y10 = 1 и устройство переходит в состояние 15.

В состоянии 15 проверяется условие Х2 = 1, при выполнении которого устройство переходит в состояние 16.

В состоянии 16 вырабатываются функции Y1, Y2 = 1 и устройство переходит в состояние 17.

В состоянии 17 проверяется условие Х7 = 1, при выполнении которого устройство переходит в состояние 18, в противном случае - в состояние 15.

В состоянии 18 вырабатываются функции Y1, Y2, Y4, Y9 = 1 и устройство переходит в состояние 19.

В состоянии 19 проверяется условие Х6 = 1, при выполнении которого устройство переходит в состояние 20, в противном случае - в состояние 15.

В состоянии 20 проверяется условие Х2 = 1, при выполнении которого устройство переходит в состояние 24.

В состоянии 21 вырабатываются функции Y1, Y2 = 1 и устройство переходит в состояние 22.

В состоянии 22 проверяется условие Х7 = 1, при выполнении которого устройство переходит в состояние 23, в противном случае - в состояние 20.

В состоянии 23 вырабатываются функции Y1, Y2, Y3, Y9 = 1 и устройство переходит в состояние 20.

В состоянии 24 проверяется условие Х5 = 1, при выполнении которого устройство переходит в состояние 25, в противном случае - в состояние 20.

В состоянии 25 вырабатываются функции Y3, Y7, Y11 = 1 и устройство переходит в состояние "Конец конфигурации".

Положительным эффектом от использования предлагаемого изобретения является повышение эффективности конфигурации памяти при сравнительно низких затратах на оборудование.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля монтажа | 1990 |

|

SU1785001A1 |

| Устройство для формирования и хранения адресов команд | 1984 |

|

SU1182578A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля микропроцессора | 1987 |

|

SU1444783A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Устройство микропрограммного управления | 1990 |

|

SU1791817A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Устройство для проверки монтажа | 1987 |

|

SU1509937A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Арифметико-логическое устройство со встроенной диагностикой | 1984 |

|

SU1275426A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах для адресации памяти в средствах вычислительной техники. Целью изобретения является повышение эффективности устройств конфигурации при сравнительно небольших затратах на оборудование. Цель достигается тем, что в процессе тестового контроля памяти производится фиксация в регистрах кодов адресов неисправных ячеек памяти, осуществляется отметка в зафиксированных кодах адресов разрядов, имеющих неизменные единичные и нулевые значения, с последующим инвертированием последних. Путем переключения адресных шин производится изменение порядковых номеров разрядов адреса таким образом, чтобы отмеченные разряды соответствовали старшим разрядам адреса памяти, причем данные разряды фиксируются единичными значениями в старших разрядах регистра области неисправной памяти. При работе устройства производится сравнение входного кода адреса с кодом, установленным в регистре неисправной области памяти, и, если последний код меньше входного кода, вырабатывается сигнал "Недействительный адрес", блокирующий обращение к памяти. 4 ил., 2 табл.

УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ, содержащее группу регистров порядковых номеров разрядов адреса, регистр адреса первой неисправной ячейки, выходы которого соединены с первыми входами элементов И первой группы, регистр кода неисправной области памяти, выходы которого подключены к первой группе информационных входов блока сравнения, и блок управления, отличающееся тем, что, с целью повышения эффективности устройства за счет уменьшения числа незадействованных ячеек памяти, в него введены вторая группа элементов И, группы сумматоров по модулю два, регистр отмеченных разрядов условных адресов и группа мультиплексоров, первые входы сумматоров по модулю два первой группы соответственно объединены с второй группой информационных входов блока сравнения, с информационными входами регистра адреса первой неисправной ячейки и первыми входами сумматоров по модулю два второй группы и являются входами устройства, выходы сумматоров по модулю два второй группы подключены к информационным входам всех мультиплексоров группы, выходы которых являются адресными выходами устройства, вторые входы сумматоров по модулю два первой группы соединены с выходами регистра адреса первой неисправной ячейки, а выходы - с первыми входами элементов И второй группы, выходы которых подключены к информационным входам регистра отмеченных разрядов условных адресов, выходы которого соединены со вторыми входами элементов И первой и второй групп и информационными входами блока управления, первая группа выходов которого подключена соответственно к третьим входам элементов И первой группы, входами сброса регистра отмеченных разрядов условных адресов, информационными и синхровходам регистра порядковых номеров разрядов адреса, управляющему и установочному входам регистра неисправной области памяти и выходу "Занято" устройства, вторая группа выходов блока управления соединена соответственно с синхровходами регистров отмеченных разрядов условных адресов, адреса первой неисправной ячейки, порядковых номеров разрядов адреса, кода неисправной области памяти и разрешающим входом блока сравнения, выход которого является выходом "Недействительный адрес" устройства, третья группа выходов блока управления подключена к соответствующим информационным входам регистра кода неисправной области памяти, выходы регистра порядковых номеров разрядов адреса и выходы элементов И первой группы соединены с соответствующими вторыми входами сумматоров по модулю два второй группы.

| Устройство для адресации блоков памяти | 1980 |

|

SU1024926A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-09-30—Публикация

1990-08-23—Подача