IS

(Л

с

4ib 4аь 4 «Ч

Изобретение относится к области вычислительной техники и может найти применение при построении надежньк микропроцессорных систем.

Цель изобретения - повышение быстродействия устройства.

На чертеже представлена функциональная схема устройства для контроля микропроцессора.

Устройство для контроля микропроцессора содержит счетчик 1, схему 2 сравнения, первый элемент И 3, первый регистр 4, блок 5 постоянной памяти, сумматор 6, второй регистр 7, мультиплексор 8, второй 9, третий 10 и четвертый 11 элементы И, первый 12 и второй 13 триггеры, элемент НЕ 14, контролируемый микропроцессор 15, выход неисправности устройства 16.

Устройство работает следующим образом.

После включения питания в схеме контролируемого микропроцессора 15 формируется Сигнал сброса.RESET, который через шину управления поступает на входы сброса счетчика 1, второго регистра 7 и триггеров 12, 13,

байт поступит на адресные входы блока 5 постоянной памяти. В результате чего на его основном выходе будет

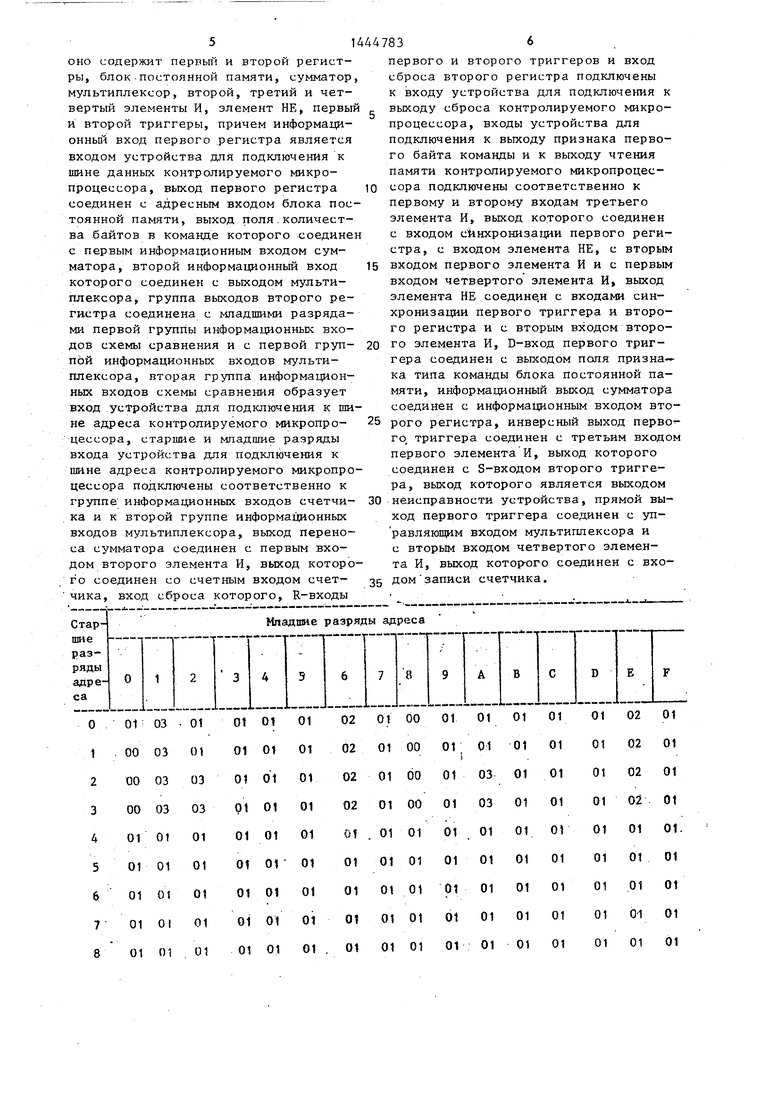

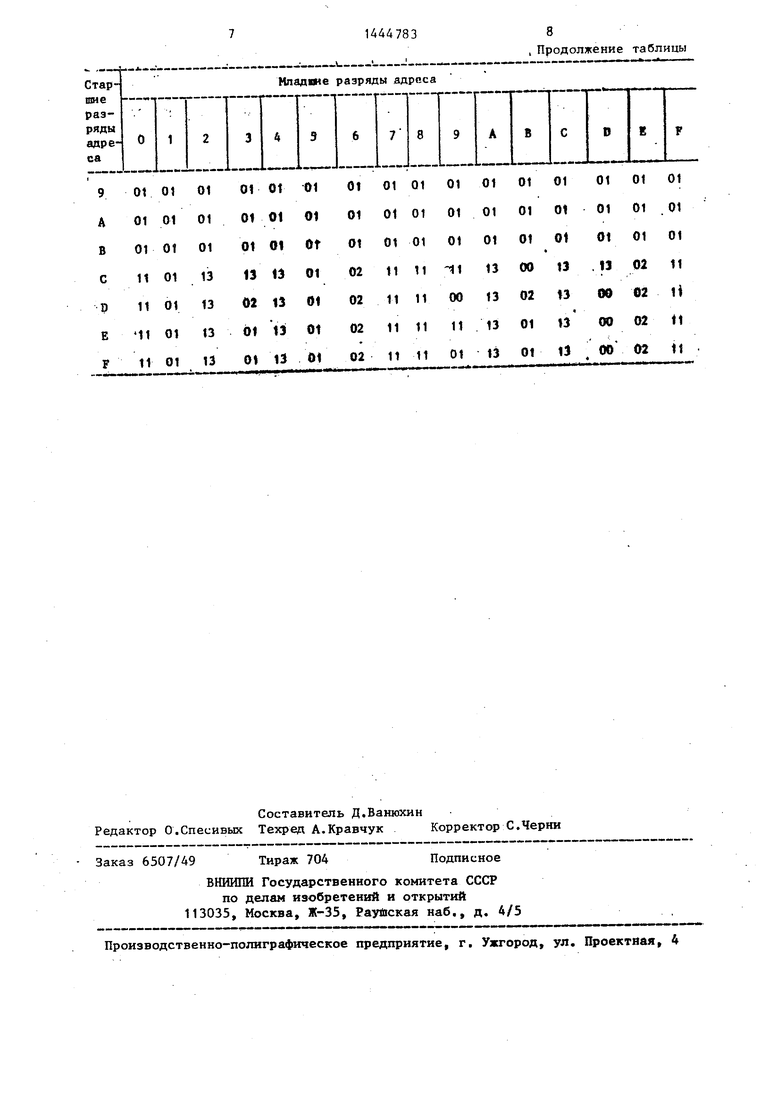

- установлен код, равный количеству байт в команде, а на дополнительном выходе код типа команды (операционная команда - команда перехода). В частности, для контроля микропроцес10 сора серии ЮР58О коды, хранимые в блоке 5 постоянной памяти, должны соответствовать данным, приведенным в таблице. Каждая клеточка этой таблицу соответствует одному из 256

15 возможных адресов.. Строки таблицы

соответствуют 16 возможным состояниям старших разрядов адреса, а столбцы - 16 возможным состояниям младших разрядов адреса (номера строк и столбцов

20 указаны шестнадцатиричными числами). Код в каждой клетке состоит из двух цифр. Левая цифра соответствует состоянию дополнительного выхода блока 5 постоянной памяти и равна единице,

25 если адресный байт соответствует команде перехода, в противном случае - равна нулю. Правая цифра соответствует десятиричному эквиваленту двоичного кода, формируемого на основном что приводит к их установке в нулевое 30выходе блока 5 постоянной памяти, и состояние. Одновременно счетчик ко-равна количеству байт (1, 2 или 3) манд микропроцессора 15 также уста-команды микропроцессора 15. Таким навливается в нулевое состояние. За-образом, на выходах блока 5 постоян- тем микропроцессор 15 начинает после-ной памяти непосредственно после довательную выборку и исполнение ко- jSмомента фиксации первого байта оче- манд по заданной программе. Дпя мик-редной команды в первом регистре 4 ропроцессора серии КР580 последниебудет установлен код в соответствии могут быть однобайтными, двухбайтны-с данными таблицы. В результате воз- ми и трехбайтными. В результате это-можны две-ситуации: очередная коман- го адрес следуюш,ей команды может быть40да не является командой перехода, больше адреса предьдущей команды со-очередная команда - команда перехода, ответственно на одну, две или три В первом случае на вход D первого единицы младшего разряда при условии1триггера 12 поступит сигнал О и по правильного функционирования микро-окончании сигнала с выхода третьего процессора. Кроме того, в системе ко-дзэлемента И 10 первый триггер 12 не избайт поступит на адресные входы блока 5 постоянной памяти. В результате чего на его основном выходе будет

установлен код, равный количеству байт в команде, а на дополнительном выходе код типа команды (операционная команда - команда перехода). В частности, для контроля микропроцессора серии ЮР58О коды, хранимые в блоке 5 постоянной памяти, должны соответствовать данным, приведенным в таблице. Каждая клеточка этой таблицу соответствует одному из 256

возможных адресов.. Строки таблицы

соответствуют 16 возможным состояниям старших разрядов адреса, а столбцы - 16 возможным состояниям младших разрядов адреса (номера строк и столбцов

указаны шестнадцатиричными числами). Код в каждой клетке состоит из двух цифр. Левая цифра соответствует состоянию дополнительного выхода блока 5 постоянной памяти и равна единице,

если адресный байт соответствует команде перехода, в противном случае - равна нулю. Правая цифра соответствует десятиричному эквиваленту дво

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Программируемый контроллер | 1986 |

|

SU1328815A1 |

Изобретение относится к вычисЛ1Т - тельной технике и может найти применение при построении надежных микропроцессорных систем. Цель изобретения - повышение быстродействия устройства. Устройство для контроля микропроцессора содержит счетчик 1, схему сравнения 2, первый элемент И 3, первый регистр 4, блок постоянной памяти 5, сумматор 6, второй регистр 7, мультиплексор 8, второй 9, третий 10 и четвертый 11 элементы И, первый 12 и второй 13 триггеры и элемент НЕ 14. 1 ил. 1 табл.

манд микропроцессора имеются команды переходов (ветвлений) ,. которые могут скачком изменять содержимое счетчика команд микропроцессора. Момент считывания первого байта команды легко идентифицируется по совпадению сигналов на линиях выборки первого байта команды (Ml) и чтения памяти (MEMR) шины управления микропроцессора 15. В этот момент сработает третий элемент И 10 и код- первого байта команды, установленный в это время на пине данных, будет зафиксирован в первом регистре 4. Этот

0

5

менит своего состояния. Код байтности очередной команды с основного выхода блока 5 постоянной памяти постудит на первый вход сумматора 6, а на второй его вход через мультиплексор 8 поступит код из второго регистра 7. По этим данным сумматор 6 формирует сумму и перенос (для микропроцессора КР580 мультиплексор 8, сумматор 6 и регистр 7 содержат по два двоичных разряда, так как двоичный код. байт-, ности может быть только 01,10 или 11) Сумма поступит на вход BTopoVo регистра 7 и будет записана в него по

заднему фронту сигн.гпа с выхода третьего элемента И 10 благодаря элементу НЕ 14, Сигнал с выхода последнего пройдет также на вход инкрементиро- вания счетчика 1 через второй элемен И 9, если значение переноса на выходе сзт матора 6 будет равно 1. Таки образом, в счетчике 1 (старшие разряды) и во втором регистре 7 (младшие разряды) будет сформирован ожидаемый код адреса первого байта следующей команды. Этот код поступает на вход схемы 2 сравнения. В момент извлечения первого байта следующей команды микропроцессор 15 сформирует ее адрес на шине адреса и сигналы М1 и MEMR на шине управления. Если микропроцессор 15 работал без сбоев, то вьщанный адрес совпадает с ожидаемым адресом, поступающим из счетчика 1 и второго регистра 7. В этом случае на инвертирующем выходе схемы 2 сравнения будет установлен нулевой потенциал, что обеспечивает пассивный логический уровень ка выходе первого элемента И 3, Если же имел место сбо то адреса .будут неравны, на выходе схемы 2 сравнения появится сигнал 1. Совпадение этого сигнала с активным cHrHaj:JOM с инверсного выхода первого триггера 12 и сигналом с выхода третьего элемента И 10 вызовет срабатывание первого элемента И 3, установку второго триггера 13 и появление на. выходе устройства 16 активного сигнала, свидетельствующего о неправильной работе микропроцессора. Причем интервал времени между моментом, возникновения сбоя и моментом появления сигнала на выходе устрой- ства 16 не превьшает длительности одной команды. Если же очередная команда - команда перехода, то на до- полнительном выходе блока 5 постоянной памяти будет установлен единичный сигнал. В результате по заднему фронту сигнала с выхода третьего элемента И 10 благодаря элементу НЕ 14 первьш триггер 12 перейдет в единичное состояние. Сигнал с его инверсного выхода заблокирует контроль совпадения адресов при извлечении следзтощей команды с помощью первого элемента И 3. Кроме того произойдет переключение мультиплексора 8 и он подключит к второму входу сумматора 6 мпадшие разряды шины адреса контролируемого микро

0

5

0

5

процессора 15. Таким образом, при извлечении первого байта команды, следующей за командой перехода, контроль не проводится, а ее адрес плюс байтность команды (ожидаемый адрес следующей команды) фиксируется в счетчике 1 и втором регистре 7. Фиксация старших разрядов адреса в счетчике 1 производится сигналом с выхода четвертого элемента И 11, работа которого разрешается единичным сигналом с выхода триггера 12. Запись младших разрядов, представляющих собой сумму младших разрядов адреса очередной к оманды с ее байтностью- с выхода сумматора 6 во второй регистр 7, а также учет переноса с выхода сумматора 6 в счетчик 1 происходит аналогично первому случаю. Кроме того, по окончании считывания команды, следующей за командой перехода (если она,конечно, сама не является командой перехода), просходит возврат первого триггера 12 в состояние О н следовательно,; восстанавливается режим контроля. Таким образом, за исключением моментов перехода в устройстве постоянно контролируется ра- венство адреса, вьвдаваемого микропроцессором 15 и ожидаемого адреса. Это позволяет выявлять не только сбои счетчика команд микропроцессора 15, но и исправность шин адреса и данных, а также внутренних магистралей микропроцессора и его управлякнцего устройства.

Сигнал .с выхода устройства 16 может быть использован различным обра0 зом, например: для световой или звуковой сигнализации о неправильной работе микропроцессора, для прерьша- ния или сброса микропроцессора с целью восстановления вычислений после

5 сбоя, для подключения резервного микропроцессора в случае отказа контро лируемого.

Формула изобретения

0

5

50

Устройство для контроля микропроцессора, содержащее счетчик, схему сравнения и первый элемент И, первый вход которого соединен с выходом схе- gg мы сравнения, старшие разряды первой группы информационных входов которой соединены с группой выходов счетчика, отличающееся тем, что, с целью повьшения быстродействия

5

оно содержит первый и второй регистры, блок.постоянной памяти, сумматор мультиплексор, второй, третий и четвертый элементы И, элемент НЕ, первы и второй триггеры, причем информационный вход первого .регистра является входом устройства для подключения к шине данных контролируемого микропроцессора, выход первого регистра соединен с адресным входом блока постоянной памяти, выход поля.количества байтов в команде которого соедине с первым информационным входом сумматора, второй информационный вход которого соединен с выходом мультиплексора, группа выходов второго регистра соединена с младшими разрядами первой группы информационных входов схемы сравнения и с первой группой информационных входов мультиплексора, вторая группа информационных входов схемы сравнения образует вход устройства для подключения к шине адреса контролируемого микропроцессора, старшие и младшие разряды входа устройства для подключения к шине адреса контролируемого микропроцессора подключены соответственно к группе информационньпс входов счетчика и к второй группе информационных входов мультиплексора, выход переноса сумматора соединен с первым входом второго элемента И, выход которого соединен со счетным входом счет- чика, вход сброса которого, R-входы

0

15

35

первого и второго триггеров и вход сброса второго регистра подключены к входу устройства для подключения к выходу сброса контролируемого микропроцессора, входы устройства для подключения к вьпсоду признака первого байта команды и к выходу чтения памяти контролируемого микропроцессора подключены соответственно к первому и второму входам третьего элемента И, выход которого соединен с входом синхронизации первого регистра, с входом элемента НЕ, с вторым входом первого элемента И и с первым входом четвертого элемента И, выход элемента НЕ соедине.н с входами синхронизации первого триггера и второго регистра и с вторым входом второго элемента И, D-вход первого триггера соединен с выходом поля признака типа команды блока постоянной памяти, информахдзнонный выход сумматора соединен с информационным входом вто- 25 рого регистра, инверсный выход перво - го триггера соединен с третьим входом первого элемента И, выход которого соединен с S-входом второго триггера, выход которого является выходом неисправности устройства, прямой выход первого триггера соединен с управляющим входом мультиплексора и с вторьш входом четвертого элемента И, выход котор-ого соединен с вхо дом записи счетчика.

0

30

Ot0101

010101

010101

110113

110113

110113

110113

orOt01

Of0101

0101Ot 131301

021301

Ы1301

011301

01 01 01 01 01 01 01 01 01 01 01 01

01 01 01 01 01 01

11 11 11 13 00 13

01 01 01

11 11 11 11

00

11

13 02 13 13 01 13

11 11 01 13 01 13

01 01

11

0101

0101

t302

0002 li

0002 11

0002 11

| Авторское свидетельство СССР 788851, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля блока управления роботом | 1982 |

|

SU1119018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1988-12-15—Публикация

1987-03-09—Подача