Изобретение относится к вычислительной технике и может быть использовано для обмена данными между территориально удаленными модулями по последовательному каналу ввода-вывода.

Цель изобретения - повышение достоверности передачи информации между территориально удаленными микропроцессорными модулями.

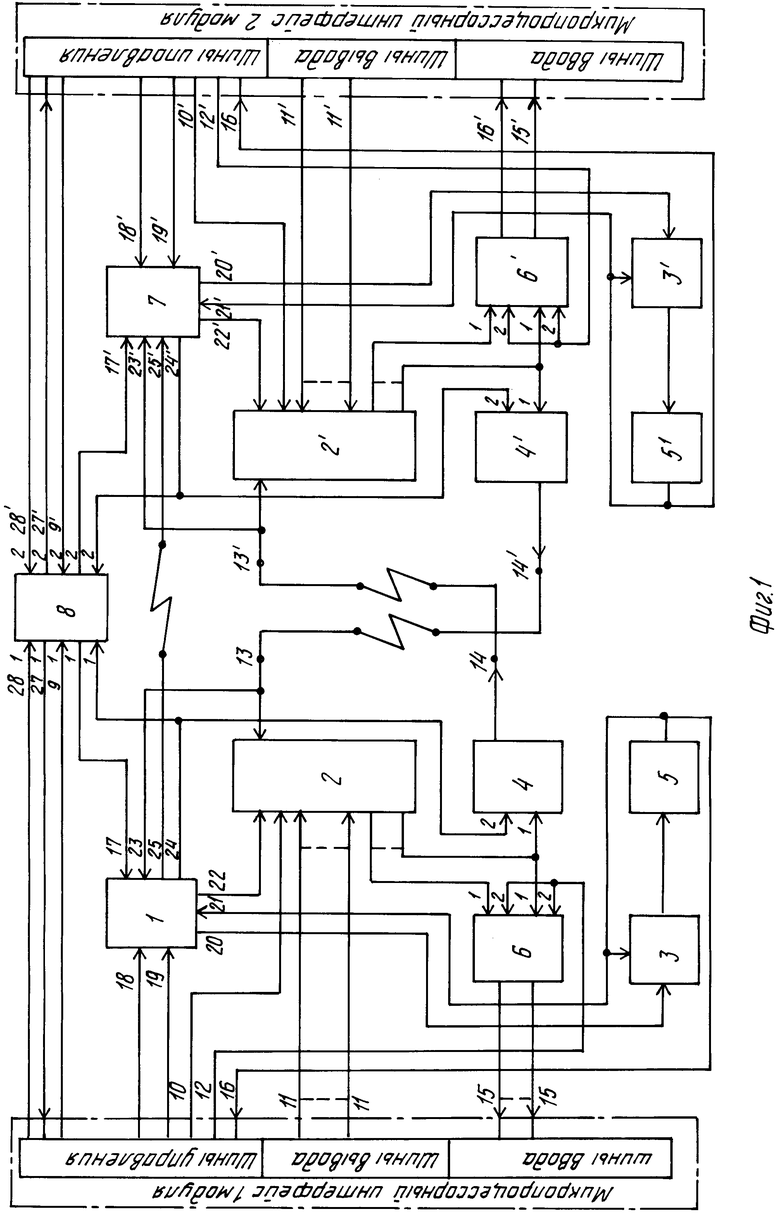

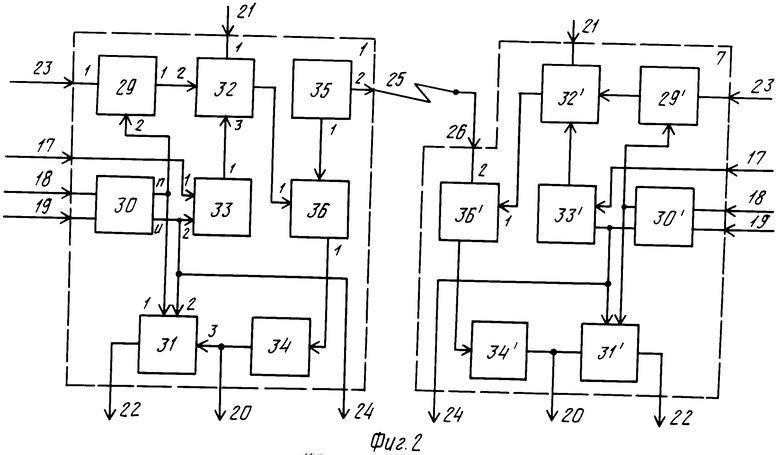

На фиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема первого и второго блоков управления и связь между ними; на фиг.3 - функциональная схема блока синхронизации приема-передачи.

Устройство содержит первый блок 1 управления, регистры 2 и 2', счетчики 3 и 3', элементы И 4 и 4', одновибраторы 5 и 5', группы 6 и 6' элементов И, второй блок 7 управления, блок 8 синхронизации приемопередачи данных, первый и второй входы 9, 9' запуска блока 8 синхронизации, первый и второй входы 10, 10' записи регистра 2, первый и второй входы 11, 11' параллельных данных устройства, первый и второй входы 12, 12' чтения устройства 14, 14' последовательных данных элементов И 4, 4', первый и второй выходы 15, 15' параллельных данных устройства, первый и второй выходы 16, 16' готовности устройства, первый и второй входы 17, 17' запуска блоков 1, 7, первый и второй входы 18, 18' выбора режима блоков 1, 7 управления, первый и второй входы 19, 19' ввода блоков 1, 7 управления, тактовые выходы 20, 22, 20', 22' блоков 1, 7 управления, входы 23, 23' синхронизации блоков 1, 7 управления, входы 21, 21' сброса блоков 1, 7 управления, выходы 24, 24' разрешения считывания блоков 1,7, выход 25 синхросигнала блока 1, вход 26 синхросигнала блока 7, первый и второй выходы 27, 27' запроса вывода блока 8, первый и второй входы 28, 28' разрешения ввода блока 8.

Первый блок 1 управления содержит элемент И 29, первый триггер 30, тактовый формирователь 31, второй триггер 32, элемент И 33, делитель 34 частоты, генератор 35 и элемент И 36 (см. фиг.2).

Второй блок 7 управления содержит элемент И 29, триггер 30, тактовый формирователь 31, триггер 32, элемент И 33, делитель 34 частоты и элемент И 36 (см. фиг.2).

Блок 8 синхронизации приемопередачи данных (фиг.3) содержит триггер 37, элемент И 38, элемент НЕ 39, элемент НЕ 40, триггер 41, элемент И 42.

Рассмотрим работу устройства.

Устройство функционирует в двух основных режимах: в режиме А - вывод информации с микропроцессорного интерфейса первого модуля, ввод информации на микропроцессорный интерфейс второго модуля; в режиме Б - вывод информации с микропроцессорного интерфейса второго модуля, ввод информации на микропроцессорный интерфейс первого модуля.

В режиме А устройство работает следующим образом.

На шине управления микропроцессорного интерфейса первого модуля вырабатывается сигнал "Выбор режима", который подается на вход 18 и, при отсутствии сигнала на входе 19, переводит блок 1 управления в режим работы "Вывод". При этом на выходе 24 блока 1 формируется разрешающий сигнал, который определяет, что последовательная информация будет выдаваться из первого регистра 2, через первый элемент И 4 по выходу 14, соединенному через линию связи с входом 13, на второй регистр 2.

Одновременно разрешающий сигнал с выхода 24 блока 1 поступает на первый вход запроса вывода блока 8 синхронизации приемопередачи, который по второму выходу 27 вырабатывает сигнал запроса вывода на шине управления микропроцессорного интерфейса второго модуля. Второй модуль, воспpиняв сигнал запроса вывода, вырабатывает на шинах управления интерфейса сигналы "Выбор режима" и "Ввод", которые подаются на входы соответственно 18 и 19 второго блока 7 управления и переводят его в режим работы "Ввод", при этом на выходе 24 блока 7 управления формируется запрещающий сигнал, определяющий, что последовательная информация будет вводиться с регистра 2.

Далее второй модуль вырабатывает на шине управления сигнал разрешения ввода, который подается на второй вход 28 разрешения ввода блока синхронизации приемопередачи.

Информация, выводимая с первого модуля, выставляется на шинах вывода интерфейса и выдачей сигнала "Запись" с шин управления интерфейса на вход 12 регистра 2 заносится в регистр 2 с входов 11.

Далее первый модуль по шине управления интерфейса выдает сигнал "Запуск" на первый вход 9 блока 8 синхронизации приемопередачи, который при наличии сигнала разрешения ввода на втором входе 28 разрешает его прохождение на вход "Запуск" 17 блока 1 управления.

Блок 1 начинает вырабатывать тактовые импульсы на выходе 22 для синхронизации сдвига и вывода последовательной информации с регистра 2 и на выходе 20 для подсчета количества выведенных битов последовательной информации 8 счетчика 3.

При появлении первого бита последовательной информации на входе 13 регистра 2 и входе 23 блока 7 управления последний также начинает вырабатывать текстовые импульсы на выходе 22 синхронизации сдвига и ввода последовательной информации в регистр 2 и на выходе 20 для подсчета количества введенных битов последовательной информации в счетчике 3.

После подсчета определенного количества тактовых импульсов счетчик 3 вырабатывает сигнал окончания подсчета, который, пройдя через одновибратор 5, сбрасывает счетчик 3 в исходное состояние, запрещает блоку 1 управления выработку текстовых импульсов и вырабатывает сигнал, поступающий по выходу 116 на шину управления интерфейса первого модуля, извещающего модуль об окончании вывода информации в регистр 2.

После подсчета определенного количества введенных битов последовательной информации счетчик 3 также формирует сигнал окончания счета, который, пройдя через одновибратор 5, запрещает блоку 7 дальнейшую выработку тактовых сигналов и сбрасывает счетчик 3 в исходное состояние. Одновременно сигнал с выхода одновибратора 5 вырабатывает сигнал, поступающий по выходу 16 на шину управления интерфейса второго модуля, извещая модуль об окончании ввода информации с регистра 2. При этом в регистре 2 находится информация для второго модуля, преобразованная из последовательного кода в параллельный.

Прием информации на шины ввода интерфейса второго модуля происходит по сигналу "Чтение", поступающего с шин управления интерфейса на вход 12 регистра 2. При этом информация из регистра 2 через вторую группу элементов И 6 передается на шины ввода по вторым выходам 15 устройства.

В режиме Б устройство работает аналогичным образом.

На шине управления микропроцессорного интерфейса второго модуля вырабатывается сигнал "Выбор режима", подаваемый на вход 18, и при отсутствии сигнала на входе 19 переводит блок 7 управления в режим "Вывод". При этом на выходе 24 блока 7 формируется разрешающий сигнал, определяющий, что последовательная информация будет выводиться из второго регистра 2 через второй элемент И 4 по выходу 14, соединенному через линию связи с входом 13, на первый регистр 2.

Одновременно разрешающий сигнал поступает на второй вход запроса вывода блока, который по первому выходу 27 вырабатывает сигнал запроса вывода на шине управления микропроцессорного интерфейса первого модуля. Первый модуль вырабатывает на шинах управления интерфейса сигналы "Выбор режима" и "Ввод", которые подаются на входы 18 и 19 соответственно первого блока 1 управления и переводят его в режим работы "Ввод", при этом на выходе 24 блока 1 формируется запрещающий сигнал, определяющий, что последовательная информация будет вводиться с регистра 2.

Далее первый модуль вырабатывает на шине управления сигнал разрешения ввода, который подается на первый вход 28 разрешения ввода блока 8.

Информация, выводимая с второго модуля, выставляется на шинах вывода интерфейса и выдачей сигнала "Запись" с шин управления на вход 12 регистра 2 заносится в регистр 2 с входов 11.

Далее второй модуль по шине управления выдает сигнал "Запуск" на второй вход 9 блока 8, который при наличии сигнала разрешения ввода на первом входе 28, разрешает его прохождение на вход "Запуск" 17 блока 7 управления.

Блок 7 начинает работать аналогично работе блока 1 в режиме А. При появлении первого бита последовательной информации на входе 13 регистра 2 и входе 23 блока 1 управления последний начинает работать аналогично работе блока 7 в режиме А.

После подсчета определенного количества тактовых импульсов счетчик 3 вырабатывает сигнал окончания подсчета, который, пройдя через одновибратор 5, сбрасывает счетчик 3, разрешает блоку 7 выработку тактовых импульсов и вырабатывает сигнал, поступающий по выходу 16 на шину управления интерфейса второго модуля, извещая модуль об окончании вывода информации в регистр 2.

После подсчета определенного количества введенных битов последовательной информации счетчик 3 также формирует сигнал окончания счета, который, пройдя через одновибратор 5, запрещает блоку 1 выработку тактовых сигналов и сбрасывает счетчик 3. Одновременно сигнал с выхода блока 5 выдает сигнал по выходу 16 на шину управления интерфейса первого модуля, извещая его об окончании ввода информации с регистра 2. При этом в регистре 2 находится информация для первого модуля.

Прием информации на шины ввода интерфейса первого модуля происходит по сигналу "Чтение", поступающему с шин управления на вход 12 регистра 2. При этом информация из регистра 2 через первую группу элементов И 6 передается на шины ввода по первым выходам 15 устройства.

Блок 8 синхронизации приемопередачи данных работает следующим образом.

В режиме А сигнал с выхода 24 блока 1 управления подается через линию связи на второй вход триггера 41, который по первому выходу формирует сигнал запроса вывода, поступающий по второму выходу 27 блока на выход устройства. Сигнал с выхода 24 блока 7 управления подается через линию связи, на второй вход триггера 37 и удерживает его в исходном состоянии. Сигнал разрешения ввода по второму входу 28 блока подается на первый вход триггера 41, сбрасывает его в исходное состояние и по второму выходу через элемент НЕ 40 высшим уровнем подается через линию связи на второй вход элемента И 38. При совпадении уровней сигнала "Запуск", поступающего по первому входу блока 8 на первый вход элемента И 38, и сигнала по второму входу элемента И 38, разрешается прохождение сигнала "Запуск" на входе 17 блока 1 управления. Этим достигается синхронизация приема первого бита на входе 13 регистра 2 и передачи первого бита с выхода 14 первого элемента И 4 и дальнейшая синхронизация приемопередачи всех остальных битов.

В режиме Б блок 8 работает аналогичным образом. Сигнал с выхода 24 блока 7 подается через линию связи на второй вход триггера 37, который по первому выходу формирует сигнал запроса вывода, поступающий по первому выходу 27 блока на выход устройства. Сигнал с выхода 24 блока 1 подается через линию связи на второй вход триггера 41 и удерживает его в исходном состоянии. Сигнал разрешения ввода по первому входу 28 блока подается на первый вход триггера 37, сбрасывает его и по второму выходу через элемент НЕ 39 высоким уровнем подается через линию связи на второй вход элемента И 42. При совпадении уровней сигнала "Запуск", поступающего по второму входу блока 8 на первый вход элемента И 42, и сигнала по второму входу элемента И 42 разрешается его прохождение на вход 17 блока 7.

Этим достигается синхронизация приема первого бита на входе 13 регистра 2 и передачи первого бита с выхода 14 второго элемента И 4 и дальнейшая синхронизация приемопередачи всех остальных битов.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРО-ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2000 |

|

RU2209462C2 |

| Устройство сопряжения двух ЭВМ | 1985 |

|

SU1334153A1 |

| Микропроцессорное устройство для управления вентильным преобразователем | 1985 |

|

SU1356155A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

Изобретение относится к вычислительной технике и может быть использовано для обмена данными между территориально удаленными модулями по последовательному каналу ввода-вывода. Цель изобретения - повышение достоверности передачи информации между территориально удаленными микропроцессорными модулями. Устройство позволяет осуществлять обмен данными между территориально удаленными микропроцессорными модулями с повышенной достоверностью за счет синхронизации приемопередачи битов последовательной информации по линии связи. 3 ил.

УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ МЕЖДУ МИКРОПРОЦЕССОРНЫМИ МОДУЛЯМИ, содержащее первый блок управления, первый регистр, первый счетчик, первую групу элементов И, первый элемент И и первый одновибратор, выход которого соединен с входами сброса первого счетчика и первого блока управления и является первым выходом готовности устройства, входы выбора режима и ввода блока управления являются первыми одноименными входами устройства, а первый и второй выходы поля управления блока управления соединены с синхровходом первого счетчика и первого регистра соответственно, первый выход поля управления первого блока управления соединен с первым входом первого элемента И, причем входы параллельной информации первого регистра являются первыми входами информации устройства, вход записи - первым входом загрузки устройства, а выходы соединены с первыми входами элементов И первой группы, выходы которых являются выходами устройства, вторые входы элементов И первой группы являются адресными входами устройствами, выход старшего разряда первого регистра соединен с вторым входом первого элемента И, отличающееся тем, что в устройство введены блок синхронизации приема-передачи данных и дополнительно второй блок управления, второй регистр, второй счетчик, вторая группа элементов И, второй элемент И и второй одновибратор, выход которого соединен с входами сброса второго счетчика и второго блока управления и является вторым выходом готовности устройства, вход синхронизации второго блока управления и вход данных второго регистра подключены через линию связи к выходу первого элемента И, входы выбора режима и ввода второго блока управления являются вторыми одноименными входами устройства, первый и второй выходы поля управления второго блока управления соединены с синхровходом второго счетчика и второго регистра соответственно, третий выход поля управления второго блока управления - с выходом второго элемента И и первым входом режима работы блока синхронизации приема-передачи данных, вторые входы информации второго регистра являются вторыми входами информации устройства, а вход записи второго регистра - вторым входом загрузки устройства, выходы второго регистра соединены с первыми входами элементов И второй группы, выходы которых являются вторыми выходами информации устройства, вторые входы элементов И второй группы являются входами считывания устройства, выход второго регистра соединен с вторым входом второго элемента И, выход которого является выходом последовательных данных и подключен через линию связи к входу последовательных данных первого регистра, выход второго счетчика соединен с входом второго одновибратора, второй и третий входы режима работы блока синхронизации приема-передачи являются входами устройства для подключения соответственно к входам разрешения ввода и запуска первого и второго модулей, первые выходы блока синхронизации приема-передачи соединены соответственно с входами запуска первого и втрого блоков управления, вторые выходы являются выходами устройства для подключения соответственно к входам запроса первого и второго модулей, второй выход поля управления первого блока управления соединен через линию связи с синхровходом второго блока управления, а третий выход - с четвертым входом режима работы блока синхронизации приема-передачи данных.

| Устройство для ввода-вывода информации | 1986 |

|

SU1368884A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-09-30—Публикация

1991-03-07—Подача