Изобретение относится к радиотехнике и может быть использовано в радиолокации, измерительной технике, для формирования сигналов с заданным законом изменения фазы.

Целью изобретения является упрощение устройства.

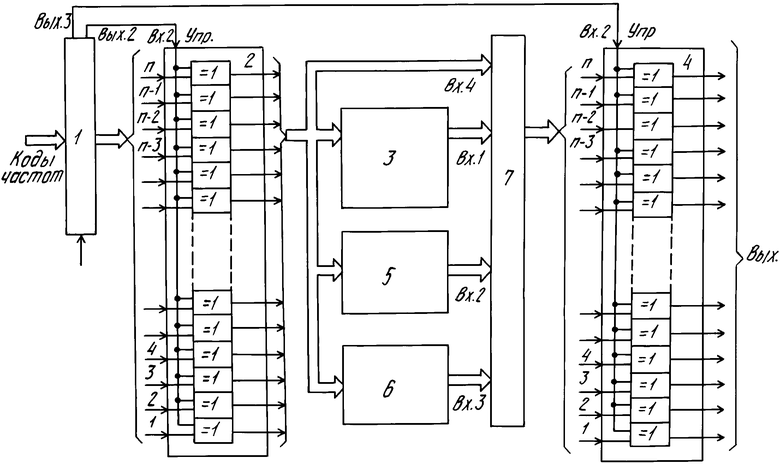

На чертеже представлена структурная электрическая схема цифрового синтезатора частот.

Цифровой синтезатор частот содержит (n+2)-разрядный накопитель фазы 1, первый блок элементов Исключающее ИЛИ (n-разрядная схема равнозначности) 2, первый преобразователь кодов 3, второй блок элементов Исключающее ИЛИ (вторая n-разрядная схема равнозначности) 4, второй и третий преобразователи кодов 5, 6 и сумматор 7.

Работа устройства заключается в следующем.

На вход (n+2)-разрядного накопителя фазы 1 подается код частоты. С каждым тактом тактовой последовательности этот код в (n+2)-разрядном накопителе фазы 1 суммируется с предыдущим значением и на его выходе (выход суммы) получается ряд последовательностей с весом суммы, т.е. коды, пропорциональные текущей фазе. Этот сигнал подается на первую n-разрядную схему равнозначности 2, вторые входы которой подключены к разряду (n+2)-разрядного накопителя фазы 1, определяющему квадрант (первый после старшего). За счет этого на выходе n-разрядной схемы равнозначности 1 появляется свернутая тактовая последовательность, т.е. при монотонном нарастании входных кодов от нуля до π/2 она линейно возрастает, а при дальнейшем нарастании их от π/2 до π она линейно уменьшается. Затем этот процесс повторяется. Таким образом на выходе n-разрядной схемы равнозначности 2 появляются коды адресов для преобразователей кодов 3, 5, 6, которые определяют четвертую часть синусоиды.

Для упрощения исполнения преобразователя кодов используется тригонометрическое соотношение

sin(x+y+z) = sin x ˙ cos y ˙ cos z + +cos x ˙ sin y ˙ cos z + cos x ˙ cos y x x sin z - sin x ˙ sin y ˙ sin z, где x, y, z - углы, в сумме составляющие текущий угол фазы. При выборе условия x >> y >> z некоторыми членами соотношения можно пренебречь без ухудшения точности

sin(x + y + z) = sinx + cos x ˙ sin y +

+ cos x ˙ sin z.

Если использовать линейную функцию фазы, которая вырабатывается на выходе n-разрядной схемы равнозначности 2 для синтезирования квадранта, найдем виды функции, которые необходимо реализовать преобразователями

sin(x+y+z) =  x-

x-  x+sinx+cosx·siny+cosx·sinz

x+sinx+cosx·siny+cosx·sinz

Таким образом, получено четыре слагаемых, которые необходимо просуммировать. Это линейная функция ( π /2) ˙ х, которая уже реализована и присутствует на выходе n-разрядной схемы равнозначности 2, второй член этого соотношения _  x+sinx, это выражение определяет грубое изменение большими шагами синусоидальной функции за вычетом линейной функции. Третье слагаемое cos x ˙ sin y определяет средний шаг изменения синусоидальной функции, и последний член cos x˙ sin z точно корректирует текущее изменение угла в небольших пределах. Эти функции производят преобразователи кодов 3, 5 и 6 соответственно. Затем сигналы в виде двоичных кодов суммируются в сумматоре 7 и подаются на второй блок элементов Исключающее ИЛИ (вторую n-разрядную схему равнозначности) 4, вторые ее входы объединены и на них подается сигнал с выхода старшего разряда (n+2)-разрядного накопителя фазы 1 (знаковый разряд). За счет этого сигнал на выходе преобразователя кодов в течение половины периода проходит без инверсии, в течение другой половины периода - с инверсией. Это равнозначно изменению знака синусоидальной функции. Итак, на выходе получается ряд двоичных последовательностей, двоичный код которых со своим весом определяет значение синусоиды в текущий момент времени. В результате большой преобразователь кодов с n разрядами в предлагаемом устройстве заменяется на три преобразователя кодов с количеством разрядов не более (n/3) + K, где К = 1...3 в зависимости от точности преобразования. Таким образом происходит упрощение устройства при сохранении точности преобразования.

x+sinx, это выражение определяет грубое изменение большими шагами синусоидальной функции за вычетом линейной функции. Третье слагаемое cos x ˙ sin y определяет средний шаг изменения синусоидальной функции, и последний член cos x˙ sin z точно корректирует текущее изменение угла в небольших пределах. Эти функции производят преобразователи кодов 3, 5 и 6 соответственно. Затем сигналы в виде двоичных кодов суммируются в сумматоре 7 и подаются на второй блок элементов Исключающее ИЛИ (вторую n-разрядную схему равнозначности) 4, вторые ее входы объединены и на них подается сигнал с выхода старшего разряда (n+2)-разрядного накопителя фазы 1 (знаковый разряд). За счет этого сигнал на выходе преобразователя кодов в течение половины периода проходит без инверсии, в течение другой половины периода - с инверсией. Это равнозначно изменению знака синусоидальной функции. Итак, на выходе получается ряд двоичных последовательностей, двоичный код которых со своим весом определяет значение синусоиды в текущий момент времени. В результате большой преобразователь кодов с n разрядами в предлагаемом устройстве заменяется на три преобразователя кодов с количеством разрядов не более (n/3) + K, где К = 1...3 в зависимости от точности преобразования. Таким образом происходит упрощение устройства при сохранении точности преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1983 |

|

SU1190457A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Цифровой синтезатор частот | 1990 |

|

SU1774464A1 |

| СПОСОБЫ И УСТРОЙСТВА ПОВЫШЕНИЯ ИНДЕКСА УГЛОВОЙ МОДУЛЯЦИИ | 2012 |

|

RU2493646C2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОДИРОВАННЫХ РАДИОСИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1991 |

|

RU2017195C1 |

| ЦИФРОВОЙ ПЕРИОДОМЕР | 1991 |

|

RU2011997C1 |

| Устройство для вычисления функций синуса и косинуса | 1991 |

|

SU1827673A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| Цифровой фазовый детектор | 1986 |

|

SU1467785A1 |

| Устройство для вычисления функций @ и @ | 1980 |

|

SU978146A1 |

Использование: радиотехника, радиолокация, измерительная техника. Сущность изобретения: цифровой синтезатор частот содержит (n + 2)-разрядный накопитель фазы 1, первый и второй блоки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2, 4, преобразователи кодов 3, 5, 6 и сумматор кодов 7. Это позволяет упростить устройство. 1 ил.

ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ, содержащий (n + 2)-разрядный накопитель фазы, сумматор кодов, первый и второй преобразователи кодов, при этом кодовый выход первого преобразователя кодов соединен с первым кодовым входом сумматора кодов, а тактовый и n-разрядный кодовый входы (n + 2)-разрядного накопителя фазы являются соответственно входом сигнала опорной частоты и входом кода частоты цифрового синтезатора частот, отличающийся тем, что, с целью упрощения, в него введены первый и второй блоки элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и третий преобразователь кодов, при этом кодовые входы первого, второго и третьего преобразователей кодов и второй кодовый вход сумматора кодов объединены и подключены к n-разрядному кодовому выходу первого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, управляющий вход которого подсоединен к выходу сигнала (n + 1)-го разряда (n + 2)-разрядного накопителя фазы, выход сигнала (n + 2-го старшего разряда которого соединен с управляющим входом второго блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, n-разрядный кодовый вход которого соединен с кодовым выходом сумматора кодов, третий и четвертый кодовые входы сумматора кодов соединены с кодовыми выходами соответственно второго и третьего преобразователей кодов, выход каждого из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первого и второго блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ является выходом одного из разрядов n-разрядного кодового выхода соответствующего блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход каждого из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первого и второго блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ является входом одного из разрядов n-разрядного кодового входа соответствующего блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ объединены и являются управляющим входом первого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второго блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ объединены и являются управляющим входом второго блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а n-разрядный выход (n + 2)-разрядного накопителя фазы соединен с n-разрядным кодовым входом первого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

| Цифровой синтезатор частот | 1978 |

|

SU813675A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-09-30—Публикация

1991-02-27—Подача