Изобретение относится к автоматике, в частности к системе управления терминальной сетью персональных ЭВМ, и может быть использовано при организации распределения заданий в локальной сети.

Известно одно из технических решений, при котором устройство содержит центральный процессор, входы которого соединены с регистрами состояний, а выход подключен к логическому блоку, другие входы которого соединены с блоками памяти, синхронизации и управления (1).

Недостаток этого устройства состоит в его конструктивной сложности.

Известно и другое техническое решение, при котором устройство содержит дешифратор адреса, входы которого являются входами устройства, а выходы соединены со счетным и информационным входами счетчика и с одними входами первого элемента ИЛИ, выход которого подключен к входу первого элемента задержки, выход которого соединен с входом считывания блока памяти, адресный вход которого подключен к выходу счетчика, а выход соединен с одними входами элементов И первой группы, первый триггер, единичный выход которого подключен к одним входам элементов ИЛИ первой группы, а нулевой выход соединен с одними входами элементов ИЛИ второй группы, второй триггер, прямой выход которого подключен к одному входу элементов И, другой вход которого соединен с выходом второго элемента задержки, а выходы подключены к прямым входам триггеров группы, выходы которых соединены с другими входами элементов ИЛИ первой и второй групп, выходы которых подключены к соответствующим элементам И группы (2).

Последнее из перечисленных выше технических решений наиболее близко к описываемому устройству.

Его недостаток состоит в ограниченных функциональных возможностях, обусловленных тем, что передача заданий операторам на интеллектуальные рабочие места осуществляется независимо от того, может принять это задание соответствующий терминал или нет, так как он занят в это время выполнением другого срочного задания.

Если оператор задания принять не может, так как интеллектуальный терминал занят решением задачи, то это задание может быть просто потеряно, что снижает надежность устройства в целом.

Целью изобретения является повышение достоверности выходной информации за счет исключения потерь распределяемых заданий.

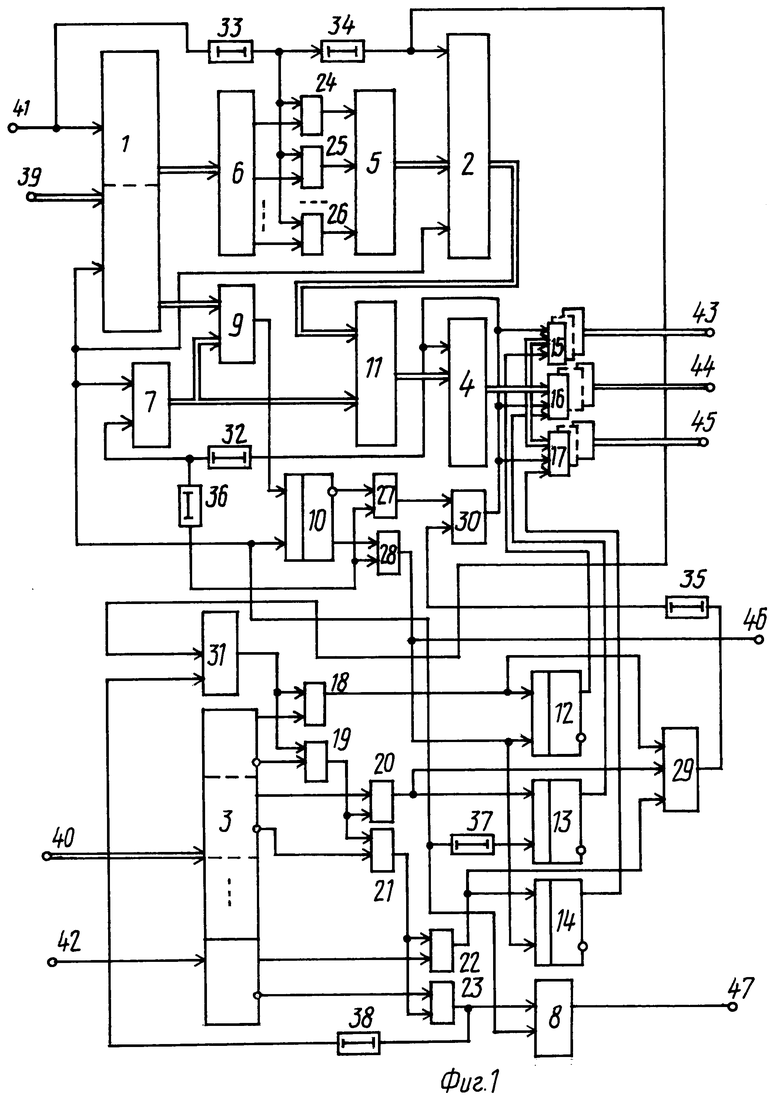

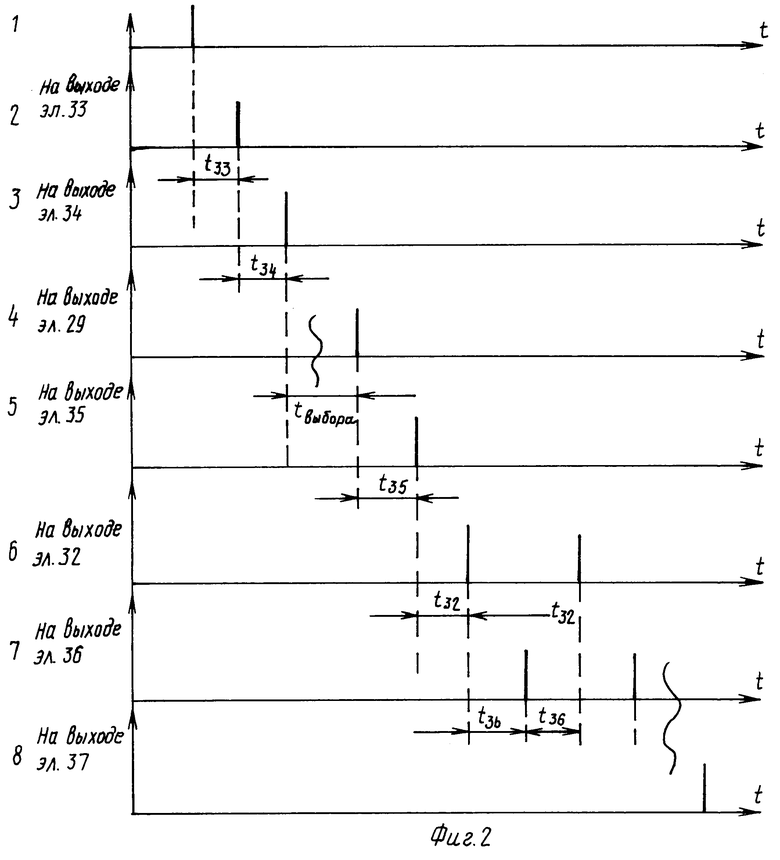

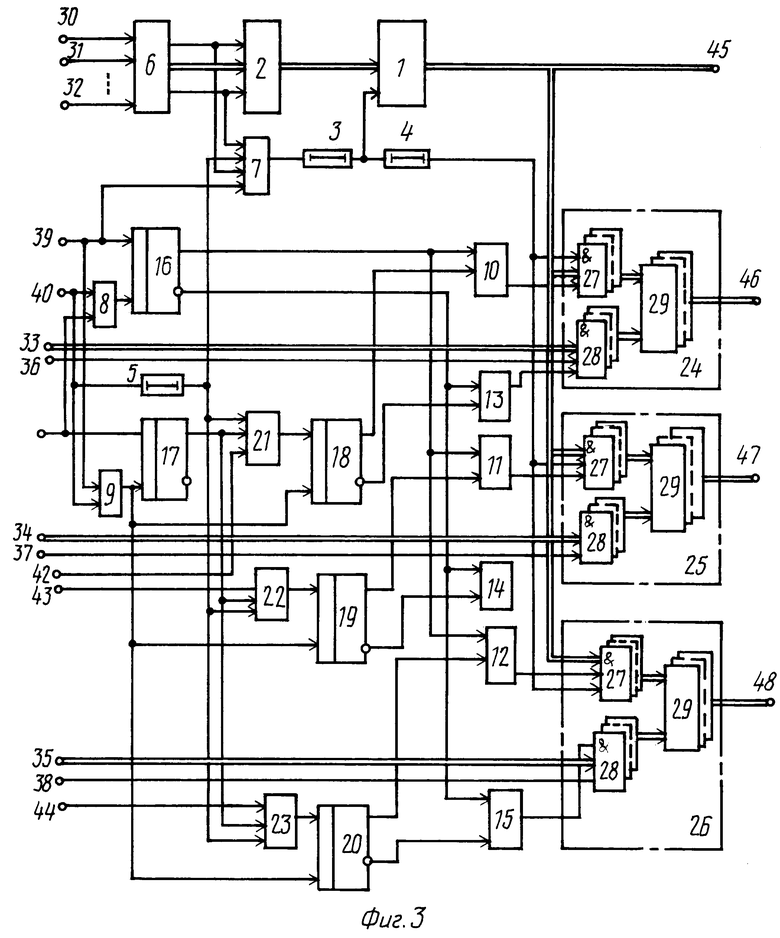

На фиг. 1 представлена структурная схема заявленного объекта; на фиг. 2 - временная диаграмма, поясняющая работу устройства.

Устройство (фиг. 1) содержит первый 1, второй 2 и третий 3 регистры, первый блок памяти 4, выполненный в виде ОЗУ, второй блок 5 памяти, выполненный в виде ПЗУ, дешифратор 6, первый 7 и второй 8 счетчики, компаратор 9, триггер 10, сумматор 11 комбинационного типа, группу триггеров 12-14, первую 15-17, вторую 18, 19, третью 20, 21, четвертую 22, 23 и пятую 24-26 группы элементов И, первый 27 и второй 28 элементы И, первый 29, второй 30, третий 31 элементы ИЛИ, первый 32, второй 33, третий 34, четвертый 35, пятый 36, шестой 37, седьмой 38 элементы задержки.

На чертеже (фиг. 1) показаны входы 39-42 и выходы 43-47.

Устройство включает регистр 1, соединенный с дешифратором 6 и компаратором 9, регистр 2, входы которого подключены к выходу блока 5 памяти и элементу задержки 32, а выход соединен с одним входом сумматора 11, другой вход которого подключен к выходу счетчика 7, а выход соединен с адресным входом блока 4 памяти, выходы которого соединены с элементами 15-17 И, подключенными к выходам элемента 30 ИЛИ и соответствующих триггеров 12-14, входы компаратора 9 соединены с выходами регистра 1 и счетчика 7, а выход подключен к входу триггера 10, прямой и инверсный выходы которого соединены с входами элементов 27, 28 И, регистр 3, выходы которого подключены к входам элементов 18-23 И, выходы которых соединены с входами триггеров 12-14, нулевые входы которых подключены к выходу элемента 28 И, второй счетчик 8, соединенный с выходом элемента 23 И и с выходом элемента 37 задержки, входы элемента 29 ИЛИ соединены с выходами элементов 18, 20, 22 И, а выход подключен к элементу 35 задержки, соединенному с элементом 30 ИЛИ, выход которого подключен к входу считывания блока 4 памяти, вход элемента 34 задержки соединен с выходом элемента 33 задержки, а выход подключен к одному входу элемента 31 ИЛИ, другой вход которого соединен с выходом элемента задержки 38, подключенного к выходу элемента 23 И, при этом выход элемента 31 ИЛИ соединен с входами элементов 18, 19 И, входы элементов 20, 21 И подключены к выходу элемента 19 И, а входы элементов 22, 23 И соединены с выходом элемента 21 И.

Устройство работает следующим образом.

Интеллектуальные терминалы (автоматизированные рабочие места - АРМ), выполненные на базе персональных ЭВМ ЕС-1841, подключаются информационными входами соответственно к выходам 43-46 устройства.

Информация о состоянии, в котором находятся АРМы (заняты, неисправны или готовы к выполнению расчетов), поступает в соответствующие разряды регистра 3 с входа 40.

При готовности к работе соответствующего АРМа в соответствующем разряде регистра 3 будет "1", в противном случае - "0".

Данным устройством задание на выполнение соответствующего расчета с входа 39 заносится в регистр 1 синхроимпульсом с входа 41 (фиг. 2, 3 поз. 1).

Задание на выполнение расчета имеет следующий вид:

Номер задания  Код имени файла

Код имени файла

Код задания расшифровывается дешифратором 6, который открывает один из элементов 24-26 И, например элемент 24 И, на другой вход которого поступает синхроимпульс с входа 41, задержанный элементом 33 на время переходных процессов в регистре 1 и дешифраторе 6 (фиг. 2, 3 поз. 2).

Синхроимпульс проходит через элемент 24 И и поступает на вход считывания фиксированной ячейки памяти блока 5, где записан базовый адрес области памяти, в которой хранятся исходные данные для выполнения задания.

Код базового адреса считывается из блока 4 на вход регистра 2, куда и заносится синхроимпульсом с выхода элемента задержки 34, задерживающего синхроимпульс на время считывания кода из блока 5 (фиг. 2, 3 поз. 3).

С выхода регистра 2 код базового адреса поступает на вход комбинационного сумматора 11, на другой вход которого подается содержимое счетчика 7. Учитывая, что к началу работы устройства счетчик 7, как и другие узлы, сброшен в исходное состояние, то на выходе сумматора 11 и соответственно на адресном входе блока 4 памяти устанавливается код базового адреса первой ячейки памяти, начиная с которой записан файл данных в следующем виде:

Тип задачи  Исходные данные

Исходные данные

После установки базового адреса на входе блока 4 синхроимпульс с выхода элемента 34 задержки, проходящий через элемент 31 ИЛИ, используется для организации процесса выбора АРМа, готового принять на себя выполнение задания.

С этой целью указанный импульс с выхода элемента 31 ИЛИ поступает на входы элементов 18, 19 И, другие входы которых подключены к прямому и инверсному выходам первого разряда регистра 3, фиксирующего готовность первого АРМа к выполнению задания.

Если указанный АРМ готов к принятию задания на выполнение, то первый разряд регистра 3 будет находиться в единичном состоянии, при котором элемент 18 И будет открыт, а элемент 19 И закрыт. Тогда импульс с выхода элемента 31 И пройдет через элемент 18 И и, во-первых, поступит на прямой вход триггера 12, устанавливая его в единичное состояние, который высоким потенциалом с прямого выхода открывает элемент 15 И, подключая тем самым выход блока 4 памяти к выходу 43 и далее к информационному входу первого АРМа; во-вторых, этот же синхроимпульс проходит через элемент 29 ИЛИ на вход элемента задержки 35 (фиг. 2, 3 поз. 4), где задерживается на время подключения АРМа к выходу 43, а затем через элемент 30 ИЛИ тот же импульс поступает на вход считывания блока 4 памяти и на входы элементов 15 И, считывая и выдавая содержимое ячейки памяти на выход 43 (фиг. 2, 3 поз. 5). В-третьих, тот же импульс с выхода элемента 30 ИЛИ поступает на вход элемента задержки 32, где задерживается на время считывания данных и далее поступает как на счетный вход счетчика 7, устанавливая в нем единицу, так и на вход элемента задержки 36, время задержки которого равно сумме времен срабатывания счетчика 7, компаратора 9 и триггера 10, и далее поступает на входы элементов 27, 28 И (фиг. 2, поз. 6, 7).

Учитывая, что триггер 10 к этому моменту времени находится в нулевом состоянии, то высоким потенциалом с его инверсного выхода будет открыт элемент 27 И. В связи с этим импульс с выхода элемента 36 задержки проходит через элемент 27 И, элемент 30 ИЛИ и далее вновь поступает на вход считывания блока 4 памяти, выдавая на выход блока 4 содержимое очередной ячейки памяти.

Процесс увеличения адреса считывания счетчиком 7 продолжается до тех пор, пока компаратор 9 не зафиксирует равенство кода числа исходных данных, хранящихся в регистре 1, с числом, зафиксированным счетчиком 7. В момент равенства кодов в регистре 1 и счетчике 7, компаратор вырабатывает импульс, переводящий триггер 10 в единичное состояние, при котором элемент 27 И закрывается, а элемент 28 И открывается.

В этом случае импульс с выхода элемента 36 задержки, задержанный на время срабатывания счетчика 7, компаратора 9 и триггера 10, проходит через элемент 28 И на выход 46 в качестве сигнала окончания выдачи исходных данных и запуске задачи на решение.

Кроме того, этот же импульс возвращает триггер 12 в исходное состояние, отключая АРМ от выхода 43, а также после задержки элементом 37 на время сброса триггеров 12-14 в исходное состояние, поступает на установочные входы триггера 10, регистров 1, 2 и счетчиков 7, 8 (фиг. 2, 3 поз. 8).

Если же в процессе проверки состояния АРМов первый из них будет не готов к приему задания, то элемент 18 И будет закрыт, а элемент 19 И открыт. Тогда импульс выхода элемента 31 ИЛИ пройдет через элемент 19 И и поступит на опрос состояния элементов 20, 21 И, фиксирующих готовность второго автоматизированного рабочего места к приему задания.

При готовности второго АРМа будет открыт элемент 20 И, и импульс с его выхода установит другой триггер 13 в единичное состояние и поступит на вход элемента 29 ИЛИ, запуская устройство на процесс выдачи исходных данных, описанным выше образом на выход 44 и далее на информационный вход второго АРМа.

Если же и второй АРМ не готов принять задание, то импульс с выхода элемента 19 И проходит через элемент 21 И на входы элементов 22, 23 И и т. д.

Может оказаться, что к данному моменту времени все АРМы оказались занятыми и не готовыми к приему задания, тогда импульс с выхода элемента 23 И поступает как на счетный вход счетчика 8, фиксирующего тот факт, что запрос на выполнение задания не принят ни одним АРМом, так и вход элемента задержки 38, время задержки которого определяется принятым временем ожидания задания в очереди на обработку, с выхода которого импульс вновь через элемент 31 ИЛИ на опрос состояний АРМов, фиксируемых элементами 18-23 И.

Счетчик 8 предназначен для проверки общего времени ожидания запроса в очереди на обработку, превышающего установленные значения, например, равного восьми циклам ожидания.

Если за 8 циклов задание не принято ни одним из АРМов, то тогда очередной девятый импульс, поступивший на счетный вход счетчика 8, появится на выходе переполнения этого счетчика и выходе 47 устройства, свидетельствуя о том, что в терминальной сети возникла ситуация, требующая вмешательства диспетчера сети.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора данных о состоянии массы, перемещаемой технологическими линиями | 1989 |

|

SU1810897A1 |

| Устройство для распознавания образов | 1991 |

|

SU1798806A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РОБОТОМ - МАНИПУЛЯТОРОМ | 1989 |

|

RU2044619C1 |

| Устройство для идентификации кодограмм-сообщений | 1990 |

|

SU1805481A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для идентификации признаков объектов | 1989 |

|

SU1626258A1 |

| СИСТЕМА ДИСТАНЦИОННОГО ОБУЧЕНИЯ СТУДЕНТОВ | 2006 |

|

RU2315364C1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| СИСТЕМА ИДЕНТИФИКАЦИИ ГОТОВНОСТИ ТЕКСТОВЫХ ДОКУМЕНТОВ В СЕТИ РАСПРЕДЕЛЕННОЙ ОБРАБОТКИ ДАННЫХ | 2005 |

|

RU2284053C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

Изобретение относится к автоматике, в частности к системе управления терминальной сетью персональных ЭВМ, и может быть использовано при организации распределения заданий в локальной сети. Целью изобретения является повышение достоверности выходной информации за счет исключения потерь распределяемых заданий. Поставленная цель достигается тем, что устройство содержит два блока памяти, четыре регистра, дешифратор, (Т + 3) групп элементов И, два счетчика, сумматор, схемы сравнения, три элемента ИЛИ, семь элементов задержки. 3 ил.

УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ В ТЕРМИНАЛЬНОЙ СЕТИ, содержащее первый блок памяти, три элемента задержки, дешифратор, первый счетчик, T + 2 групп элементов И, где T - количество терминалов, триггер, два элемента И, первый элемент ИЛИ, группу триггеров, причем вход первого элемента задержки подключен к входу записи-чтения первого блока памяти, выход K-го разряда первого блока памяти подключен к первому входу K-го элемента И P-й группы, (K = 1, M, где M - разрядность задания, P = 1, T,) выход P-го триггера группы подключен к второму входу K-го элемента И P-й группы, выход которого подключен к K-му разряду P-го информационного выхода устройства, вход приема задания устройства через второй элемент задержки подключен к входу третьего элемента задержки, отличающееся тем, что, с целью повышения достоверности выходной информации за счет исключения потерь распределяемых заданий, в него введены три регистра, группа элементов И, второй блок памяти, схема сравнения, сумматор, с четвертого по седьмой элементы задержки, второй и третий элементы ИЛИ, второй счетчик, причем выход второго элемента задержки подключен к первым входам элементов И (T + 1)-й группы, вторые входы и выходы которых подключены к соответствующим выходам дешифратора и к разрядам адресного входа второго блока памяти соответственно, вход кодов распределяемых заданий устройства подключен к информационному входу первого регистра, синхровход которого подключен к входу приема задания устройства, первый и второй выходы первого регистра подключены соответственно к входу дешифратора и первому информационному входу схемы сравнения, прямой и инверсный выходы триггера подключены соответственно к первым входам первого и второго элементов И, выход первого элемента И подключен к выходу индикации окончания выдачи задания устройства, входам установки в "0" триггеров группы и через четвертый элемент задержки - к входам установки в "0" первого и второго счетчиков, первого и второго регистров и триггера, выход второго элемента И подключен к первому входу первого элемента ИЛИ, выход которого подключен к третьим входам элементов И P-й группы и входу первого элемента задержки, выход которого подключен к счетному входу первого счетчика и через пятый элемент задержки - к вторым входам первого и второго элементов И, выход второго элемента ИЛИ через шестой элемент задержки подключен к второму входу первого элемента ИЛИ, входы состояния приемников и синхронизации приема заданий устройства подключены соответственно к информационному входу и синхровходу третьего регистра, прямой и инверсный выходы P-го разряда которого подключены соответственно к первым входам P-х элементов И (T + 2)-й и (T + 3)-й групп, выход P-го элемента И (T + 2)-й группы подключен к входу установки в "1" P-го триггера группы и к P-му входу второго элемента ИЛИ, выход второго блока памяти подключен к информационному входу второго регистра, выход которого подключен к первому информационному входу сумматора, выход которого подключен к адресному входу первого блока памяти, выход первого счетчика подключен к вторым информационным входам схемы сравнения и сумматора, выход третьего элемента задержки подключен к синхровходу второго регистра и первому входу третьего элемента ИЛИ, выход которого подключен к вторым входам первых элементов И (T + 2)-й и (T + 3)-й групп, выход H-го элемента И (T + 3)-й группы подключен к вторым входам (H + 1)-х элементов И (T + 2)-й и (T + 3)-й групп, (H + 1), T-го элемента И (T + 3)-й группы подключен к синхровходу второго счетчика и через седьмой элемент задержки - к второму входу третьего элемента ИЛИ, выход второго счетчика подключен к выходу индикации ошибки распределения заданий устройства, выход схемы сравнения подключен к входу установки в "1" триггера.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР N 1485296, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1994-11-15—Публикация

1989-12-04—Подача