Предлагаемый микропроцессор (МП) имеет специальную архитектуру и предназначен для выполнения команд языка высокого уровня, одна команда за один такт.

Используется в вычислительной технике - для решения задач управления в реальном времени (встраиваемое оборудование, станки с числовым программным управлением, робототехника, бортовая аппаратура, электронные АТС).

Цель изобретения - повышение производительности.

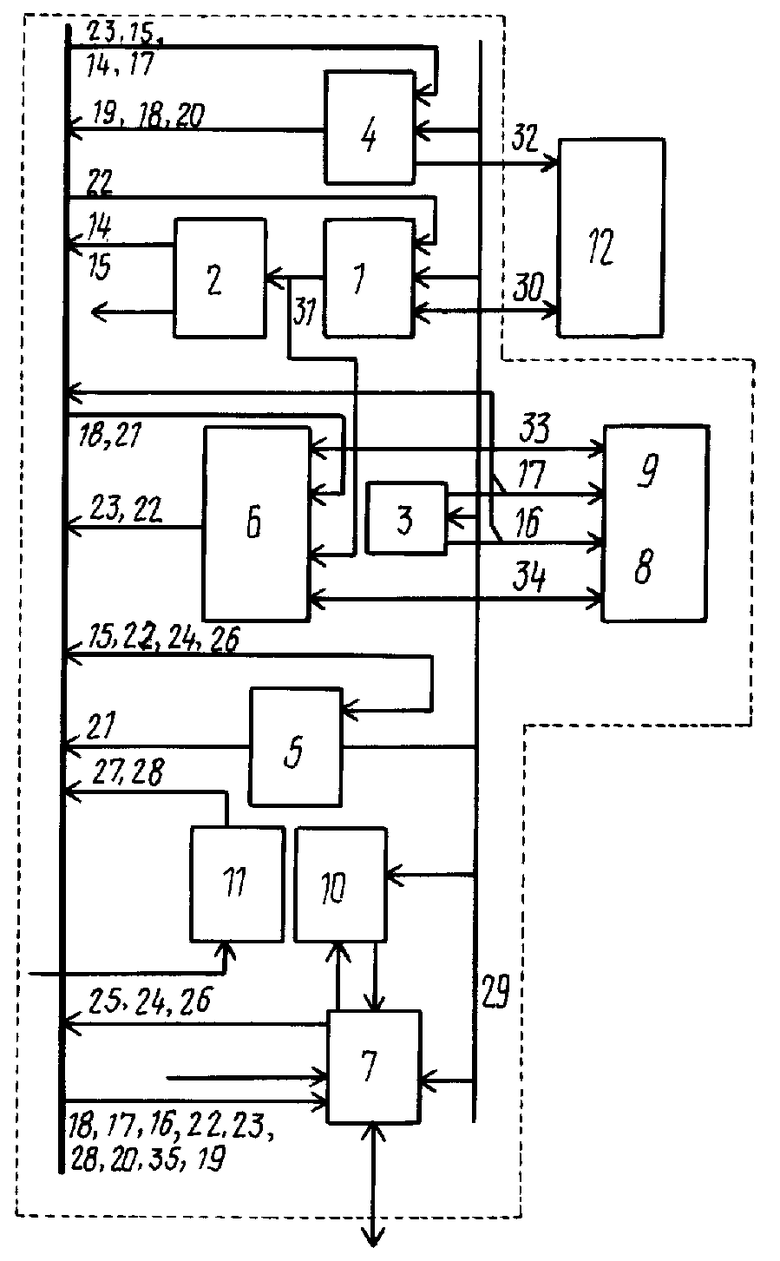

На чертеже приведена структурная схема предлагаемого микропроцессора.

Микропроцессор содержит первый блок 1 ввода-вывода, блок 2 формирования команд, блок 3 указателя адреса, блок 4 указателя адреса, арифметико-логический блок 5, второй блок 6 ввода-вывода, третий блок 7 ввода-вывода, блок 8 памяти стека параметров, блоки 9 памяти стека возвратов, таймер 10 и контроллер 11 прерываний.

Далее в состав микропроцессора входит магистраль 13, объединяющая информационные шины (далее шины):

- 14 литерала, 15 короткого литерала, 16 адреса памяти стека параметров и 17 памяти стека возвратов, 18 счетчика команд, 19 пользовательского сегментного регистра, 20 регистров сегментов данных и программ, 21 результата вычислений, 22 второго элемента стека параметров, 23 первого элемента стека возвратов, 24 внутренних источников, 25 поддержки деления/умножения и 26 квадратного корня, 27 вектора, 28 регистра маски, информационная шина 29 верхнего элемента стека параметров, вход-выход 30, выход 31, выход 32, входы-выходы 33, 34, 35, выход 36.

Блок 4 формирует и по шине передает адрес к блоку 12. После формирования адреса и передачи его к блоку 12 команды или данные поступают в блок 1 по входу-выходу 30. Команды по шине поступают в регистр, содержащийся в блоке 2. Команды дешифрируются блоком 2 и подаются к блокам микропроцессора для управления информационным потоком. Микропроцессор принимает внешний сигнал синхронизации и формирует внутренний сигнал синхронизации (ССК) для кодирования и фиксации. Команда фиксируется в блоке 2 положительным фронтом CLK и декодируется во время верхнего состояния CLK. Декодирование завершается до перехода к нижнему состоянию. До прихода следующего положительного фронта CLK происходит определение ячейки памяти в блоке 12 (содержащей следующую команду или информационное слово) и выполнение микропроцессором текущей команды. Другими словами, происходит совмещение двух основных действий микропроцессора, формирование (следующего) адреса и выполнение уже принятой команды.

Далее информация по шине подается на вход блока 6 и может быть помещена в регистр, являющийся вторым элементом стека параметров, первым (верхним) элементом является регистр в блоке 5.

В свою очередь, блок 6 соединен шиной с блоком 5 и другой шиной с блоком. Связь регистра, входящего в блок 6 с блоком 9, осуществляется соответствующей шиной. Информация, извлекаемая из блока 8 и блока 9 по адресам, формируется блоком 3.

Через блок 6 может осуществляться обмен содержимым блоков 9 и 8. Информация, содержащаяся в блоках 8, 9, через блок 6 подается в одном случае по шине на входы блока 5 и блока 1, в другом случае - по шине на вход блока 4 и используется им для формирования адресов возврата при вызове подпрограмм.

Блок 5 преобразовывает информацию и передает ее по шине на входы блоков 4, 3, 1, 6 и 7. Блок 7 используется для расширения возможностей ввода-вывода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство управления шаговым двигателем | 1990 |

|

SU1789970A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| АКТИВНЫЙ АППАРАТНЫЙ СТЕК ПРОЦЕССОРА | 2013 |

|

RU2530285C1 |

| Устройство для ввода-вывода информации | 1985 |

|

SU1297068A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1991 |

|

RU2077415C1 |

| Устройство контроля и управления технологическим комплексом для намотки изделий | 1989 |

|

SU1661721A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

Изобретение относится к вычислительной технике, в частности к микропроцессорам, поддерживающим языки высокого уровня. Микропроцессор /МП/ имеет специальную архитектуру и предназначен для выполнения команд языка высокого уровня, одна команда за один такт, МП может использоваться для решения задач обработки сигналов и изображений, располагает ресурсами для решения задач управления в реальном времени. Цель изобретения повышение производительности за счет поддержки потокового обращения внешних устройств к блоку основной памяти. МП содержит: три блока ввода-вывода, блок формирования команд, два блока указателя адреса, арифметико-логический блок, блок памяти стека параметров, блок памяти стека возвратов, таймер и контроллер прерываний. 1 ил.

МИКРОПРОЦЕССОР, содержащий первый, второй и третий блоки ввода-вывода, блок формирования команд, первый и второй блоки указателя, арифметико-логический блок, блок памяти стека параметров, блок памяти стека возвратов, таймер и контроллер прерываний, причем управляющие входы первого, второго и третьего блоков ввода-вывода, первого и второго блоков указателя адреса, арифметико-логического блока, блока памяти стека параметров, блока памяти стека возвратов, таймера и контроллера прерываний соединены с соответствующими выходами первой группы блока формирования команд, тактовый вход и вход пуска которого подключены соответственно к одноименным входам микропроцессора, первый информационный вход-выход которого подключен к первым информационным входам первого и третьего блоков ввода-вывода таймера, второго блока указателя адреса, информационному входу второго блока указателя адреса и информационному входу-выходу арифметико-логического блока, информационный выход которого соединен с первым информационным входом первой группы второго блока ввода-вывода, вторая группа информационных входов которого соединена с группой информационных входов блока формирования команд и группой информационных выходов первого блока ввода-вывода, второй информационный вход которого соединен с первым информационным выходом второго блока ввода-вывода, первый и второй информационные входы-выходы которого соединены с информационными входами-выходами соответственно блока памяти стека параметров и блока памяти стека возвратов, адресные входы которых соединены соответственно с первым и вторым выходами первого блока указателя адреса, информационный вход-выход первого блока ввода-вывода является вторым информационным входом-выходом микропроцессора, адресный выход которого подключен к первому выходу второго блока указателя адреса, второй выход которого соединен с вторым информационным входом первой группы второго блока ввода-вывода, второй информационный выход которого соединен с первым информационным входом группы второго блока указателя адреса, второй информационный вход группы которого соединен с выходом вектора прерываний контроллера прерываний, вход прерываний которого является одноименным входом микропроцессора, первый, второй и третий информационные выходы группы третьего блока ввода-вывода и первый информационный выход второго блока ввода-вывода соединены с соответствующими информационными входами группы арифметико-логического блока, второй, третий и четвертый информационные выходы второго блока указателя адреса, первый и второй выходы первого блока указателя адреса, первый и второй информационные выходы второго блока ввода-вывода и выход прерываний контроллера прерываний соединены с соответствующими информационными входами первой группы третьего блока ввода-вывода, информационный вход-выход которого является третьим информационным входом-выходом микропроцессора, информационный выход третьего блока ввода-вывода соединен с вторым информационным входом таймера, отличающийся тем, что, с целью повышения производительности, группа выходов таймера соединена с второй группой информационных входов третьего блока ввода-вывода.

| Electronic engineering, 01.89, ном.745, р.56,58. |

Авторы

Даты

1994-12-15—Публикация

1990-10-29—Подача