Изобрете 1ие относится к вычислительной технике и может быть использовано для ввода-вывода информации в микрогроцессорных системах.

Целью изобретения является повышение быстродействия устройства при вводе-выводе информации, разрядность которой превышает длину машинного слова, за счет использования шины адреса для передачи информации и ввода-вывода двух машинных слов по шине данных за одну команду.

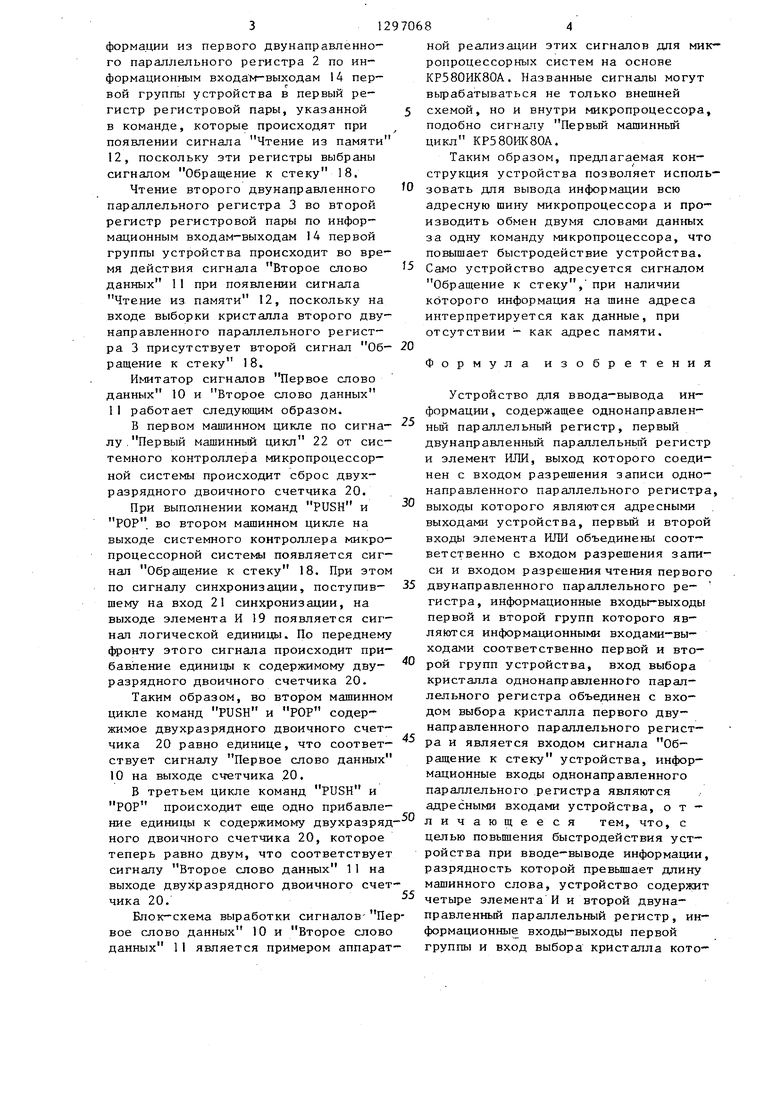

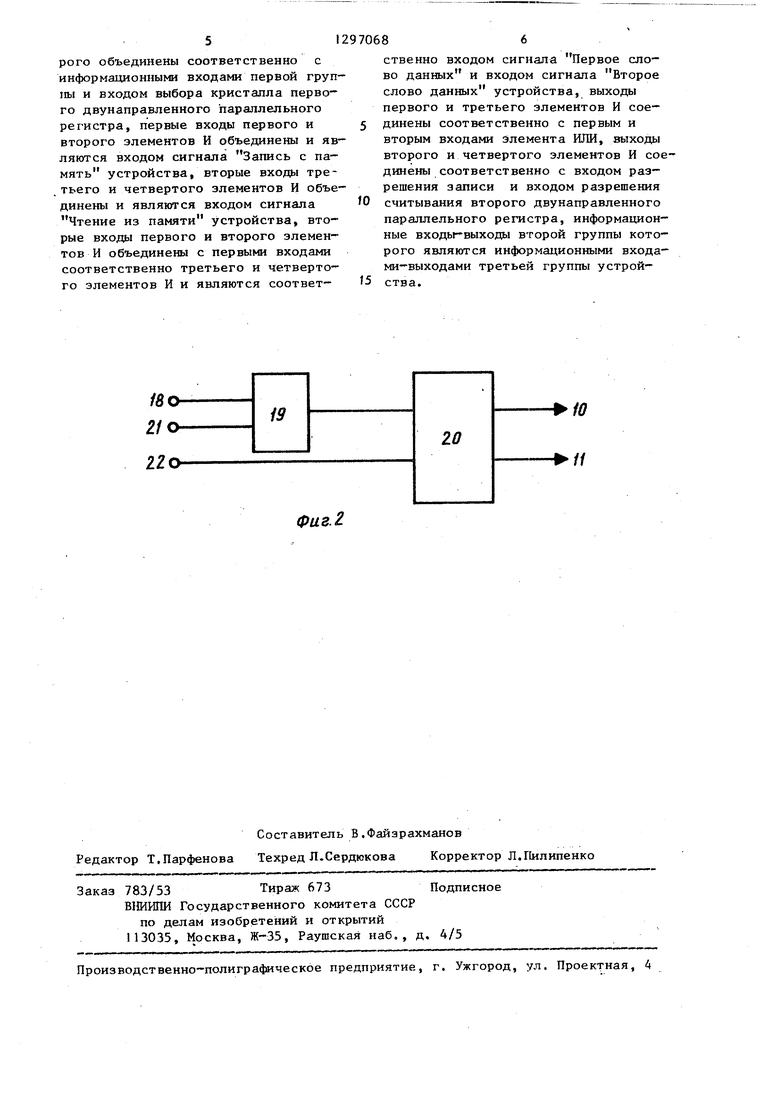

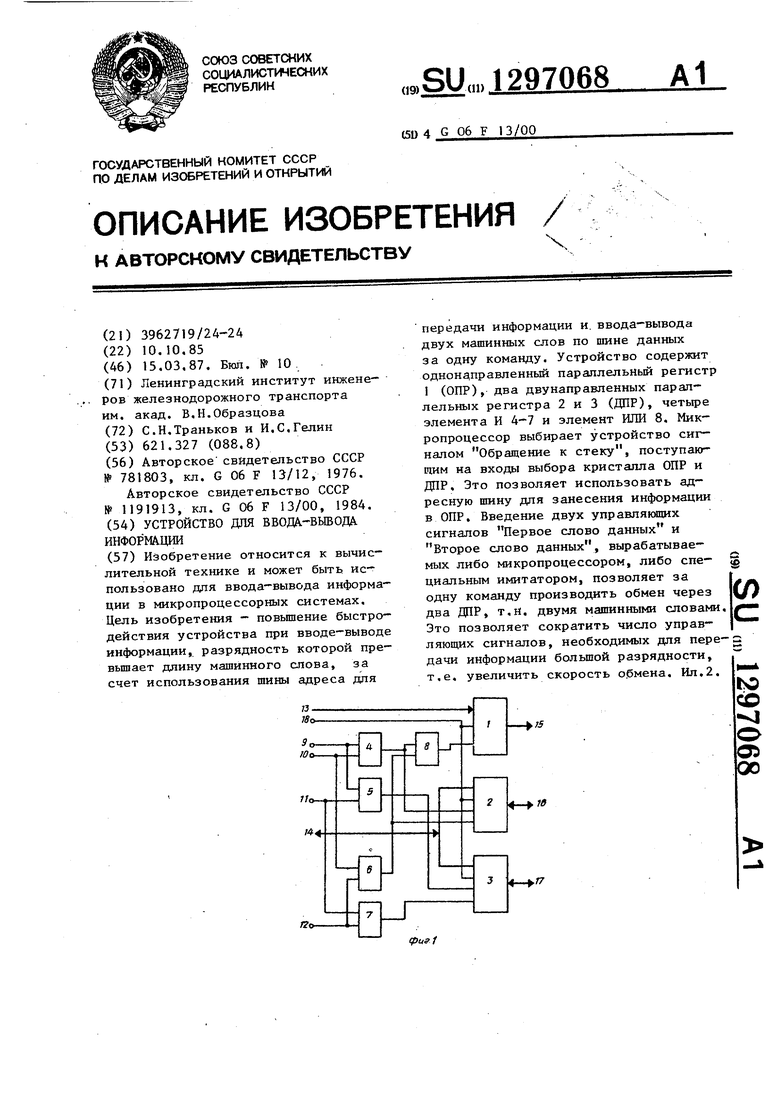

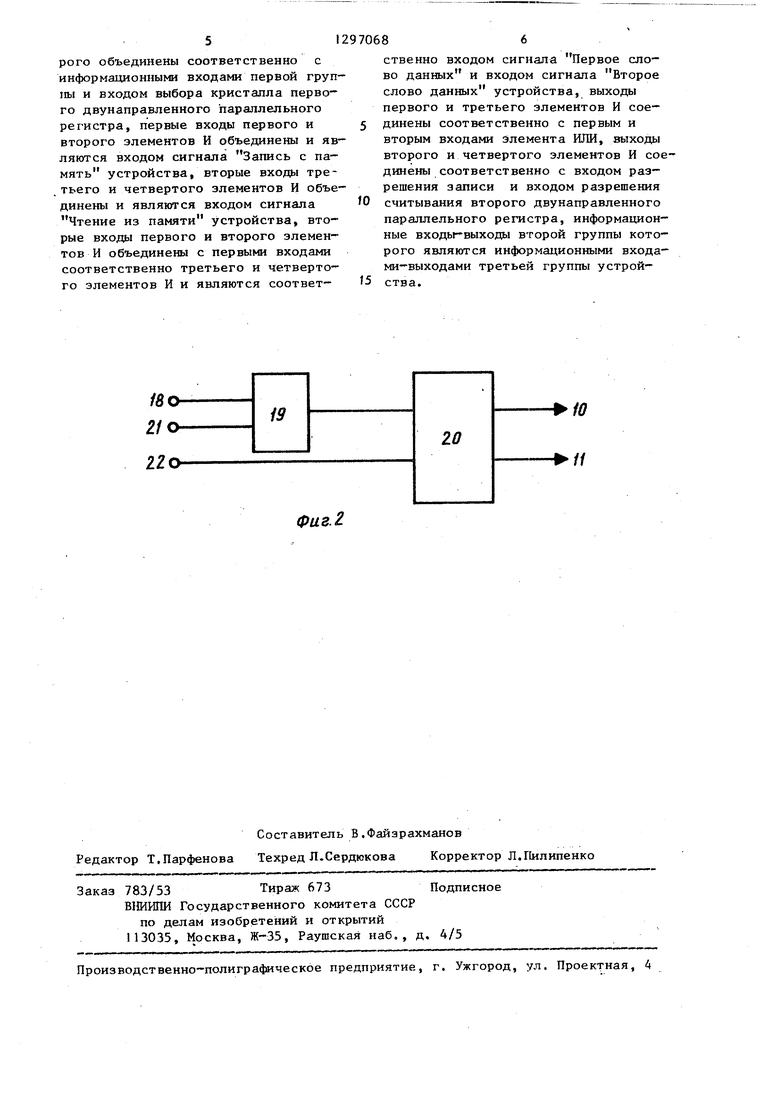

На фиг.1 представлена блок-схема устройства; на фиг.2 - блок-схема имитатора сигналов Первое слово данных и Второе слово данных для микропроцессора КР580 ИК80А.

На фиг.1 обозначены однонаправленный параллельный регистр 1, пер- вьй двунаправленный регистр 2, второй двунаправленный параллельный регистр 3, первый,.второй, третий и четвертый элементы И 4-7 соответственно, элемент ИЛИ 8, вход Запис в память 9, вход Первое слово данных гО, вход Второе слово данных 11, вход Чтение из памяти 12, адресные входы 13 устройства, информационные входы-выходы -14 первой группы устройс /ва, адресные выходы 15 устройства, информационные входы- выходы 16 второй группы устройства, информационные входы-выходы 17 третьей группы устройства.и вход Обращение к стеку 18.

На фиг.2 обозначены элемент И 19 двухразрядный двоичный счетчик 20, вход 21 синхроимпульсов микропроцессора, вход сигнала Первый машинный цикл 22.

Устройство работает следующим образом.

При выполнении командь микропроцессора Запись содержимого регистровой пары в стек (PUSH) происходит запись содержимого первого регистра регистровой пары в первый двунаправленный параллельный регист 2, второго регистра регистровой пары - во второй двунаправленньш па раллельньш регистр 3, и содержимого указателя стека - в однонаправленны параллельный регистр I.

При выполнении команды микропроцессора Чтение содержимого стека в регистровую пару (ГОР) происходи чтение первого двунаправленного параллельного регистра 2 в первый ре

5

0

5

0

5

0

5

0

5

гистр регистровой пары микропроцессора, чтение второго двунаправленного параллельно го регистра 3 - во второй регистр регистровой пары микропроцессора и, кроме того, происходит запись содержимого указателя стека в однонаправленный регистр 1.

Рассмотрим работу предлагаемого устройства для ввода-вывода информации при выполнении команды PUSH для микропроцессора КР580ИК80А.

Во втором машинном цикле этой команды на первую группу информационных входов-выходов 14 устройства выдается содержимое первого регистра регистровой пары, указанной в команде PUSH. В это же время на адресные входы первой группы устройства выдается содержимое указателя стека. При этом появляется сигнал Первое слово данных 10, подготавливаюидай запись в однонаправленный параллегльный регистр 1 и первый двунаправленный параллельный регистр 2, которая происходит при появлении сигнала Запись в память 9, поскольку эти регистры уже выбраны сигналом Обраш,ение к стеку 18. Сигнал Обращение к стеку вырабатывается в начале второго машинного цикла команды PUSH системным контроллером микропроцессорной системы.

В третьем машинном цикле этой команды на информационные входы-выходы 14 первой группы устройства выдается содержимое второго регистра регистровой пары, указанной в команде PUSH. При этом появляется сигнал Второе слово данных 11, необходимый для записи содержимого второго регистра регистровой пары микропроцессора во второй двунаправленный параллельный регистр 3, которая происходит при появлении сигнала Запись в память 9 и обеспечивается вторым сигналом Обращение к стеку 18, поступающим на вход выбора кристалла второго двунаправленного параллельного регистра 3.

Рассмотрим работу устройства для случая выполнения микропроцессором КР580Ж80А команды POP.

При появлении сигнала Первое слово данных 10 подготавливается запись содержимого указателя стека в однонаправленный парагшельньш регистр 1 по адресным входам 13 первой группы устройства и чтение ин-

312

формации из первого двунаправленного параллельного регистра 2 по информационным BXOflaNf-BbixoflaM 14 пер-

г

вой группы устройства в первый регистр регистровой пары, указанной в команде, которые происходят при появлении сигнала Чтение из памяти 12, поскольку эти регистры выбраны сигналом Обращение к стеку 18.

Чтение второго двунаправленного параллельного регистра 3 во второй регистр регистровой пары по информационным входам-выходам 14 первой группы устройства происходит во время действия сигнала Второе слово данных 11 при появлении сигнала Чтение из памяти 12, поскольку на входе выборки кристалла второго двунаправленного параллельного регистра 3 присутствует второй сигнал Об- ращение к стеку 18.

Имитатор сигналов Первое слово

данных 10 и Второе слово данных 11 работает следующим образом.

В первом машинном цикле по сигна- лу. Первый машинный цикл 22 от системного контроллера микропроцессорной системы происходит сброс двух- разрядного двоичного счетчика 20.

При выполнении команд PUSH и POP, во втором машинном цикле на выходе системного контроллера микропроцессорной систе№1 появляется сигнал Обращение к стеку 18. При этом по сигналу синхронизации, поступившему на вход 2 синхронизации, на выходе элемента И 19 появляется сигнал логической единицы. По переднему фронту этого сигнала происходит прибавление единицы к содержимому дву- разрядного двоичного счетчика 20.

Таким образом, во втором машинном цикле команд PUSH и POP содержимое двухразрядного двоичного счетчика 20 равно единице, что соответствует сигналу Первое слово данных 10 на выходе счетчика .20.

Б третьем цикле команд PUSH и POP происходит еще одно прибавление единицы к содержимому двухразрядного двоичного счетчика 20, которое теперь равно двум, что соответствует сигналу Второе слово данных 11 на выходе двухразрядного двоичного счетчика 20.

Блок-схема выработки сигналов- Певое слово данных 10 и Второе слово данных 11 является примером аппарат

ной реализации этих сигналов для микропроцессорных систем на основе КР580ИК80А. Названные сигналы могут вьфабатываться не только внешней схемой, но и внутри микропроцессора, подобно сигналу Первый машинный цикл КР580Ж80А.

Таким образом, предлагаемая конструкция устройства позволяет использовать для вывода информации всю адресную шину микропроцессора и производить обмен двумя словами данных за одну команду микропроцессора, что повышает быстродействие устройства. Само устройство адресуется сигналом Обращение к стеку, при наличии которого информация на шине адреса интерпретируется как данные, при отсутствии - как адрес памяти.

Формула изобретения

0

5

0

Устройство для ввода-вывода информации, содержащее однонаправленный параллельный регистр, первый двунаправленный параллельньш регистр и элемент ИЛИ, выход которого соединен с входом разрешения записи однонаправленного параллельного регистра, выходы которого являются адресными выходами устройства, первый и второй входы элемента ИЛИ объединены соответственно с входом разрешения записи и входом разрешения чтения первого двунаправленного параллельного ре- гистра, информационные входы-выходы первой и второй групп которого являются информационными входами-выходами соответственно первой и второй групп устройства, вход выбора кристалла однонаправленного параллельного регистра объединен с входом выбора кристалла первого двунаправленного параллельного регистра и является входом сигнала Обращение к стеку устройства, информационные входы однонаправленного параллельного регистра являются адресными входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства при вводе-выводе информации, разрядность которой превьш1ает длину машинного слова, устройство содержит четыре элемента И и второй двунаправленный параллельный регистр, информационные входы-выходы первой группы и вход выбора кристалла кото5

рого объединены соответственно с информационными входами первой труп- ны и входом выбора кристалла первого двунаправленного параллельного регистра, первые входы первого и второго элементов И объединены и являются входом сигнала Запись с память устройства, вторые входы третьего и четвертого элементов И объединены и являются входом сигнала Чтение из памяти устройства, вторые входы первого и второго элементов И объединены с первыми входами соответственно третьего и четвертого элементов И и являются соответФаг.2

ственно входом сигнала Первое слово данных и входом сигнала Второе слово данных устройства, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выходы второго и четвертого элементов И соединены соответственно с входом разрешения записи и входом разрешения считывания второго двунаправленного параллельного регистра, информационные входы-выходы второй группы которого являются информационными входами-выходами третьей группы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1983 |

|

SU1167615A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Реконфигурируемый вычислительный модуль | 2018 |

|

RU2686017C1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Многоканальное устройство управления шаговым двигателем | 1990 |

|

SU1789970A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЯЕМОЙ ПАМЯТИ | 2014 |

|

RU2550555C1 |

Изобретение относится к вычислительной технике и может быть использовано для ввода-вывода информации в микропроцессорных системах. Цель изобретения - повышение быстродействия устройства при вводе-выводе информации, разрядность которой превышает длину машинного слова, за счет использования шины адреса дпя 3 Юл передачи информации и. ввода-вывода двух машинных слов по шине данных за одну команду. Устройство содержит однонаправленный параллельный регистр 1 (ОПР), два двунаправленных параллельных регистра 2 и 3 (ДПР), четьфе элемента И 4-7 и элемент ИЛИ 8. Микропроцессор выбирает устройство си1- налом Обращение к стеку, поступающим на входы выбора кристалла ОПР и ДПР, Это позволяет использовать адресную шину дпя занесения информации в ОПР. Введение двух управлякяцих сигналов Первое слово данных и Второе слово данных, вырабатываемых либо микропроцессором, либо специальным имитатором, позволяет за одну команду производить обмен через два ДПР, т.н. двумя машинными словами. Это позволяет сократить число управляющих сигналов, необходимых для передачи информации большой разрядности, т.е. увеличить скорость о.бмена. Ил.2. - ./5 « (Л ts5 О О) 00 cpusi

| Устройство ввода-вывода | 1976 |

|

SU781803A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1191913A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-10—Подача