Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем для решения задач, алгоритмы которых имеют последовательно-параллельную структуру.

Известна вычислительная система, которая относится к классу множественный поток команд - множественный поток данных (МКМД) и позволяют совмещать во времени выполнение параллельных ветвей алгоритмов.

Вычислительная система состоит из общего запоминающего устройства, нескольких вычислительных блоков, каждый из которых содержит процессор, локальную память, локальную шину, регистр состояния, устройства ввода-вывода. Вычислительная система обрабатывает как независимые последовательные программы, так и программы, алгоритмы выполнения которых допускают распараллеливание, т. е. имеют последовательно-параллельную структуру.

Однако производительность системы снижается, когда параллельные ветви представляют собой последовательность небольшого числа операций, после выполнения которых необходимо осуществить обмен данными между процессорами, что характерно, например для алгооритмов полиномов, цепных дробей и других многоместных выражений.

. Известна вычислительная система содержащая несколько вычислительных блоков, блоки локальной памяти, блок управления, логический коммутатор, блок преобразования и хранения данных, устройства ввода-вывода данных.

Эта вычислительная система при вычислении многоместных операций работает следующим образом. Вначале производится подготовка задачи к решению. Выдаются признаки исправности и занятости процессорного блока, что позволяет в процессе вычислений использовать только исправные процессорные блоки.

Далее настраивается пара вход-выход в логическом коммутаторе. Для этого блок управления вырабатывает команды на формирование адреса выхода и адреса входа, по которому осуществляется ассоциативный поиск процессорного блока для выполнения заданной функции.

Недостатком системы является следующее. Настройка коммутатора на реализацию определенного алгоритма требует достаточно большого времени. Когда возникает необходимость часто менять алгоритмы вычислений, а также выполнять одновременно несколько алгоритмов (в различных сочетаниях), известная система обладает невысокой производительностью.

Целью изобретения является повышение производительности вычислительной системы.

Поставленная цель достигается тем, что вычислительная система, содержит блок управления, группу вычислительных блоков, группу устройств ввода данных, группу устройств вывода данных, блок памяти операндов, блок памяти управляющих слов, регистр адреса, регистр данных и коммутатор, группа информационных входов которого соединена с информационными выходами группы устройств ввода данных и группы вычислительных блоков. Группа управляющих входов коммутатора соединена с первой группой выходов блока управления, вторая группа выходов которого соединена с входами чтения устройств вывода данных, выходы признаков информации которых соединены с первой группой входов условий блока управления, вторая группа входов условий блока управления соединена с выходами признаков готовности к приему и наличия информации вычислительных блоков, входы записи и чтения которых соединены с третьей группой выходов блока управления, первый и второй выходы которого соединены с входами записи адреса и регистра данных соответственно, четвертая группа выходов блока управления соединена с входами записи группы устройств вывода данных, выходы готовности которых соединены с третьей группой входов условий блока управления. В систему дополнительно введены блок буферной памяти данных и блок буферной памяти команд, информационные выходы которого соединены с информационными входами устройств вывода данных и вычислительных блоков, выходы

0 типа команды блока буферной памяти команд соединены с четвертой группой условий блока управления, выходы коммутатора соединены с информационными входами блока буферной памяти данных, первая и

5 вторая информационные группы выходов которого соединены с информационными входами регистра адреса и регистра данных соответственно, а выходы Буфер пуст и Буфер заполнен блока буферной памяти

0 данных соединены с первым и вторым входами условий блока управления, третий и четвертый выходы которого соединены с входами записи и продвижения очереди блока буферной памяти данных соответственно. Выход признака типа информации регистра данных соединен с третьим входом условий блока управления, а информационные выходы регистра данных соединены с информационными входами

0 блоков памяти операндов и управляющих слов и первой группой информационных входов блока буферной памяти команд, вторая и третья группы информационных входов которого соединены с информационными выходами блоков памяти операндов и управляющих слов соответственно. Выход регистра адреса соединен с адресными входами блоков памяти операндов и управляющих слов, входы записи и чтения

0 каждого из которых соединены с выходами блока управления с пятого по восьмой, девятый выход которого соединен с входом признака данных блока памяти операндов, выходом признака данных блока памяти

5 операндов, выход признака данных которого соединен с четвертым входом условий блока управления, пятый и шестой входы условий которого соединены соответственно с выходами Буфер пуст и Буфер запол0 нен блока буферной памяти команд, входы записи и продвижения очереди которого соединены с десятым и одиннадцатым выходами блока управления.

Отличительные признаки в указанной

5 взаимосвязи ранее нигде не встречались, являются существенными, и в своей совокупности позволяют увеличить производительность системы за счет совмещения во времени реализации различных алгоритмов в любом сочетании.

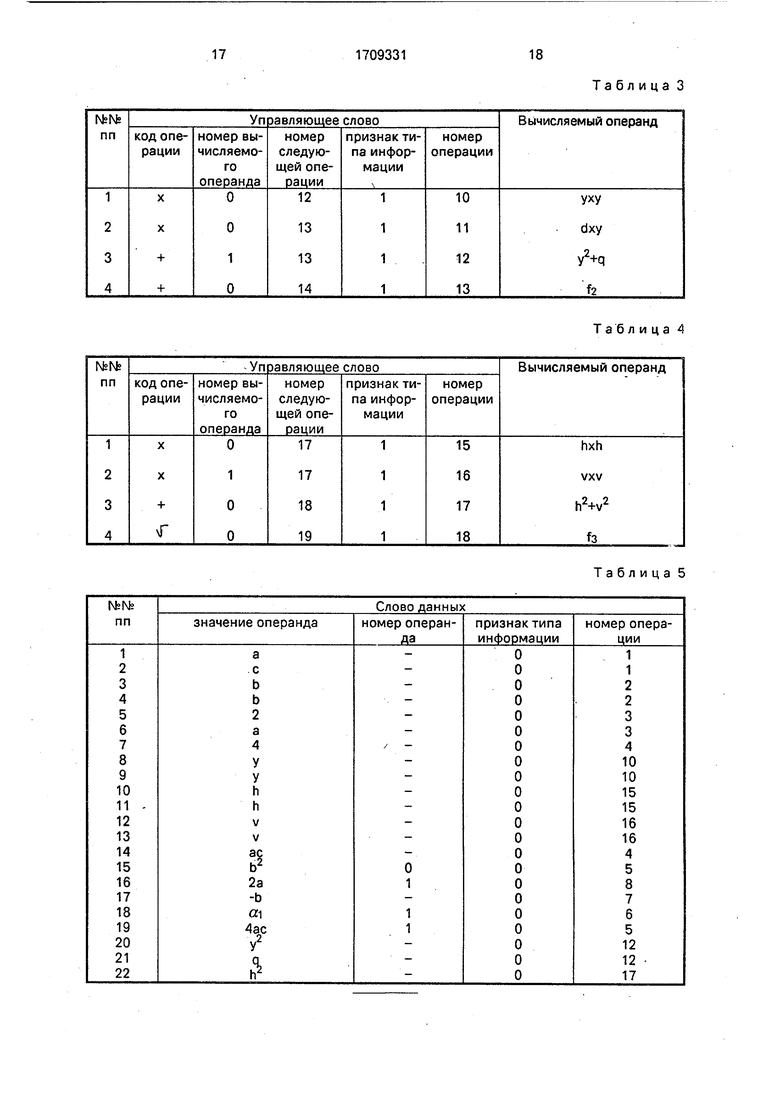

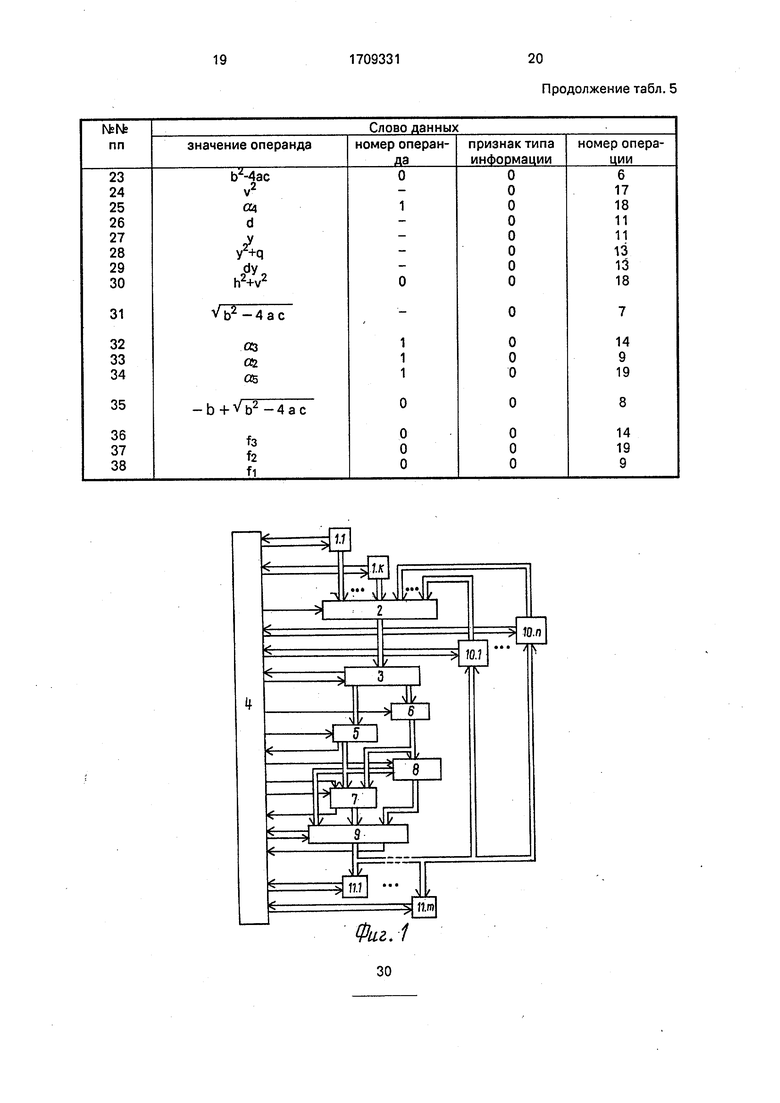

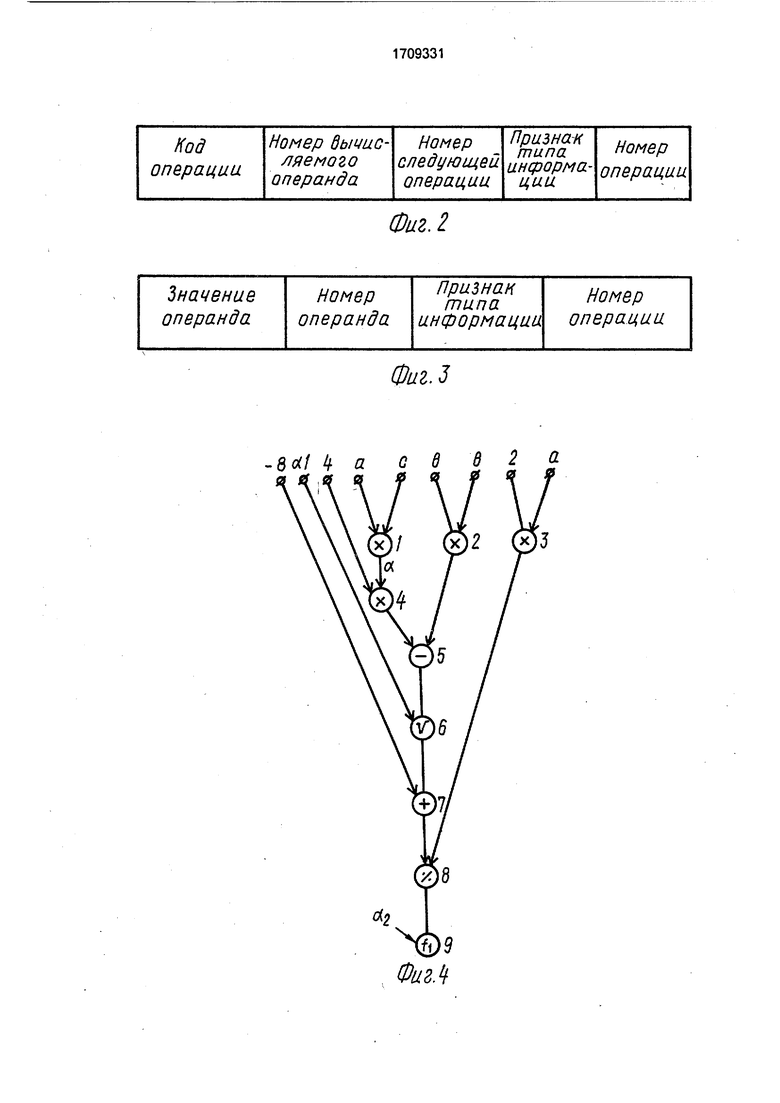

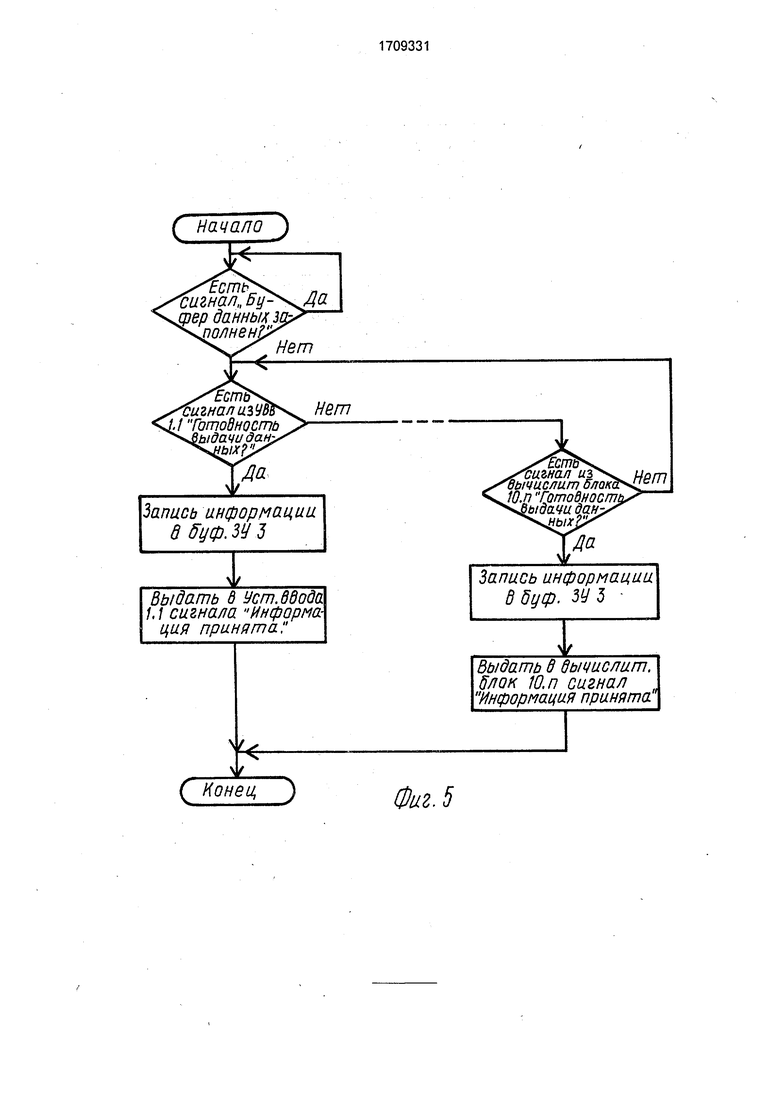

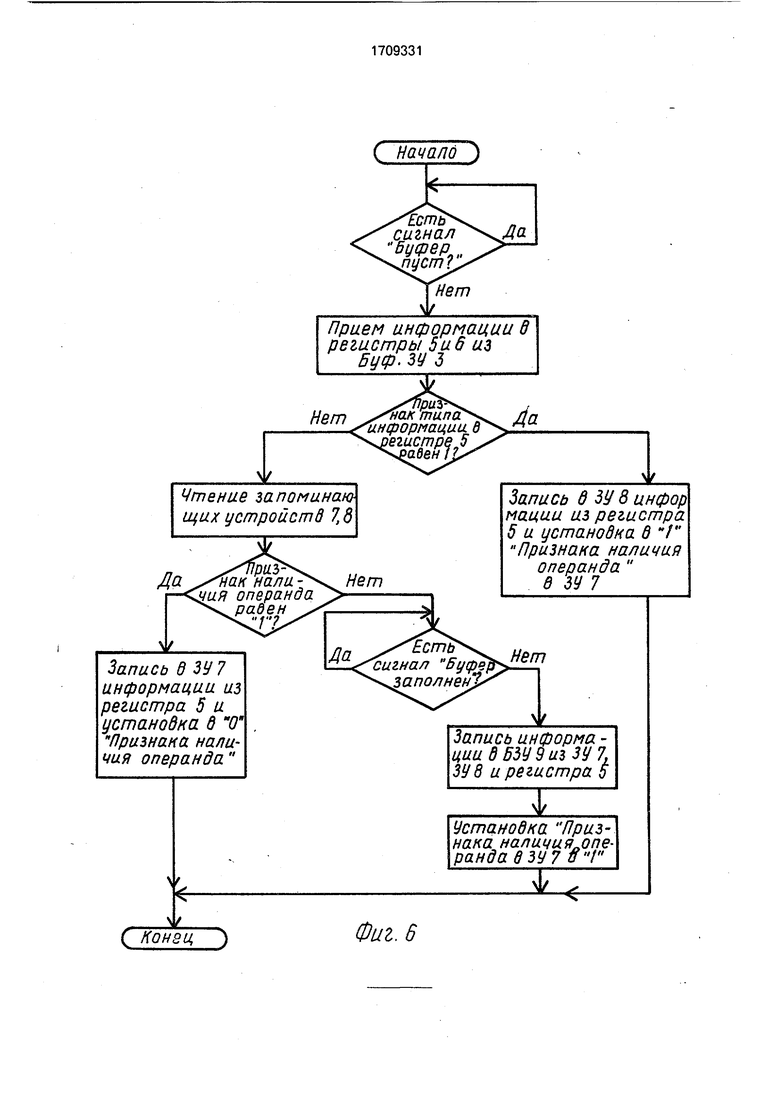

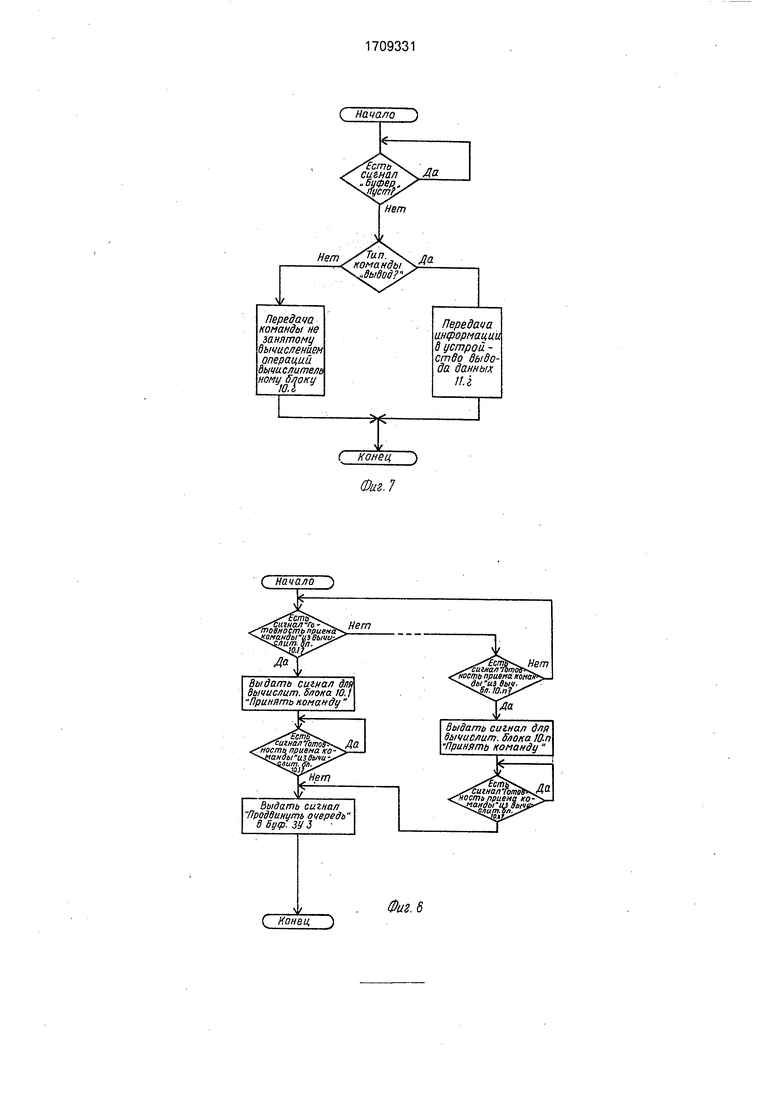

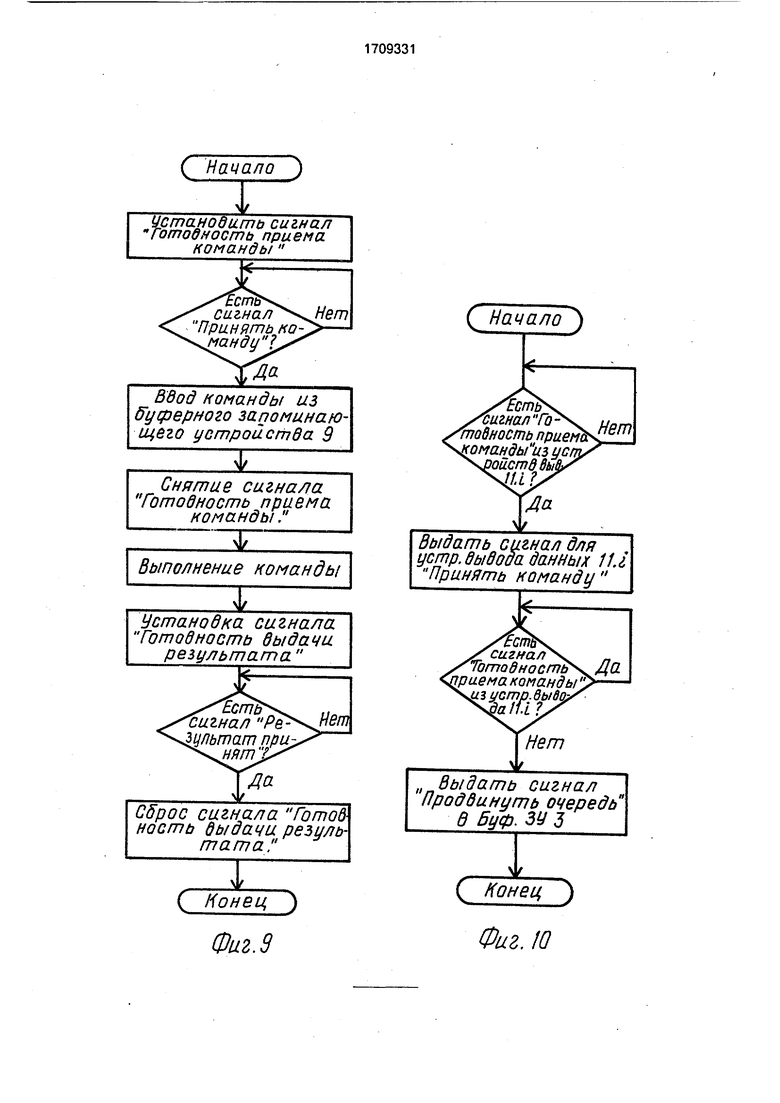

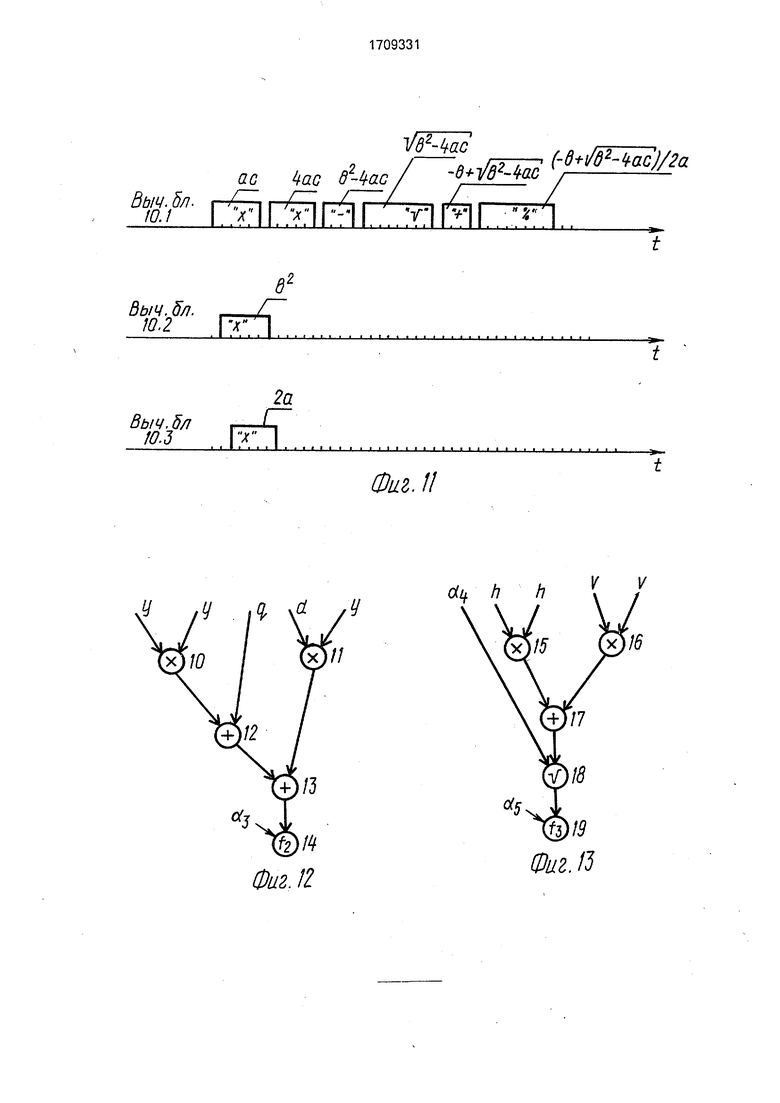

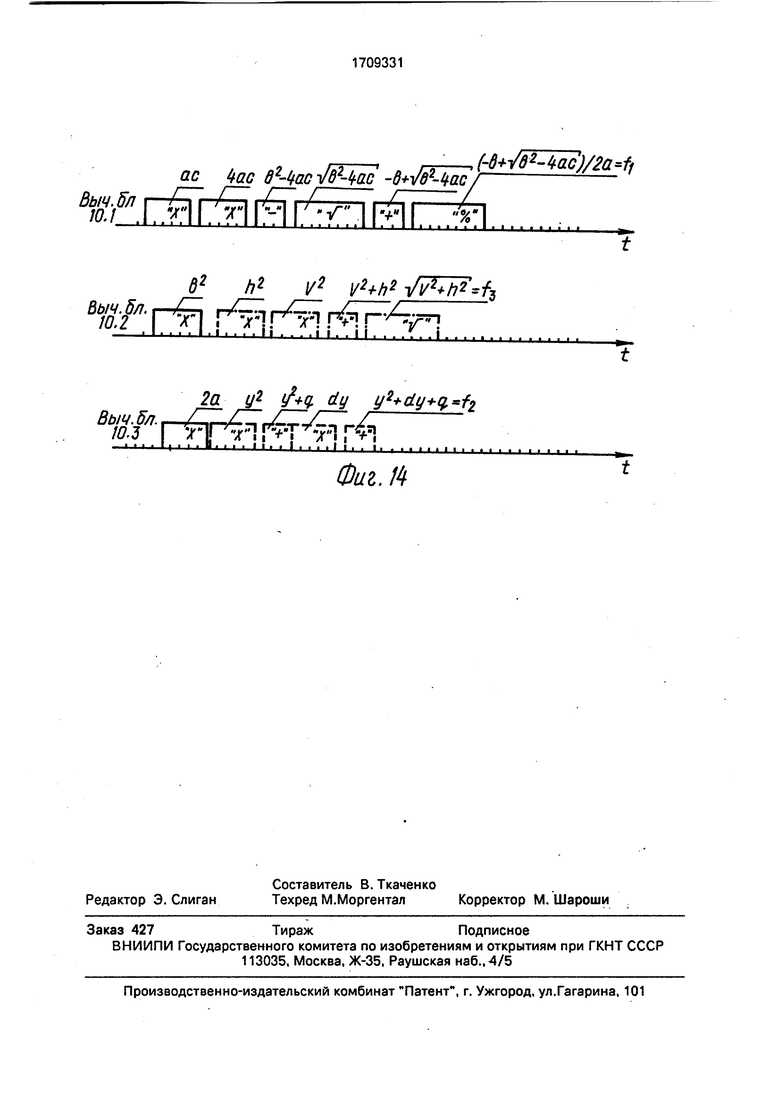

На фиг. 1 представлена структурная схема вычислительной системы; на фиг. 2 формат управляющего слова; на фиг. 3 формат слова данных; на фиг. 4 - граф алгоритма вычисления функции fi; на фиг. 5алгоритм загрузки управляющих слов и слов данных; на фиг. 6 - алгоритм формирования команды; на фиг. 7, 8 и 10 - алгоритмы распределения команд между вычислительными блоками и устройствами вывода данных; на фиг. 9 - алгоритм работы вычислительных блоков; на фиг. 11 - диаграмма занятости вычислительных блоков при вычислении функции fi; на фиг. 12 -граф алгоритма вычисления функции fa; на фиг. 13- граф алгоритма вычисления функции fs; на фиг. 14 - диаграмма занятости вычислительных блоков при совместном вычислении функций fi, f2, fa.

Вычислительная система, представленная на фиг, 1, содержит устройства 1.1Ik

ввода данных, информационные выходы которых через соответствущие группы входов коммутатора 2 подключены к блоку 3 буферной памяти данных, каждое устройство 1.1,...,1k ввода соединено с блоком 4 управления управляющим входом и выходом, а коммутатор 2 - управляющими входами.

Управляющие входы блока 3 буферной памяти данных, которые обеспечивают занесение информации и продвижение очере-х ди, подключены к выходам блока 4 управления, соответствующие входы которого соединены с выходами сигналов блока 3 буферной памяти данных, характеризующих степень его заполнения (Буфер занят и Буфер пуст).

К информационным входам регистра 5 данных и регистра б адреса подключены соответственно первая и вторая группы информационных выходов блока 3 буферной памяти данных. Управляющие входы занесения информации регистра 6 адреса и регистра 5 данных соединены с выходами блока 4 управления, а выход одного разряда регистра 5 данных (признак типа информации) подключен к соответствующему входу блока 4 управления. Информационные выходы регистра 6 адреса связаны с адресными входами блока 7 памяти операндов и блока 8 памяти управляющих слов. Информационные выходы регистра 5 данных подключены к входам данных блока 7 памяти операндов, блока 8 памяти управляющих слов и первой rpynqe информационных входов блока 9 буферной памяти команд. Вторая и третьи группы информационных входов блока 9 буферной памяти команд соединены соответственно с выходами данных блока 7 памяти операндов и блока 8

памяти управляющих СЛОБ. К входам управления записью и чтением блока 7 памяти операндов и блока 8 памяти управляющих слов подключены соответствующие выходы блока 4 управления. Один выход блока 4 управления подключен к входу одного разряда данных блока 7 памяти операндов, выход одноименного разряда данных которого соединен с одним входом блока 4 управления. К соответствующим входам блока 4 управления подведены выходы сигналов блока буферной памяти команд 9, указывающих на степень его заполнения, а также выходы группы разрядов, характеризующих тип команды и номер устройства вывода.

Управляющие входы записи и продвижения очереди (чтения) блока 9 буферной памяти команд связаны с соответствующими входами блока 4 управления.

Информационные выходы блока 9 буферной памяти команд подключены к информационным входам вычислительных блоков 10.1,...10.п и информационным входам устройств вывода данных 11.1,...11.т, управляющие входы и управляющие выходы которых подключены к соответствующим входам и выходам блока 4 управления. Информационные выходы каждого вычислительного блока 10.1,...10.п соединены с соответствующей группой информационных входов коммутатора 2.

Вычислительная система работает следующим образом.

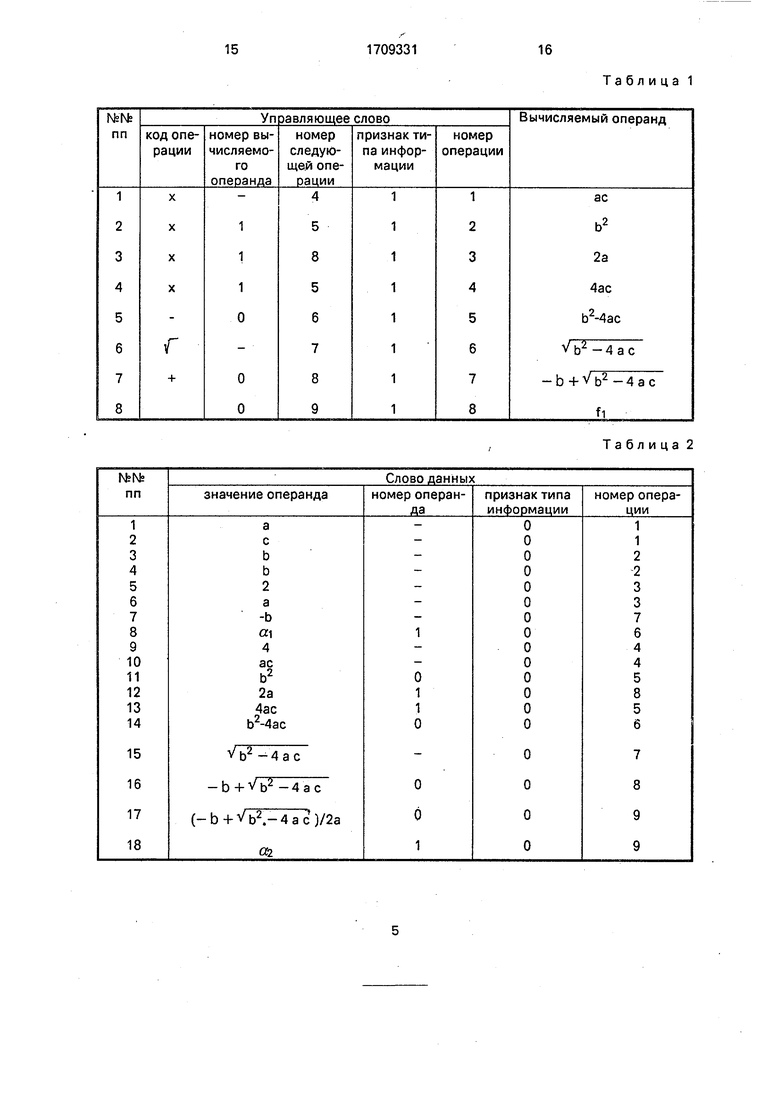

Исходная для вычислений информация вводится из устройств 1.1Ik ввода данных и представляют собой последовательность управляющих слов и слов данных, форматы которых представлены на фиг. 2 иЗ.

Управляющее слово содержит q-разрядное поле кода операций, разряд номера вычисляемого операнда, S-разрядное поле номера следующей операции, разряд признака типа информации и поле номера операции, имеющие m разрядов.

Разряд признака типа информации для всех управляющих слов имеет значение 1.

Информация, которая записывается в остальные поля управляющего слова, определяется заданным графом алгоритма вычислений, который строится независимо от числа вычислительных блоков 10.110.П.

В качестве примера на фиг. 4 представлен граф алгоритма вычисления выражения fi ( - b Ч- V b - 4 а с ) /2а. Каждой вершине графа, которая соответствует определенной операции, присваивается номер, отличный от номеров других вершин.

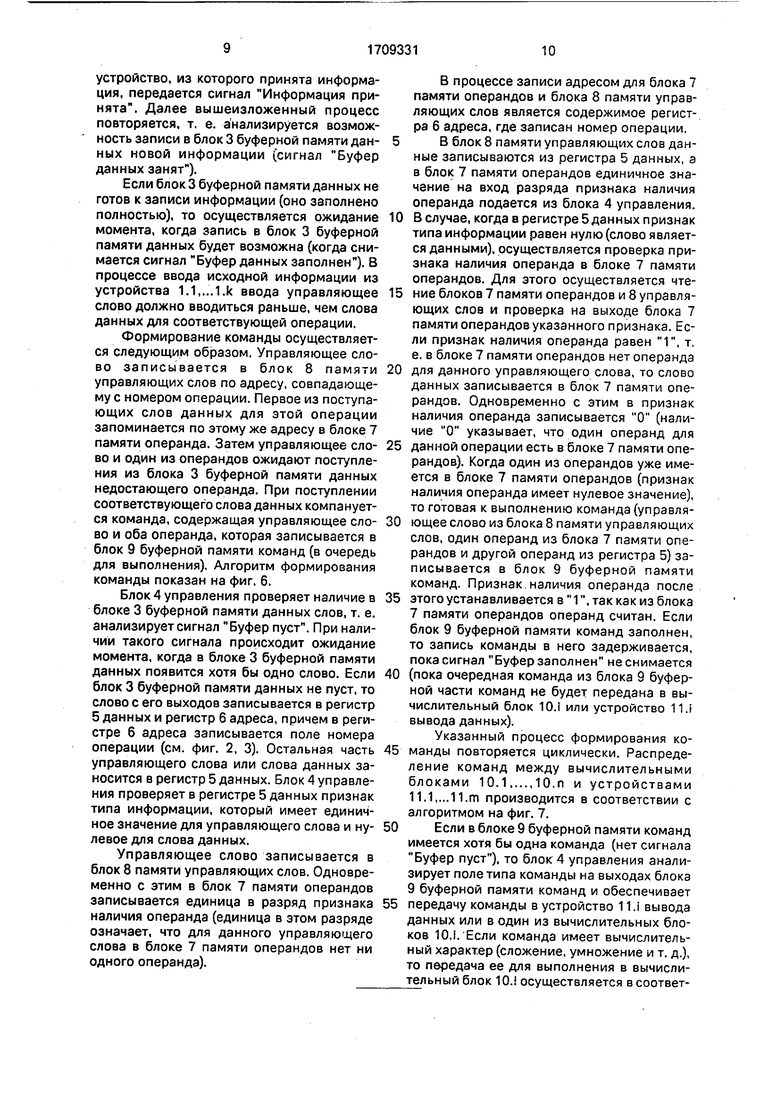

Управляющие слова для ках1сдой вершины графа представлены в табл. 1.

Вершина с номером 1 соответствует действию а а X с. В поле кода операции управляющего слова для данной вершины записывается код операции умножения, в поле номера операции - 1 (номер вершины), в поле следующей операции - 4 (номер вершины для которой, результат операции, является операндом), или можно было записать приращение 3 (разность номеров вершин, с помощью которой получают номер следующей операции, просуммировав номер текущей операции с разностью). Разряд номера вычисляемого операнда имеет смысл для операций, использующих данный операнд, которые не обладают свойством коммутативности (например, деление, вычитание и др.). В этом случае делимое и делитель, уменьшаемое и вычитаемое имеют разные номера (О или 1). Для операции, соответствующей первой вершине, в разряде номера вычисляемого операнда, отмеченного прочерком, можно записать любую цифру, так как следующая (четвертая) операция умножения обладает свойством коммутативности. Каждой дуге графа соответствует слово данных (фиг. 3), включающее п-разрядное поле значения операнда в принятой для данной операции форме (с плавающей или фиксированной запятой, в прямом или дополнительном кодах и т. д.), т-разрядное поле номера операции (номера вершин на графе, для которой дуга является входной), разряд номера операнда и разряд типа информации, который для слов данных (в отличие от управляющих слов) всегда имеет нулевое значение.

Слова данных для дуг графа на фиг. 4 представлены в табл. 2.

Для определенности предполагается, что для вычисления используются операции умножения ( X ), сложения ( + ), вычитание (-), деление ( / ) i извлечение корня (Т). Операнд «i для операции извлечения корня необходим лишь для инициализации выполнения данной операции (см. ниже). В разряде номера этого операнда записывается 1, а в операнде, из которого извлекается корень, - О. Вершина с номером 8 на графе (фиг. 4) соответствует операции передачи результата в устройство вывода 11.1. Слово данных, в котором записано значение результата, имеет нулевой признак операнда. Для инициализации или начала передачи результата в устройство вывода служит операнд сгг, в поле значения операнда которого записывается номер устройства вывода, а признак номера операнда имеет значение 1.

Граф для каждого алгоритма строится независимо от других. Номера вершин ни в

одном графе не должны повторяться.

Длина q поля кода операции (фиг. 2) определяется количеством команд и должна включать не менее log2N двоичных разрядов. Разрядность m должна обеспечивать

0 возможность записи самого большого номера операции (вершины на графе), а разрядность S - или максимального номера, или максимальной по модулю разности номеров операций. Разрядность поля значения операнда (фиг. 3) зависит от формы и точности представления операндов. Это поле может включать знаковые разряды, разряды мантиссы и порядка.

В исходном состоянии блоки 3 буферной памяти данных и 9 буферной памяти команд пусты (в них вырабатываются сигналы Буфер пуст). Цепи установки исходного состояния условно не показаны).

При функционировании системы можно

5 выделить три независимых процесса:

-ввод управляющих слов и слов данных

из устройств ввода данных 1.11 .k и ввода

результатов из вычислительных блоков 10.110.п в блок 3 буферной памяти дан0 ных;

-формирование команд и засылка их в блок 9 буферной памяти команд,

-распределение команд между вычислительными блоками 10.1,...10.п для их

5 дальнейшей обработки и устройствами вывода данных 11.1...,11.т.

Первый из указанных процессов иллюстрируется алгоритмом, представленным на фиг. 5. Блок 4 управления анализирует сигнал Буфер данных заполнен, формирующийся в блоке 3 буферной памяти данных, если оно заполнено полностью и запись в него невозможна. При отсутствии этого сигнала, в блоке 3 буферной памяти данных

5 можно записать информацию, блок 4 управления проверяет выходные сигналы Готовность выдачи данных от всех устройств

ввода данных 1.11.К и вычислительных

блоков 10.110.п циклически, начиная от

0 устройства 1.1 ввода данных и заканчивая вычислительным блоком 10.п. Готовые к выдаче данных устройства 1.1,...1К ввода данных и вычислительные блоки 10.1,...,10.п выставляют указанный сигнал Готовность

5 выдачи данных. При обнаружении готового к выдаче данных устройства ввода данных 1.1 (вычислительного блока lO.i) по сигналу блока 4 управления информация из этого устройства через коммутатор 2 записывается в блок 3 буферной памяти данных. В

устройство, из которого принята информация, передается сигнал Информация принята. Далее вышеизложенный процесс повторяется, т. е, анализируется возможность записи в блок 3 буферной памяти данных новой информации (сигнал Буфер данных занят).

Если блок 3 буферной памяти данных не готов к записи информации (оно заполнено полностью), то осуществляется ожидание момента, когда запись в блок 3 буферной памяти данных будет возможна (когда снимается сигнал Буфер данных заполнен). В процессе ввода исходной информации из устройства 1.1,...1.k ввода управляющее слово должно вводиться раньше, чем слова данных для соответствующей операции.

Формирование команды осуществляется следующим образом. Управляющее слово записывается в блок 8 памяти управляющих слов по адресу, совпадающему с номером операции. Первое из поступающих слов данных для зтой операции запоминается по этому же адресу в блоке 7 памяти операнда. Затем управляющее слово и один из операндов ожидают поступления из блока 3 буферной памяти данных недостающего операнда. При поступлении соответствующего слова данных компануется команда, содержащая управляющее слово и оба операнда, которая записывается в блок 9 буферной памяти команд (в очередь для выполнения). Алгоритм формирования команды показан на фиг. 6.

Блок 4 управления проверяет наличие в блоке 3 буферной памяти данных слов, т. е. анализирует сигнал Буфер пуст. При наличии такого сигнала происходит ожидание момента, когда в блоке 3 буферной памяти данных появится хотя бы одно слово. Если блок 3 буферной памяти данных не пуст, то слово с его выходов записывается в регистр 5 данных и регистр 6 адреса, причем в регистре 6 адреса записывается поле номера операции (см. фиг. 2, 3). Остальная часть управляющего слова или слова данных заносится в регистр 5 данных. Блок 4 управления проверяет в регистре 5 данных признак типа информации, который имеет единичное значение для управляющего слова и нулевое для слова данных.

Управляющее слово записывается в блок 8 памяти управляющих слов. Одновременно с зтим в блок 7 памяти операндов записывается единица в разряд признака наличия операнда (единица в зтом разряде означает, что для данного управляющего слова в блоке 7 памяти операндов нет ни одного операнда).

В процессе записи адресом для блока 7 памяти операндов и блока 8 памяти управляющих слов является содержимое регистра 6 адреса, где записан номер операции.

В блок 8 памяти управляющих слов данные записываются из регистра 5 данных, а в блок 7 памяти операндов единичное значение на вход разряда признака наличия операнда подается из блока 4 управления.

0 В случае, когда в регистре 5 данных признак типа информации равен нулю (слово является данными), осуществляется проверка признака наличия операнда в блоке 7 памяти операндов. Для зтого осуществляется чтение блоков 7 памяти операндов и 8 управляющих слов и проверка на выходе блока 7 памяти операндов указанного признака. Если признак наличия операнда равен 1, т. е. в блоке 7 памяти операндов нет операнда

0 для данного управляющего слова, то слово данных записывается в блок 7 памяти операндов. Одновременно с этим в признак наличия операнда записывается О (наличие О указывает, что один операнд для

5 данной операции есть в блоке 7 памяти операндов). Когда один из операндов уже имеется в блоке 7 памяти операндов (признак наличия операнда имеет нулевое значение), то готовая к выполнению команда (управляющее слово из блока 8 памяти управляющих слов, один операнд из блока 7 памяти операндов и другой операнд из регистра 5) записывается в блок 9 буферной памяти команд. Признак.наличия операнда после

5 зтого устанавливается в 1, так как из блока 7 памяти операндов операнд считан. Если блок 9 буферной памяти команд заполнен, то запись команды в него задерживается, пока сигнал Буфер заполнен не снимается

0 (пока очередная команда из блока 9 буферной части команд не будет передана в вычислительный блок 10.1 или устройство 11.1 вывода данных).

Указанный процесс формирования команды повторяется циклически. Распределение команд между вычислительными

блоками 10.110.п и устройствами

11.1,...11.т производится в соответствии с алгоритмом на фиг. 7.

0 Если в блоке 9 буферной памяти команд имеется хотя бы одна команда (нет сигнала Буфер пуст), то блок 4 управления анализирует поле типа команды на выходах блока 9 буферной памяти команд и обеспечивает

5 передачу команды в устройство 1 l.i вывода данных или в один из вычислительных блоков 10.i.Если команда имеет вычислительный характер (сложение, умножение и т. д.), то передача ее для выполнения в вычислительный блок 10.1 осуществляется в соответствии с алгоритмом, представленным на фиг. 8. Готовый к приему команды вычислительный блок 10.i выдает блок 4 управления сигнал Готовность приема команды. Блок 4 управления поочередно анализирует готовность каждого вычислительного блока 10.1, способного выполнить данную команду. Если очередной при просмотре вычислительный блок 10.1 готов принять команду, то блок 4 управления выдает ему управляющий сигнал Принять команду. После ввода команды вычислительный блок 10.1 снимает сигнал Готовность приема данных. В этом случае блок 4 управления продвигает очередь в блоке 9 буферной памяти команд.

В процессе обработки команды каждый вычислительный блок 10.1 обменивается с блоком 4 управления двумя входными и двумя выходными управляющими сигналами. Алгоритм обмена сигналами отражен на фиг. 9. Одна пара сигналов (входной и выходной) используется для ввода команды, а другая - для выдачи результата после выполнения команды. Операнды, которые используются для инициализации выполнения операций и не имеют смыслового значения (например ai, на графе фиг. 4) в вычислительных блоках 10.1,...,10.п необрабатыв)аются. Команда вывода, как отмечалось выше, содержит два операнда. В одном слове данных (фиг. 3) в поле значения операнда находится выводимая информация, а в другом - номер устройства вывода данных (11.1,...,1 l.m). Эти слова отличаются значениями номеров операндов (в одном устанавливается О, а в другом 1). Если на выходах блока 9 буферной памяти команд присутствуют команды вывода, то блок 4 управления анализирует номер устройства вывода данных и передает команду в устройство 11.1 вывода с этим номером.

Процедура передачи информации в устройство вывода данных 11.1 показана на фиг. 10.

Таким образом, в предлагамой системе одновременно могут выполняться несколько алгоритмов. Момент инициализации выполнения каждого алгоритма осуществляется независимо друг от друга. Никакой настройки аппаратуры на выполнение алгоритма определенного вида производить не требуется. Кроме того, данные для каждого алгоритма подготавливаются независимо как от других алгоритме, так и от числа вычислительных блоков в системе. Система остается работоспособной, если имеется хотя бы один вычислительный блок (остальные, например, отключены в результате проверки их работоспособности перед началом работы). Увеличение числа

вычислительных блоков приводит к автомаическому увеличению производительности системы. Рассмотрим примеры реализации алгоритмов для случая использования трех

вычислительных блоков.

Для вычисления fi( - b + )/ /2а в соответствии с алгоритмом на фиг. 4 из любых устройство 1.1,...,1К ввода данных в систему вводятся управляющие слова,

представленные в табл. 1. В результате изложенных выше процедур управляющие слова будут записаны в блоке 8 памяти управляющих слов, причем адресом каждого слова является номер этого слова.

Для инициализации вычисления fi в систему вводятся исходные данные. Для случая, когда данные вводятся в порядке, указанном в табл. 2, команды выполняются в вычислительных блоках 10.1, 10.2, 10.3 в

соответствии с диаграммой занятости, представленной на фиг. 11.

Строки 1-9 табл. 2 соответствуют исходным данным, а строки 10-17 - промежуточным результатам, формирующимся в

вычислительных блоках 10.1, 10.2, 10.3.

Строка 18 соответствует команде вывода.

Для инициализации вывода операнд аг

может быть введен в систему в любое время.

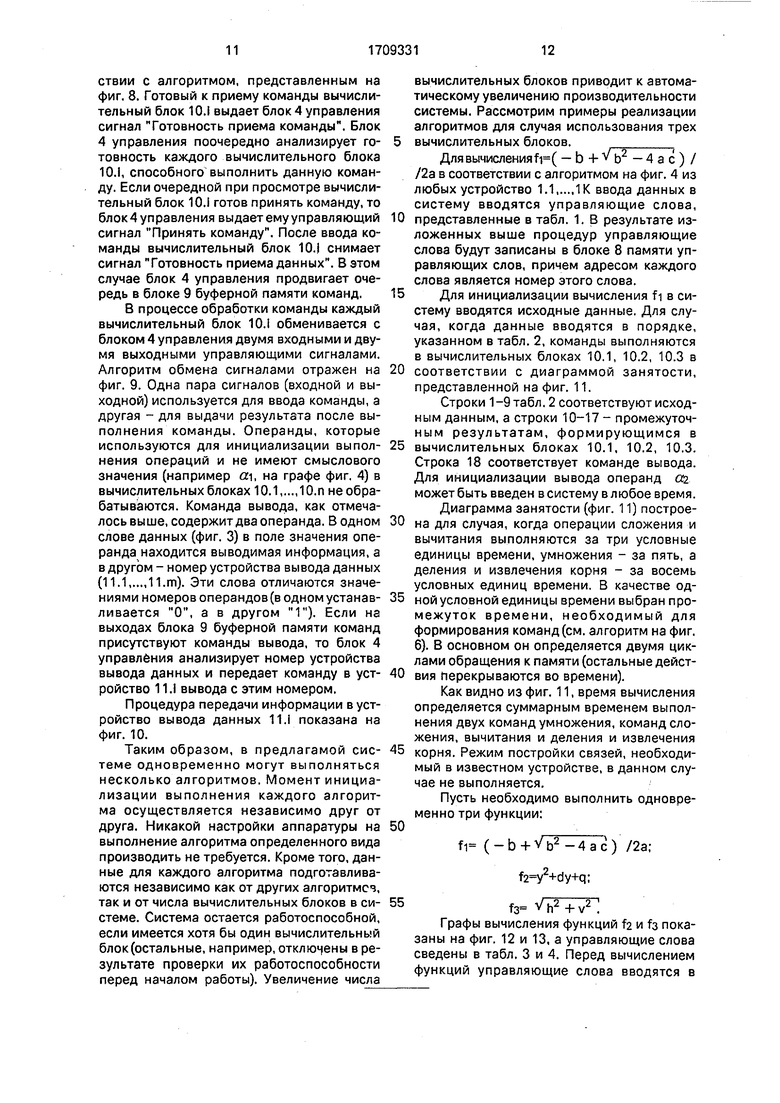

Диаграмма занятости (фиг. 11) построена для случая, когда операции сложения и вычитания выполняются за три условные единицы времени, умножения - за пять, а деления и извлечения корня - за восемь условных единиц времени. В качестве одной условной единицы времени выбран промежуток времени, необходимый для формирования команд (см. алгоритм на фиг. 6). В основном он определяется двумя циклами обращения к памяти (остальные дейстВИЯ Перекрываются во времени).

Как видно из фиг. 11, время вычисления определяется суммарным временем выполнения двух команд умножения, команд сложения, вычитания и деления и извлечения

корня. Режим постройки связей, необходимый в известном устройстве, в данном случае не выполняется.

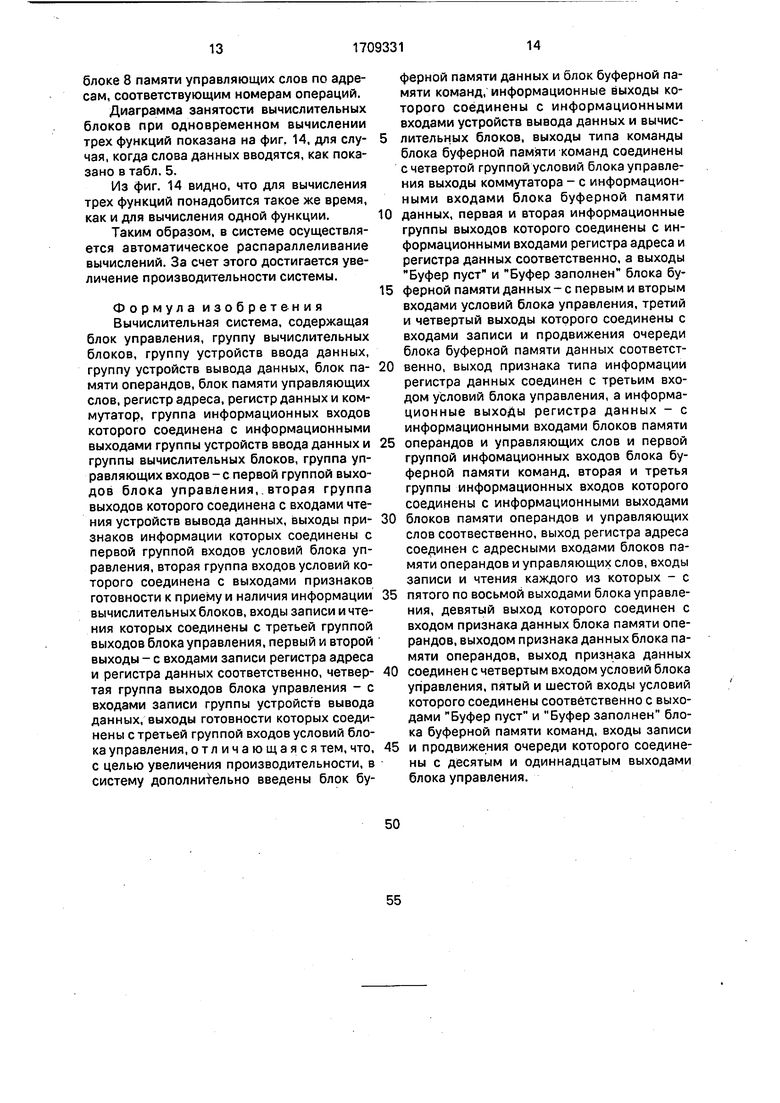

Пусть необходимо выполнить одновременно три функции:

.

fi ( - b Ч- V ь - 4 а с ) /2а;

f2 y2+dy+q:

f3 V h + у2;

Графы вычисления функций fa и fa показаны на фиг. 12 и 13, а управляющие слова сведены в табл. 3 и 4. Перед вычислением функций управляющие слова вводятся в

блоке 8 памяти управляющих слов по адресам, соответствующим номерам операций.

Диаграмма занятости вычислительных блоков при одновременном вычислении трех функций показана на фиг, 14, для случая, когда слова данных вводятся, как показано в табл. 5.

Из фиг. 14 видно, что для вычисления трех функций понадобится такое же время, как и для вычисления одной функции.

Таким образом, в системе осуществляется автоматическое распараллеливание вычислений. За счет этого достигается увеличение производительности системы.

Формула изобретения Вычислительная система, содержащая блок управления, группу вычислительных блоков, группу устройств ввода данных, группу устройств вывода данных, блок памяти операндов, блок памяти управляющих слов, регистр адреса, регистр данных и коммутатор, группа информационных входов которого соединена с информационными выходами группы устройств ввода данных и группы вычислительных блоков, группа управляющих входов-с первой группой выходов блока управления,.вторая группа выходов которого соединена с входами чтения устройств вывода данных, выходы признаков информации которых соединены с первой группой входов условий блока управления, вторая группа входов условий которого соединена с выходами признаков готовности к приему и наличия информации вычислительных блоков, входы записи и чтения которых соединены с третьей группой выходов блока управления, первый и второй выходы - с входами записи регистра адреса и регистра данных соответственно, четвертая группа выходов блока управления - с входами записи группы устройств вывода данных, выходы готовности которых соединены с третьей группой входов условий блокауправления,отл ича ю щая с я тем, что, с целью увеличения производительности, в систему дополнительно введены блок буферной памяти данных и блок буферной памяти команд, информационные выходы которого соединены с информационными входами устройств вывода данных и вычислительных блоков, выходы типа команды блока буферной памяти команд соединены с четвертой группой условий блока управления выходы коммутатора - с информационными входами блока буферной памяти

данных, первая и вторая информационные группы выходов которого соединены с информационными входами регистра адреса и регистра данных соответственно, а выходы Буфер пуст и Буфер заполнен блока буферной памяти данных - с первым и вторым входами условий блока управления, третий и четвертый выходы которого соединены с входами записи и продвижения очереди блока буферной памяти данных соответственно, выход признака типа информации регистра данных соединен с третьим входом условий блока управления, а информационные выходы регистра данных - с информационными входами блоков памяти

операндов и управляющих слов и первой группой инфомационных входов блока буферной памяти команд, вторая и третья группы информационных входов которого соединены с информационными выходами

блоков памяти операндов и управляющих слов соотвественно, выход регистра адреса соединен с адресными входами блоков памяти операндов и управляющих слов, входы записи и чтения каждого из которых - с

пятого по восьмой выходами блока управления, девятый выход которого соединен с входом признака данных блока памяти операндов, выходом признака данных блока памяти операндов, выход признака данных

соединен с четвертым входом условий блока управления, пятый и шестой входы условий которого соединены соответственно с выходами Буфер пуст и Буфер заполнен блока буферной памяти команд, входы записи

и продвижения очереди которого соединены с десятым и одиннадцатым выходами блока управления.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1990 |

|

RU2030785C1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| СПОСОБ КОДИРОВАНИЯ И ИСПОЛНЕНИЯ КОНТЕКСТНО-ЗАВИСИМОЙ ПРОГРАММЫ МУЛЬТИКЛЕТОЧНЫМ ПРОЦЕССОРОМ, МУЛЬТИКЛЕТОЧНЫЙ ПРОЦЕССОР, КЛЕТКА И КОММУТАЦИОННОЕ УСТРОЙСТВО МУЛЬТИКЛЕТОЧНОГО ПРОЦЕССОРА ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2013 |

|

RU2530690C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| Программируемый процессор спектральной обработки сигналов | 1982 |

|

SU1092517A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

Изобретение относится к вычислительной технике и может быть использовано припостроении высокопроизводительных вычислительных систем для решения задач, алгоритмы которых имеют последовательно-параллельную структуру. Цель изобретения - повышение производительности вычислительной системы. Вычислительная система содержит блок управления, группу вычислительных блоков, группу устройств ввода данных, группу устройств вывода данных, блок памяти операндов, блок памяти управляющих слов, регистр адреса, регистр данных, коммутатор, блок буферной памяти данных и блок буферной памяти команд. Предлагаемая система позволяет увеличить производительность за счет совмещения во времени реализации различных алгоритмов в любом сочетании. 14 ил., 5 табл.^•^ Nwfe

Таблица 2

Таблица 3

Таблица 4

Таблица 5

Продолжение табл. 5

Фиг.1

-Qo(i i а об

Фиг. 2

Фиг.З

5

Ф1/г. (Начало Выдать в Уст.вбода /. / сигнала Информация принята:

( Но не ц )

Выдать 8 быцислит. 5лок Ю.п сигнал . Информация принята

Фиг. 5 Запись информации. д5уф. ЗУ 5 С Начало )

Прием информации 6 регистры 5и6 из Чтение шпоминанзщих устройстд 7, д „ . JptiS Да .ак нала. чая операнда раден ГЪ Л Запись в ЗУ информации из регистра 5 и установна д О Признана наличия операнда

/

С Конец ) Буф. ЗУ J Нет

Установна Признака наличия операнда в ЗУ 7

Фиг. 6 Запись в 5У 8 инфор мации из регистра 5 и установиа в / Признака наличия операнда в ЗУ 7 г аТ-ву заполнен Запись информа ции в 65У 9 из ЗУ 7, ЗУ 8 и регистра b

Нет

С Нон ей, J

Да

Выдать сигнал бпй вычислит. SaoKO. 10.п Принять команду

0иг.8

С Начало J

исшановать сигнал готовность приема команды

ЕстВ . сагнал Припяти

ДО

Ввод команды из буферного запоминаюицвго устройства 9

Снртие сигнала Готовность приема но манды.

Выполнение команды

Установка сигнала

Готовность выдачи.

результата

ЕсптВ Сигнал Ре пьпштпри;

С5рос сигнала Го т об ность вшдачи результата.

I

С Ноне ц 3

Фиг. 9

( Начало

, стб

У игналТо- upm тподность привм WMaHdbi u2yc, оистдды IfLf.

Выдать сигнал для устр, вывода данных 11. i Принять команду

ст

сигнал „ Тотодность ДО. 1раема ког анды Ml ycrnp.QbiOo;/ alUy

Нет

,, Выдать сигнал Продвинуть очередь в Буф. ЗУ 3

( Конец )

Фиг, W дыч. 5л. fOJ

6

Выч. 5л. pri Ю.2 ас ifac дЧас/ -f S I viiTrii iT rimL.. -; f-TT- (-6i-i/d4 J/2a

Выч. 5л Ю.З x

I i j I I

Фиг. //

di h

5

ас fyac вЦас -6+Ve -ffuc

Выч.л

/аГ.Гг Г Fl Г

6 h V

/Щ±1Г21

y-1 rV .7Т1 .....X - I 1 11

2a у2 Lf-t-q, dy y +dy-i-q f

r| r1 4тх1Г Й I.. I.... 11.. I. т.........

г. /

, (-e- i/d - ac}/2a ff

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1990-02-28—Подача