Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известно троичное счетное устройство [1] которое может использоваться в качестве троичного триггера. Устройство содержит два RS-триггера, каждый из которых состоит из двух элементов И-НЕ, четыре двухвходовых элемента И-НЕ и два многовходовых элемента И-НЕ. Входная шина устройства подключена к одному из входов первого и второго многовходовых элементов И-НЕ и первого двухвходового элемента И-НЕ, выходы которых соединены соответственно с  -входом первого RS-триггера, с

-входом первого RS-триггера, с  -входом второго RS-триггера и

-входом второго RS-триггера и  -входом второго RS-триггера. Второй, третий и четвертый входы первого многовходового элемента И-НЕ подключены соответственно к

-входом второго RS-триггера. Второй, третий и четвертый входы первого многовходового элемента И-НЕ подключены соответственно к  -входу первого RS-триггера, к выходу второго элемента И-НЕ и к выходу первого элемента И-НЕ. Второй и третий входы второго многовходового элемента И-НЕ подключены соответственно к инверсному выходу и

-входу первого RS-триггера, к выходу второго элемента И-НЕ и к выходу первого элемента И-НЕ. Второй и третий входы второго многовходового элемента И-НЕ подключены соответственно к инверсному выходу и  -входу первого RS-триггера. Второй вход первого двухвходового элемента И-НЕ подключен к выходу четвертого двухвходового элемента И-НЕ, входы которого соединены соответственно с

-входу первого RS-триггера. Второй вход первого двухвходового элемента И-НЕ подключен к выходу четвертого двухвходового элемента И-НЕ, входы которого соединены соответственно с  -входом второго RS-триггера и с выходом третьего элемента И-НЕ. Входы третьего двухвходового элемента И-НЕ подключены соответственно к инверсному выходу и

-входом второго RS-триггера и с выходом третьего элемента И-НЕ. Входы третьего двухвходового элемента И-НЕ подключены соответственно к инверсному выходу и  -входу второго RS-триггера, а выход к

-входу второго RS-триггера, а выход к  -входу первого RS-триггера. Первый и второй входы второго элемента И-НЕ соединены соответственно с

-входу первого RS-триггера. Первый и второй входы второго элемента И-НЕ соединены соответственно с  -входом и инверсным выходом первого RS-триггера.

-входом и инверсным выходом первого RS-триггера.

Признаком, совпадающим с существенным признаком предлагаемого изобретения, является наличие шины счетных импульсов.

Наиболее близким к изобретению является делитель частоты на три [2] который может использоваться в качестве троичного триггера и содержит два синхронных D-триггера и двухвходовой элемент ИЛИ-НЕ. Прямой выход первого триггера соединен с D-входом второго триггера. Счетные входы первого и второго триггеров соединены с первым входом элемента ИЛИ-НЕ и с входной шиной счетных импульсов. D-вход первого триггера соединен с инверсным выходом второго триггера и с вторым входом элемента ИЛИ-НЕ. Выход элемента ИЛИ-НЕ подключен к R-входу первого триггера.

Признаками, совпадающими с существенными признаками предлагаемого изобретения, являются наличие первого и второго синхронных D-триггеров, инверсный выход последнего из которых соединен с одним из входов первого элемента ИЛИ-НЕ, и шины счетных импульсов.

Недостатком известных устройств является низкая помехоустойчивость по счетному входу и по шине питания, обусловленная высоким быстродействием микросхем и потерей состояния устройства при перерывах в питании нерегламентированной длительности.

Техническим результатом изобретения является повышение помехоустойчивости.

Для этого в троичный триггер, содержащий первый и второй синхронные D-триггеры, инверсный выход последнего из которых соединен с одним из входов первого элемента ИЛИ-НЕ, и шину счетных импульсов, введены два элемента памяти на магнитном сердечнике с прямоугольной петлей гистерезиса и обмоткой каждый, второй, третий и четвертый элементы ИЛИ-НЕ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, три резистора, конденсатор и шина установки исходного состояния, соединенная с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с шиной счетных импульсов, установочными входами D-триггеров, первым входом второго элемента ИЛИ-НЕ и первым выводом первого резистора, второй вывод которого через конденсатор соединен с общей шиной и непосредственно с вторым входом второго элемента ИЛИ-НЕ, выход которого соединен с входами синхронизации D-триггеров и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с другим входом первого элемента ИЛИ-НЕ и с прямым выходом первого D-триггера, информационный вход которого соединен с началом обмотки сердечника первого элемента памяти, конец которой соединен с выходом и первым входом соответственно первого и третьего элементов ИЛИ-НЕ, а средняя точка обмотки через второй резистор с выходом третьего элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом четвертого элемента ИЛИ-НЕ, выход которого через третий резистор соединен со средней точкой обмотки сердечника второго элемента памяти, начало которой соединено с информационным входом второго D-триггера, конец с выходом и вторым входом соответственно второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четвертого элемента ИЛИ-НЕ.

Указанная совокупность признаков позволяет повысить помехоустойчивость путем введения инерционности по счетному входу в виде интегрирующей RC-цепи и постоянного принудительного удержания триггеров в нулевом состоянии в паузе между счетными импульсами, а также путем хранения информации о состоянии устройства в сердечниках элементов памяти, которая сохраняется при перерывах в питании.

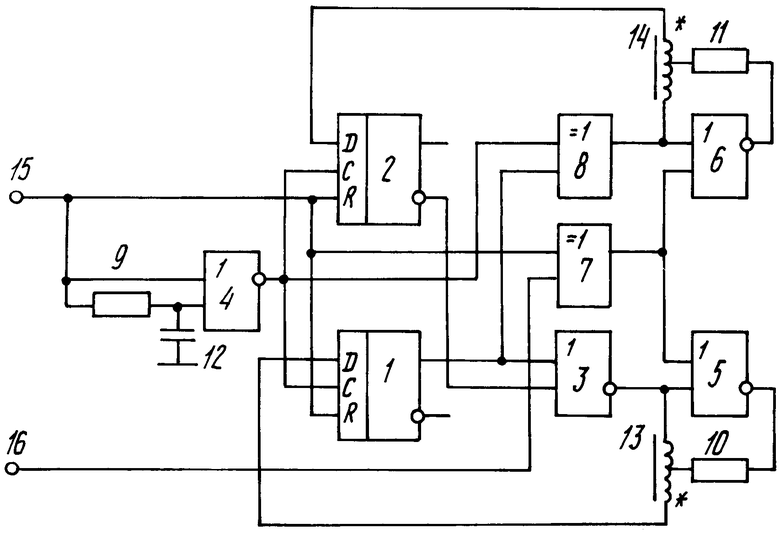

На чертеже приведена схема троичного триггера.

Троичный триггер содержит первый 1 и второй 2 синхронные D-триггеры, первый 3, второй 4, третий 5 и четвертый 6 элементы ИЛИ-НЕ, первый 7 и второй 8 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 9, второй 10 и третий 11 резисторы, конденсатор 12, первый 13 и второй 14 элементы памяти на магнитном сердечнике с прямоугольной петлей гистерезиса и обмоткой каждый, шину 15 счетных импульсов и шину 16 установки исходного состояния. Шина 16 установки исходного состояния соединена с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7, второй вход которого соединен с шиной 15 счетных импульсов, установочными входами триггеров 1 и 2, первым входом элемента ИЛИ-НЕ 4 и через интегрирующую цепь, состоящую из резистора 9 и конденсатора 12, с вторым входом элемента ИЛИ-НЕ 4. Выход элемента ИЛИ-НЕ 4 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и с входами синхронизации триггеров 1 и 2, инверсный выход последнего из которых соединен с первым входом элемента ИЛИ-НЕ 3. Второй вход элемента ИЛИ-НЕ 3 соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и прямым выходом триггера 1. Начало обмотки сердечника элемента 13 памяти соединено с информационным входом триггера 1, конец с выходом и первым входом элементов ИЛИ-НЕ 3 и 5 соответственно. Второй вход элемента ИЛИ-НЕ 5 соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и первым входом элемента ИЛИ-НЕ 6. Начало обмотки сердечника элемента 14 памяти соединено с информационным входом триггера 2, конец с выходом и вторым входом соответственно элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и элемента ИЛИ-НЕ 6. Средние точки обмоток сердечников элементов 13 и 14 памяти через соответственно резисторы 10 и 11 соединены с выходами элементов ИЛИ-НЕ 5 и 6 соответственно.

Троичный триггер работает следующим образом.

В режиме хранения информации на шине 15 счетных импульсов присутствует уровень логической "1", а на шине 16 установки исходного состояния уровень логического "0". При этом на выходах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и элементов ИЛИ-НЕ 3, 5 и 6 уровень логического "0", ток через обмотки сердечников элементов 13 и 14 памяти не протекает. Для записи в сердечники элементов 13 и 14 памяти исходного нулевого состояния на шину 16 установки исходного состояния подается импульс положительной полярности. Триггеры 1 и 2 удерживаются в нулевом состоянии по R-входам, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 появляется уровень логического "0", а на выходах элементов ИЛИ-НЕ 5 и 6 уровень логической "1". Через резисторы 10 и 11 и нижнюю часть обмоток сердечников элементов 13 и 14 памяти на выход элементов ИЛИ-НЕ 3 и ИСКЛЮЧАЮЩЕЕ ИЛИ 8 соответственно протекает ток, намагничивающий сердечники элементов 13 и 14 памяти в нулевое состояние. За нулевое состояние сердечника условно принято состояние, в которое он намагничивается при вытекающем из конца обмотки токе. После записи нулевого состояния на шине 16 установки исходного состояния восстанавливается уровень логического "0".

Переключение троичного триггера в первое состояние начинается по переднему фронту импульса отрицательной полярности (относительно напряжения питания) на шине 15 счетных импульсов. При этом на выходе элементов ИЛИ-НЕ 4, на счетных входах и на прямых выходах триггеров 1 и 2 сохраняются уровни логического "0". На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 появляется уровень логического "0", а на выходах элементов ИЛИ-НЕ 5 и 6 уровень логической "1". Через резисторы 10 и 11 и нижнюю часть обмоток сердечников элементов 13 и 14 памяти протекает ток. Так как сердечники находятся в нулевом состоянии, на начале обмоток сердечников элементов 13 и 14 памяти и соответственно на информационных входах триггеров 1 и 2 формируются короткие импульсы помехи из-за непрямоугольности петли гистерезиса магнитного сердечника. После разряда конденсатора 12 через резистор 9, на выходе элемента ИЛИ-НЕ 4 появляется уровень логической "1", триггеры 1 и 2 при этом сохраняют нулевое состояние, так как на их информационных входах уже закончились импульсы помехи положительной полярности. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 появляется уровень логической "1", а на выходе элемента ИЛИ-НЕ 6 уровень логического "0". Через нижнюю часть обмотки сердечника элемента 14 памяти и резистор 11 начинает протекать ток в противоположном направлении и сердечник элемента 14 памяти намагничивается в единичное состояние. На начале обмотки сердечника элемента 14 памяти формируется импульс отрицательной полярности, не влияющий на состояние триггера 2. По окончании импульса на шине 15 счетных импульсов ток через обмотки сердечников элементов 13 и 14 памяти не протекает и в сердечнике элемента 13 памяти хранится "0", в сердечнике элемента 14 памяти "1". Триггеры 1 и 2 удерживаются в нулевом состоянии по R-входам.

Следующим импульсом на шине 15 счетных импульсов троичный триггер переключается во второе состояние следующим образом. По переднему фронту импульса снимается удержание триггеров 1 и 2 в нулевом состоянии по R-входам. На выходе элемента ИЛИ-НЕ 4 сохраняется уровень логического "0" на время разряда конденсатора 12 через резистор 9. На выходах элементов ИЛИ-НЕ 5 и 6 появляется уровень логической "1" и через нижние части обмоток сердечников элементов 13 и 14 памяти начинает протекать ток. Так как сердечник элемента 13 памяти находился в нулевом состоянии, на начале обмотки этого элемента 13 памяти и на информационном входе триггера 1 формируется короткий импульс помехи. Сердечник элемента 14 памяти находился в единичном состоянии, поэтому он начинает перемагничиваться в нулевое состояние и на начале обмотки сердечника элемента 14 памяти и на информационном входе триггера 2 формируется полезный импульс положительной полярности, длительность которого значительно превышает длительность импульса помехи. После разряда конденсатора 12 на выходе элемента ИЛИ-НЕ 4 появляется уровень логической "1" и, так как на информационном входе триггера 2 также присутствует уровень логической "1", триггер 2 переключается в единичное состояние, а триггер 1 сохраняет нулевое состояние. На выходах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и элемента ИЛИ-НЕ 3 появляется уровень логической "1", а на выходах элементов ИЛИ-НЕ 5 и 6 уровень логического "0". Сердечник элемента 13 памяти перемагничивается в единичное состояние, а сердечник элемента 14 памяти восстанавливает единичное состояние. Триггеры 1 и 2 при этом сохраняют соответственно нулевое и единичное состояние. После окончания процесса перемагничивания заканчивается импульс на шине 15 счетных импульсов, триггеры 1 и 2 удерживаются в нулевом состоянии, в сердечниках элементов 13 и 14 памяти хранится "1".

Третьим импульсом на шине 15 счетных импульсов троичный триггер переключается в исходное нулевое состояние следующим образом. При появлении уровня логического "0" на шине 15 счетных импульсов сердечники элементов 13 и 14 памяти начинают перемагничиваться из единичного в нулевое состояние. При этом на началах обмоток сердечников элементов 13 и 14 памяти и на информационных входах триггеров 1 и 2 формируются полезные импульсы положительной полярности. По переднему фронту импульса на выходе элемента ИЛИ-НЕ 4, задержанному относительно переднего фронта импульса на шине 15 счетных импульсов, триггеры 1 и 2 переключаются в единичное состояние. При этом направление тока, протекающего через резисторы 10 и 11 и нижние части обмоток сердечников элементов 13 и 14 памяти, остается неизменным и сердечники продолжают перемагничиваться в нулевое состояние.

Далее устройство работает аналогичным образом. Информация о состоянии троичного триггера снимается с выходов триггеров 1 и 2 во время присутствия импульса отрицательной полярности на шине 15 счетных импульсов, когда информация из сердечников элементов 13 и 14 памяти переписана в триггеры 1 и 2. Нулевому состоянию устройства соответствует и нулевое состояние триггеров 1 и 2, в первом состоянии устройства триггер 1 находится в нулевом состоянии, а триггер 2 в единичном, во втором состоянии триггеры 1 и 2 находятся в единичном состоянии.

Постоянная времени интегрирующей RC-цепи выбирается, исходя из требований помехоустойчивости по счетному входу, и должна быть больше, чем возможная длительность помехи, формируемой на обмотках сердечников элементов 13 и 14 памяти за счет непрямоугольности петли гистерезиса сердечников.

Помехоустойчивость устройства по шине 15 счетных импульсов и сохранение информации при перерывах в питании нерегламентированной длительности достигается за счет введения инерционности в виде интегрирующей RC-цепи по шине счетных импульсов и за счет хранения информации о состоянии троичного триггера в энергонезависимых элементах памяти на магнитных сердечниках с прямоугольной петлей гистерезиса, обмотки которых запитываются только при переключении устройства в следующее состояние, а также за счет принудительного удержания устройства в нулевом состоянии в паузе между счетными импульсами.

С целью подтверждения осуществимости предлагаемого решения и достигнутого технического результата был изготовлен и испытан лабораторный макет, выполненный по схеме, представленной на чертеже. Макет был выполнен на микросхемах 564 серии. Напряжение питания 10 В. Элементы памяти выполнены на базе сердечников из сплава 77 НМД. Постоянная времени интегрирующей RC-цепи равна 5 мкс. Длительность импульса начальной установки и счетных импульсов равна 100 мкс.

Макет троичного триггера испытан в диапазоне температур от минус 50 до плюс 60оС. Проведенные испытания показали осуществимость предлагаемого устройства и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧИК ИМПУЛЬСОВ, СОХРАНЯЮЩИЙ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХ ПИТАНИЯ | 1991 |

|

RU2047271C1 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1780487A1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2036547C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2034397C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| ТРОИЧНЫЙ ТРИГГЕР | 1990 |

|

SU1804270A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1990 |

|

SU1753919A1 |

Использование: изобретение относится к импульсной технике и позволяет повысить помехоустойчивость. Сущность изобретения: троичный триггер содержит два синхронных d-триггера 1 и 2, четыре элемента ИЛИ-НЕ 3 и 6, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8, три резистора 9 - 11, конденсатор 12, два элемента 13 и 14 памяти на магнитном сердечнике с прямоугольной петлей гистерезиса и обмоткой каждый, шину 15 счетных импульсов и шину 16 установки исходного состояния. 1 ил.

ТРОИЧНЫЙ ТРИГГЕР, содержащий первый и второй синхронные D-триггеры, инверсный выход последнего из которых соединен с одним из входов первого элемента ИЛИ НЕ, и шину счетных импульсов, отличающийся тем, что в него введены два элемента памяти на магнитном сердечнике с прямоугольной петлей гистерезиса и обмоткой каждый, второй, третий и четвертый элементы ИЛИ НЕ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, три резистора, конденсатор и шина установки исходного состояния, соединенная с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с шиной счетных импульсов, установочными входами D-триггеров, первым входом второго элемента ИЛИ НЕ и первым выводом первого резистора, второй вывод которого через конденсатор соединен с общей шиной и непосредственно с вторым входом второго элемента ИЛИ НЕ, выход которого соединен с входами синхронизации D-триггеров и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с другим входом первого элемента ИЛИ НЕ и прямым выходом первого D-триггера, информационный вход которого соединен с началом обмотки сердечника первого элемента памяти, конец которой соединен с выходом и первым входом соответственно первого и третьего элементов ИЛИ НЕ, а средняя точка обмотки через второй резистор с выходом третьего элемента ИЛИ НЕ, второй вход которого соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом четвертого элемента ИЛИ НЕ, выход которого через третий резистор соединен со средней точкой обмотки сердечника второго элемента памяти, начало которой соединено с информационным входом второго D-триггера, конец с выходом и вторым входом соответственно второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четвертого элемента ИЛИ НЕ.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Делитель частоты на три | 1986 |

|

SU1354414A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-06-27—Публикация

1991-11-22—Подача