Изобретение относится к области телемеханики, автоматики и вычислительной техники и предназначено для обработки данных и исправления одиночных сбоев в регистровых файлах микропроцессоров.

Уменьшение технологических норм изготовления изделий микроэлектроники приводит к уменьшению критического заряда, требуемого для возникновения одиночного сбоя в элементах хранения цифровых схем. Проблема усугубляется для электронных устройств, применяемых в авиации и космосе, где воздействие атмосферных нейтронов и тяжелых ионов во много раз сильнее, чем на поверхности земли.

Одним из основных блоков любого микропроцессора является регистровый файл, в котором сосредоточены основное количество элементов хранения, расположенных вне встроенных блоков памяти.

Регистровый файл существенно отличается от встроенных блоков памяти, таких как кэш-память, поскольку к нему предъявляются особые требования по быстродействию, по количеству портов чтения и записи и пр., требуются особые методы и решения для защиты его содержимого от одиночных сбоев. Стандартным методом защиты данных в регистровых файлах является защита с помощью корректирующих кодов. Принцип действия защиты заключается в том, что специальное устройство формирует дополнительные разряды на основе исходных данных таким образом, что при сбое любого элемента хранения возможно обнаружить его положение и исправить. Наиболее часто применяются схема кодирования кодом Хеммина, позволяющая исправлять одиночную и обнаруживать двойную ошибку («Architecture Design for Soft Errors», Mukherjee S. // Elsevier, 2008, стр.172-186).

Известны и другие схемы. Пример такой схемы применительно к регистровому файлу описан ниже. В этой схеме входное слово данных, разрядностью I, поступает в блок формирования корректирующих кодов, где на его основе формируются дополнительные D разрядов, которые записываются в соответствующий регистр регистрового файла вместе с исходным словом. При чтении, блок проверки и восстановления проверяет целостность слова данных, вычисляя корректирующие коды и сравнивая их со считанным значением из регистрового файла. При обнаружении расхождения, блок восстанавливает исходное значение и выдает на выход правильные данные разрядностью I. Недостатком такой схемы является то, что значение в регистровом файле остается поврежденным, поскольку исправление ошибки в регистровом файле возможно только при его записи. Таким образом, существует вероятность того, что запись в регистр не будет происходить длительное время и возможно возникновение в нем второго сбоя, а две ошибки традиционные схемы, такие как схема защиты кодом Хемминга, исправить не в состоянии. Данное явление принято называть накоплением сбоев. Существует разные программные и аппаратные решения данной проблемы. Например, широко известен программный метод, называемый scrubbing, при котором, параллельно к выполнению основной программы, периодически запускается фоновый процесс, в котором программа обращается последовательно ко всем ячейкам регистрового файла, считывая и обратно записывая содержимое считанной ячейки, тем самым исправляя все возможные одиночные сбои (Architecture Design for Soft Errors», Mukherjee S. // Elsevier, 2008, стр.132).

Недостатком этого метода является то, что требуется серьезная модификация программного кода, что не всегда возможно.

Наиболее близким по технической сути и достигаемому результату являются способ исправления одиночных ошибок и предотвращения возникновения двойных ошибок в регистровом файле, каждый регистр которого, помимо I информационных, содержит D дополнительных разрядов, и устройство для его осуществления, содержащее регистровый файл, блок формирования корректирующих кодов и блок проверки и восстановления, с входами и выходами и связями между блоками (Патент US №7493523, кл. G06F 11/14, опублик. 1994).

В указанном патенте описана схема, отслеживающая частоту обращений и принудительно вставляющая команду обращения к регистру, к которому длительное время не было обращения. Реализация схемы предполагает введение отдельного счетчика, а также схемы его управления для каждого регистра из регистрового файла.

Недостатком описанного выше технического решения является существенное увеличение суммарной площади на кристалле, занимаемой регистровым файлом и схемой, реализующей защиту от накопления сбоев и, соответственно, повышение энергопотребления всего кристалла. Также, включение дополнительных команд в исходную последовательность инструкций приводит к изменению временной диаграммы выполнения программы, что не всегда допустимо для систем жесткого реального времени.

Техническим результатом от использования изобретения является обеспечение устойчивости схемы регистрового файла к одиночным сбоям при сохранении временной диаграммы выполнения команд при меньшей площади кристалла и меньшем энергопотреблении.

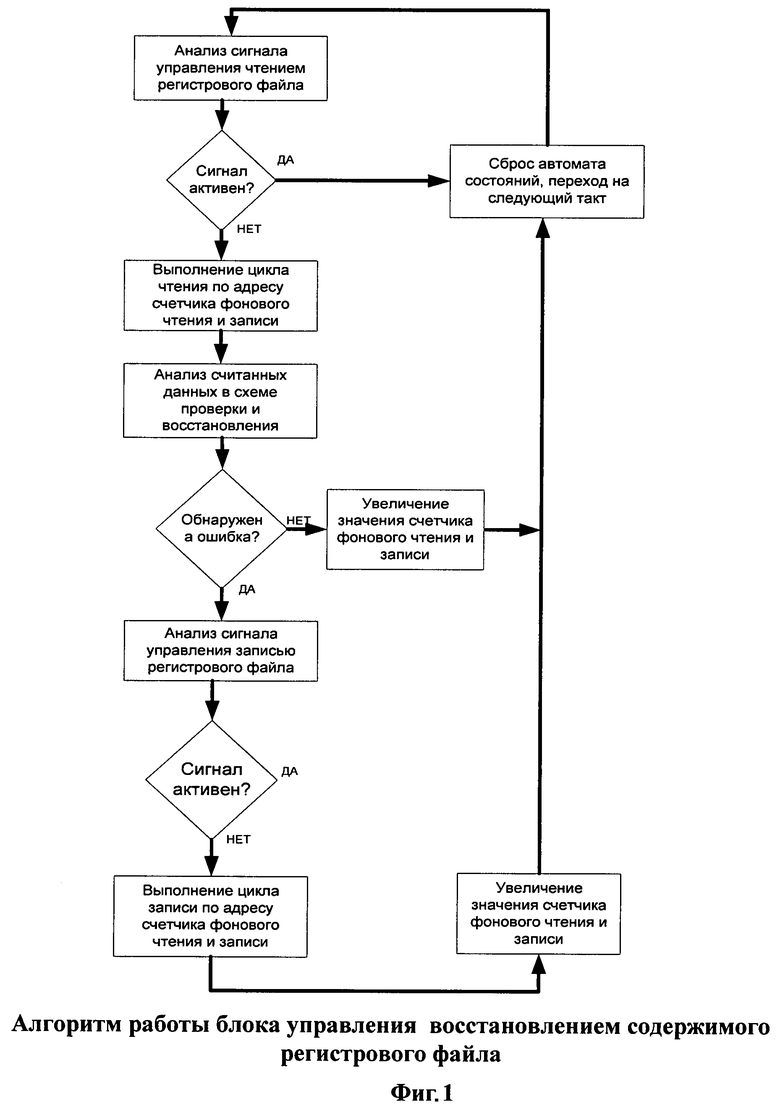

Указанный результат достигается тем, что в способе исправления одиночных ошибок и предотвращения возникновения двойных ошибок в регистровом файле, каждый регистр которого, помимо I информационных, содержит D дополнительных разрядов, в каждом такте работы процессора выполняют анализ состояния сигнала управления циклом чтения регистрового файла, и если сигнал управления циклом чтения активен, то автомат состояний блока управления восстановлением содержимого регистрового файла приводят в исходное состояние, если сигнал управления циклом чтения регистрового файла неактивен, то выполняют цикл фонового чтения, причем адрес считываемого регистра в цикле фонового чтения берут со счетчика адреса фонового чтения и записи, разрядность которого совпадает с разрядностью шины адреса регистрового файла, затем считанные данные анализируют в блоке проверки и восстановления, при этом если ошибка не обнаружена, то содержимое счетчика адреса фонового чтения и записи увеличивают на единицу и автомат состояний блока управления восстановлением содержимого регистрового файла приводят в исходное состояние, а при обнаружении ошибки анализируют сигнал управления циклом записи регистрового файла и если он активен, то автомат состояний блока управления восстановлением содержимого регистрового файла приводят в исходное состояние, а если сигнал управления циклом записи регистрового файла неактивен, то выполняют цикл фоновой записи и в регистр записывают данные, исправленные в блоке проверки и восстановления, причем адрес записываемого регистра в цикле фоновой записи берут со счетчика адреса фонового чтения и записи, после чего содержимое счетчика фонового чтения и записи увеличивают на единицу, и автомат состояний блока управления восстановлением содержимого регистрового файла приводят в исходное состояние.

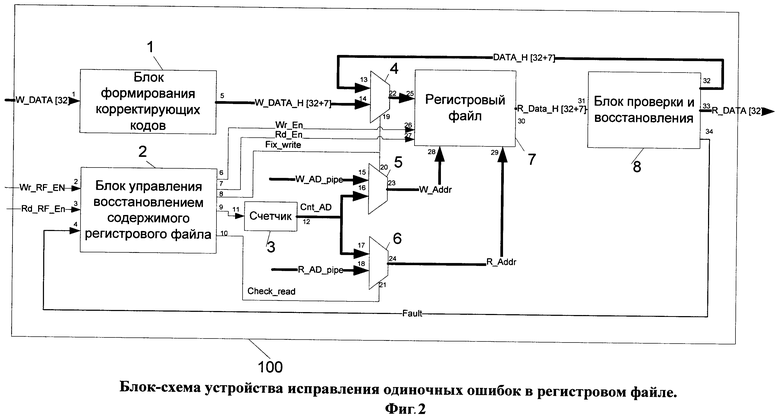

Способ реализуется устройством, содержащим регистровый файл, блок формирования корректирующих кодов, и блок проверки и восстановления, с входами и выходами и связями между блоками и дополнительно содержащим блок управления восстановлением содержимого регистрового файла, счетчик адреса фонового чтения и записи, мультиплексор данных записи, мультиплексор адреса записи, мультиплексор адреса чтения, при этом выходом блока управления восстановлением содержимого регистрового файла являются сигналы управления счетчиком фонового чтения и записи, мультиплексором данных записи, мультиплексором адреса записи, мультиплексором адреса чтения и регистровым файлом, а входом являются сигналы записи и чтения регистрового файла, поступающие из дешифратора команд ядра микропроцессора, причем счетчик адреса фонового чтения и записи имеет разрядность, совпадающую с разрядностью адреса регистрового файла, при этом мультиплексор адреса записи и мультиплексор адреса чтения имеют по две входные и по одной выходной шины, разрядность которых совпадает с разрядностью адреса регистрового файла, мультиплексор данных записи, имеет две входные и одну выходную шину, разрядность которой совпадает с разрядностью шины данных регистрового файла разрядностью I+D, выходом регистрового файла является шина данных разрядностью I+D, выходом блока проверки и восстановления является шина, разрядностью I+D, содержащая исправленные данные и подключенная к входу мультиплексора данных записи, шина, разрядностью I, содержащая информационные разряды, поступающие в конвейер микропроцессора, подключенный к выходу блока проверки и восстановления.

Изобретение поясняется чертежами, где на фиг.1 представлен алгоритм работы блока управления восстановлением содержимого регистрового файла, на фиг.2 представлена блок-схема устройства исправления одиночных ошибок в регистровом файле.

Способ исправления одиночных ошибок и предотвращения возникновения двойных ошибок в регистровом файле реализуется следующим образом. Каждый регистр регистрового файла, помимо информационных, содержит дополнительные разряды, в котором каждом такте работы процессора выполняется анализ состояния сигнала управления циклом чтения регистрового файла. Если сигнал управления циклом чтения активен, то автомат состояний блока управления восстановлением содержимого регистрового файла приводится в исходное состояние. Если сигнал управления циклом чтения неактивен, то выполняется цикл фонового чтения, причем адрес считываемого регистра в цикле фонового чтения берется со счетчика адреса фонового чтения и записи, разрядность которого совпадает с разрядностью шины адреса регистрового файла.

Данные, считанные в цикле фонового чтения, включающие информационные и дополнительные разряды, анализируются в блоке проверки и восстановления. Если блок проверки и восстановления не обнаружил ошибки, то содержимое счетчика адреса фонового чтения и записи увеличивается на единицу и автомат состояний блока управления восстановлением содержимого регистрового файла приводится в исходное состояние. Если обнаружена ошибка, то анализируется сигнал управления циклом записи регистрового файла. Если сигнал управления циклом записи регистрового файла неактивен, то выполняется цикл фоновой записи, в котором в регистр записываются данные, включающие информационные и дополнительные разряды, исправленные в блоке проверки и восстановления, причем адрес записываемого регистра в цикле фоновой записи берется со счетчика адреса фонового чтения и записи, после чего содержимое счетчика фонового чтения и записи увеличивается на единицу и автомат состояний блока управления восстановлением содержимого регистрового файла приводится в исходное состояние.

если сигнал управления циклом записи регистрового файла активен, то автомат состояний блока управления восстановлением содержимого регистрового файла приводится в исходное состояние.

Способ реализуется устройством, которое содержит следующие узлы:

1 - блок формирования корректирующих кодов,

2 - блок управления восстановлением содержимого регистрового файла,

3 - счетчик адреса фонового чтения и записи,

4 - мультиплексор данных записи,

5 - мультиплексор адреса записи,

6 - мультиплексор адреса чтения

7 - регистровый файл,

8 - блок проверки и восстановления.

1. Блок формирования корректирующих кодов 1 предназначен для формирования некоторого дополнительного числа разрядностью D на основе исходного информационного слова разрядностью I. Разрядность корректирующего дополнительного слова зависит от разрядности информационного слова и от принятого алгоритма вычисления корректирующего кода. На вход 1 блока формирования корректирующих кодов 1 подается исходное информационное слово, поступающее из конвейера микропроцессора.

2. Блок управления восстановлением содержимого регистрового файла 2 предназначен для формирования сигналов управления счетчиком 3, мультиплексорами 4. 5, 6 и регистровым файлом 7. Выходом блока 2 являются сигналы управления счетчиком фонового чтения и записи 3, мультиплексорами 4, 5, 6 и регистровым файлом 7. Входом схемы 2 являются сигналы записи и чтения регистрового файла, поступающие из дешифратора команд ядра микропроцессора. Алгоритм работы блока управления восстановлением содержимого регистрового файла показан на рис.1.

3. Счетчик адреса фонового чтения и записи 3 предназначен для формирования адреса, по которому производится фоновое считывание данных из регистрового файла 7 для проверки, а также по которому производится фоновая запись в регистровый файл 7 в случае обнаружения ошибки. Представляет собой стандартный счетчик с разрядностью, совпадающей с разрядностью адреса регистрового файла 7.

4. Мультиплексор 4 предназначен для формирования данных для цикла записи регистрового файла 7. Представляет собой стандартный мультиплексор с двумя входными и одной выходной шиной. Разрядность входных и выходных шин мультиплексора совпадает с разрядностью шины данных регистрового файла 7.

5. Мультиплексор 5 предназначен для формирования адреса цикла фоновой записи регистрового файла 7. Представляет собой стандартный мультиплексор с двумя входными и одной выходной шиной. Разрядность входных и выходных шин мультиплексора совпадает с разрядностью адреса регистрового файла 7.

6. Мультиплексор 6 предназначен для формирования адреса цикла фонового чтения регистрового файла 7. Представляет собой стандартный мультиплексор с двумя входными и одной выходной шиной. Разрядность входных и выходных шин мультиплексора совпадает с разрядностью адреса регистрового файла 7.

7. Регистровый файл 7 предназначен для хранения I информационных и D дополнительных разрядов и состоит из набора регистров общего назначения. Количество информационных разрядов каждого регистра определяется архитектурой микропроцессора и, как правило, составляет 8, 16, 32 или 64 разряда, но может принимать и другие значения. Количество дополнительных разрядов каждого регистра зависит от алгоритма вычисления корректирующего кода. Выходом регистрового файла является шина данных разрядностью I+D. Регистровый файл сможет содержать произвольное количество регистров, количество которых определят разрядность адреса чтения и записи. Наиболее распространены регистровые файлы с 16, 32, 64 регистрами (разрядность адреса = 4, 5, 6 соответственно), но возможны и другие значения количества регистров и, соответственно, другая разрядность адреса. Регистровый файл может иметь различное количество портов чтения и записи.

8. Блок проверки и восстановления 8 предназначен для проверки корректности считанных из регистрового файла 7 информационных и дополнительных данных и, в случае обнаружения одиночной ошибки, восстановления сбойного разряда. Наиболее распространенным является алгоритм проверки и восстановления кодом Хемминга, тем не менее, принцип действия устройства допускает любые другие алгоритмы проверки и восстановления. Выходом блока проверки и восстановления 8 является шина, разрядностью I+D, содержащая исправленные данные и подключенная к входу мультиплексора 4 шина разрядностью I, содержащая информационные разряды, поступающие в конвейер микропроцессора, и сигнал Fault, являющийся признаком обнаружения сбоя, подключенный к входу блока управления восстановлением содержимого регистрового файла 2. Устройство исправления одиночных ошибок и предотвращения возникновения двойных ошибок в регистровом файле 100 работает следующим образом: в начале каждого процессорного такта блок управления восстановлением содержимого регистрового файла 2 анализирует состояние сигнала управления циклом чтения регистрового файла Rd_RF_En, который формируется схемой управления конвейером микропроцессора. Если данный сигнал активен, то устройство 100 выполняет стандартный цикл чтения регистрового файла, а именно: сигнал Rd_En, поступающий с выхода 7 блока 2 на вход 27 регистрового файла 7, становится активным, сигнал управления мультиплексором Check_read, поступающий с выхода 10 блока 2 на вход 23 мультиплексора 6, имеет неактивное состояние, позволяя адресу чтения с конвейера микропроцессора R_AD_pipe попасть на вход 29 регистрового файла 7. Считанные данные R_Data_H с выхода 30 регистрового файла 7 поступают на вход 31 блока проверки и восстановления 8, в котором производится проверка и восстановление содержимого I информационных разрядов шины данных R_DATA, которые с выхода 33 блока 8 поступают в конвейер микропроцессора, после чего схема 100 переводит все сигналы в неактивное состояние и готова к началу следующего процессорного такта. Если сигнал управления циклом чтения регистрового файла Rd_RF_En имеет неактивное состояние, то схема 100 начинает цикл фонового чтения, в котором сигнал Rd_En, поступающий с выхода 7 блока 2 на вход 27 регистрового файла 7, становится активным, сигнал управления мультиплексором Check_read, поступающий с выхода 10 блока 2 на вход 23 мультиплексора 6, принимает неактивное состояние, позволяя адресу фонового чтения и записи Cnt_AD с выхода счетчика 3 попасть на вход 29 регистрового файла 7. Считанные данные R_Data_H разрядностью I+D с выхода 30 регистрового файла 7 поступают на вход 31 блока проверки и восстановления 8, в котором производится проверка содержимого разрядов шины R_Data_H.

Если блок проверки и восстановления 8 не обнаружил ошибки в данных на шине R_Data_H, то сигнал Fault, поступающий с выхода 34 блока 8 на вход 4 блока 2, имеет неактивное состояние и блок 2 переводит сигнал на выходе 9, поступающий на вход 11 счетчика 3, в активное состояние до окончания текущего такта, при этом счетчик 3 увеличивает свое значение на 1, после чего схема 100 переводит все сигналы в неактивное состояние и готова к началу следующего процессорного такта.

Если блок проверки и восстановления 8 обнаружил ошибку в данных на шине R_Data_H, то сигнал Fault, поступающий с выхода 34 блока 8 на вход 4 блока 2, переходит в активное состояние. Блок 2, обнаружив на входе 4 активный уровень сигнала Fault, анализирует состояние сигнала управления циклом записи регистрового файла Wr_RF_EN, поступающего на вход 2, который формируется схемой управления конвейером микропроцессора.

Если данный сигнал активен, то схема 100 выполняет стандартный цикл записи регистрового файла, а именно: сигнал Wr_En, поступающий с выхода 6 блока 2 на вход 26 регистрового файла 7, становится активным, информационные разряды I на шине данных W_DATA, подаваемые на вход 1 блока формирования корректирующих кодов из конвейера микропроцессора, дополняются корректирующими разрядами D, формируя на выходе 5 блока 1 данные разрядностью I+D на шине W_DATA_H, сигнал управления мультиплексором Fix_write, поступающий с выхода 8 блока 2 на вход 19 мультиплексора 4 и на вход 20 мультиплексора 5 имеет неактивное состояние, позволяя адресу записи с конвейера микропроцессора W_AD_pipe попасть на вход 28 регистрового файла 7, а данным на шине W_DATA_H с выхода 5 блока 1 попасть на вход 25 регистрового файла 7, после чего схема 100 переводит все сигналы в неактивное состояние и готова к началу следующего процессорного такта.

Если сигнал Wr_RF_EN неактивен, то схема 100 начинает цикл фоновой записи, при котором сигнал Wr_En, поступающий с выхода 6 блока 2 на вход 26 регистрового файла 7, становится активным, сигнал управления мультиплексором Fix_write, поступающий с выхода 8 блока 2 на вход 19 мультиплексора 4 и на вход 20 мультиплексора 5 принимает активное состояние, позволяя адресу фонового чтения и записи Cnt_AD с выхода счетчика 3 попасть на вход 28 регистрового файла 7, а исправленным данным на шине DATA_H разрядностью I+D с выхода 32 блока проверки и восстановления 8 попасть на вход 25 регистрового файла 7. Результатом данного цикла фоновой записи станет исправление поврежденного слова данных в регистровом файле 7. По завершении указанных действий блок 2 переводит сигнал на выходе 9, поступающий на вход 11 счетчика 3, в активное состояние, при этом счетчик 3 увеличивает свое значение на 1, после чего схема 100 переводит все сигналы в неактивное состояние и готова к началу следующего.

Описанные выше способ и устройство позволяют обеспечить устойчивость схемы регистрового файла к одиночным сбоям при сохранении временной диаграммы выполнения команд при меньшей площади кристалла и меньшем энергопотреблении.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1985 |

|

SU1274006A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Микропроцессорное устройство управления лучом плоской антенной решетки | 1984 |

|

SU1206797A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1829038A1 |

Изобретение относится к области телемеханики, автоматики и вычислительной техники и предназначено для обработки данных и исправления одиночных сбоев в регистровых файлах микропроцессоров. Техническим результатом является обеспечение устойчивости схемы регистрового файла к одиночным сбоям при сохранении временной диаграммы выполнения команд при меньшей площади кристалла и меньшем энергопотреблении. Устройство содержит регистровый файл, блок формирования корректирующих кодов и блок проверки и восстановления, блок управления восстановлением содержимого регистрового файла, счетчик адреса фонового чтения и записи, мультиплексор данных записи, мультиплексор адреса записи, мультиплексор адреса чтения. Способ описывает работу устройства. 2 н.п. ф-лы, 2 ил.

1. Способ исправления одиночных ошибок и предотвращения возникновения двойных ошибок в регистровом фале, каждый регистр которого, помимо I информационных, содержит D дополнительных разрядов, отличающийся тем, что в каждом такте работы процессора выполняют анализ состояния сигнала управления циклом чтения регистрового файла, и если сигнал управления циклом чтения активен, то автомат состояний блока управления восстановлением содержимого регистрового файла приводят в исходное состояние, если сигнал управления циклом чтения регистрового файла неактивен, то выполняют цикл фонового чтения, причем адрес считываемого регистра в цикле фонового чтения берут со счетчика адреса фонового чтения и записи, разрядность которого совпадает с разрядностью шины адреса регистрового файла, затем считанные данные анализируют в блоке проверки и восстановления, при этом, если ошибка не обнаружена, то содержимое счетчика адреса фонового чтения и записи увеличивают на единицу и автомат состояний блока управления восстановлением содержимого регистрового файла приводят в исходное состояние, а при обнаружении ошибки анализируют сигнал управления циклом записи регистрового файла, и, если он активен, то автомат состояний блока управления восстановлением содержимого регистрового файла приводят в исходное состояние, а если сигнал управления циклом записи регистрового файла неактивен, то выполняют цикл фоновой записи и в регистр записывают данные, исправленные в блоке проверки и восстановления, причем адрес записываемого регистра в цикле фоновой записи берут со счетчика адреса фонового чтения и записи, после чего содержимое счетчика фонового чтения и записи увеличивают на единицу, и автомат состояний блока управления восстановлением содержимого регистрового файла приводят в исходное состояние.

2. Устройство для осуществления способа по п.1, содержащее регистровый файл, блок формирования корректирующих кодов, и блок проверки и восстановления, с входами и выходами и связями между блоками, отличающееся тем, что устройство дополнительно содержит блок управления восстановлением содержимого регистрового файла, счетчик адреса фонового чтения и записи, мультиплексор данных записи, мультиплексор адреса записи, мультиплексор адреса чтения, при этом выходом блока управления восстановлением содержимого регистрового файла являются сигналы управления счетчиком фонового чтения и записи, мультиплексором данных записи, мультиплексором адреса записи, мультиплексором адреса чтения и регистровым файлом, а входом являются сигналы записи и чтения регистрового файла, поступающие из дешифратора команд ядра микропроцессора, причем счетчик адреса фонового чтения и записи имеет разрядность, совпадающую с разрядностью адреса регистрового файла, при этом мультиплексор адреса записи и мультиплексор адреса чтения имеют по две входные и по одной выходной шины, разрядность которых совпадает с разрядностью адреса регистрового файла, мультиплексор данных записи имеет две входные и одну выходную шины, разрядность которой совпадает с разрядностью шины данных регистрового файла разрядностью I+D, выходом регистрового файла является шина данных разрядностью I+D, выходом блока проверки и восстановления является шина разрядностью I+D, содержащая исправленные данные и подключенная к входу мультиплексора данных записи, шина разрядностью I, содержащая информационные разряды, поступающие в конвейер микропроцессора, подключенный к выходу блока проверки и восстановления.

| US 7493523 В2, 17.02.2009 | |||

| US 7083092 В2, 01.08.2006 | |||

| СПОСОБ ИНТЕЛЛЕКТУАЛЬНО-АДАПТИВНОЙ ШИРОТНО-ИМПУЛЬСНОЙ ЗАПИСИ ЦИФРОВОЙ ИНФОРМАЦИИ | 2006 |

|

RU2302667C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2008 |

|

RU2384899C2 |

Авторы

Даты

2012-10-27—Публикация

2011-09-02—Подача