СО

ел к

QD

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1159165A1 |

| Преобразователь параллельного кода в последовательный | 1983 |

|

SU1119002A1 |

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1243098A1 |

| Медианный фильтр | 1988 |

|

SU1562902A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1547076A1 |

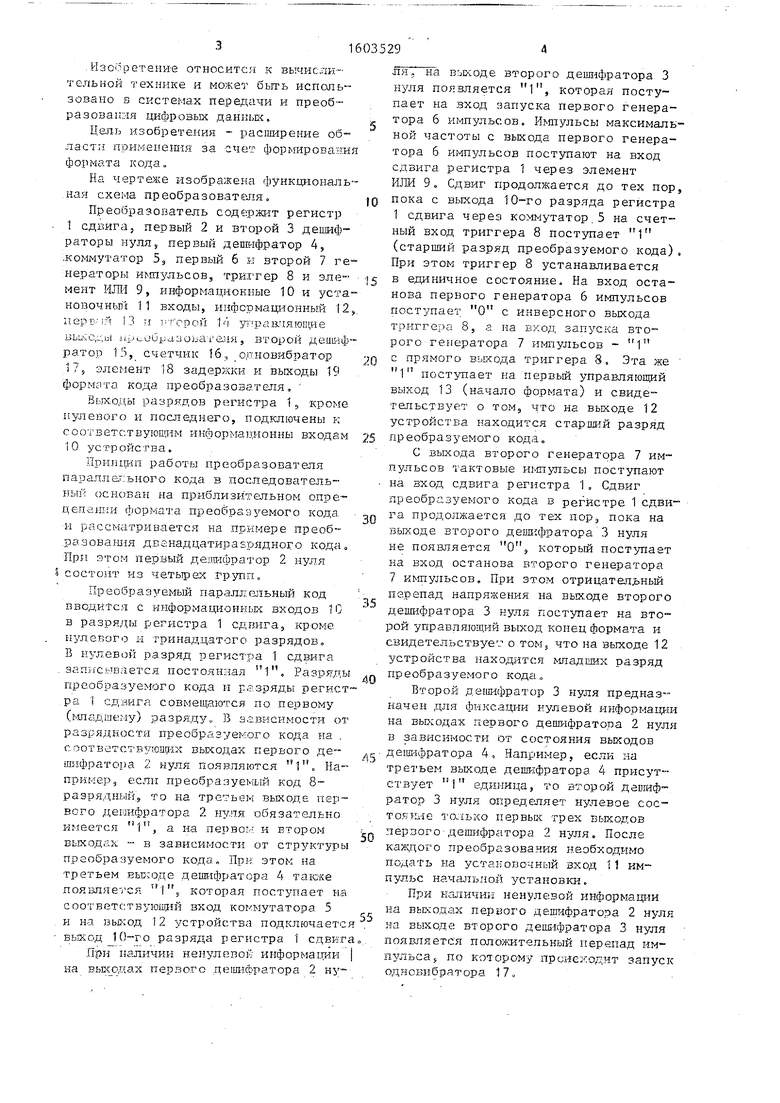

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и преобразования цифровых данных. Цель изобретения - расширение области применения за счет формирования формата кода. Преобразователь содержит регистр 1 сдвига, первый 2 и второй 3 дешифраторы нуля, первый дешифратор 4, коммутатор 5, первый 6 и второй 7 генераторы импульсов, триггер 8 и элемент ИЛИ 9, информационные 10 и установочные 11 входы, информационный 12, первый управляющий 13 и второй управляющий 14 выходы преобразователя, второй дешифратор 15, счетчик 16, одновибратор 17, элемент задержки 18, выходы 19 формата кода преобразователя. 1 ил.

ГО

Изобретение относится к вычислительной технике и может быть испань- зоваио Б системах передггчи и преоб- разозаиня цифровых данных,

Цеаь изобретения - расширение области npHMenei-nijf за счет фop fflpoвaпия формата кода,

На чертеже изображена функциональная схема преобразователя

Преобразователь содержит регистр 1 сдвига, первый 2 и второй 3 дешифраторы нуля, первый дешифратор 4, .коммутатор 5s первый б к второй 7 генераторы импульсовэ триггер 8 и эле- мент ИЛИ 9, информационнрле 10 и уста- но}зочньш 11 входы, информационный 12,. первмй 3 и гт срой 14 у; рааця1опре ,L:,bi .iLie.uOpa3OJja i e,iiHJ второй ратор 13, счетчик 16,, одновибратор 1/S элемент 18 задержки и выходы 19 формата кода преобразо}зателя,

Вькоды разрядов регистра 1, кроме пулевого и последнего, подключены к соо1 ветствуюпгим информационны входам 10 устройства.

При.шшп работы преобразоватачя паралле-:ьного кода в последовательный основан на приблизительном опре- цепелши формата преобразуемого кода, и рассматривается на примере преоб- ра.зоварл1я двенадцатиразр щного кода. При этом первый деинфратор 2 нуля состоит из четырех групп.

Преобразуемый параллельный код вводится с информационньБ-j входов 10 в разряды регистра 1 сдвига, кроме нулевого н тринадцатого разрядов В нулевой разряд регистра 1 сдвига запис.ывяется постоянная 1, Разряды преобразуемого кода и разряды регистра 1 сдвига совмещаются по первому (tdnaA.uje.-.iy) разряду. В зависимости от разрядности преобразуемого кода на соответствуюищх выходах первого дешифратора 2 нуля гшяв.пяются Г „ Например, если преобразуемый код 8 разрядный, то на третьем выходе первого дешифр атора 2 нуля обязательно имеется 1, а па первом и втором выходах в зависимости от стрз ктут Ы преобразуемого кода. При: этом на третьем вькоде дешифратора 4 таюке появляется 1, которая поступает на соответс;твующий вход ког/мутатора 5 и на вькод 12 устройства подключается выход JO-ro разряда регистра 1 сдвига

При наличии ненулевой информа.т.тии | на первого деишфратора 2 ну10

0

5

ля. на выходе второго деш1фратора 3 нуля появляется 1, которая поступает на .вход запуска первого генератора б импульсов. Иьшульсы максимальной частоты с выхода первого генератора б импульсов поступают на вход сдвига регистра 1 через элемент ИЛИ 9„ Сдвиг продолжается до тех пор, пока с выхода 10-го разряда регистра 1 сдвига через коммутатор,5 на счетный вход триггера 8 поступает 1 (старший разряд преобразуемого кода). При этом триггер 8 устанавливается в единичное состояние. На вход останова первого генератора 6 импульсов поступает О с инверсного выхода триггера 8, а на вход зап-уска второго генератора 7 импульсов - 1 с прямого выхода триггера 8. Эта же 1 поступает на первый управляющий выход 13 (начало формата) и свидетельствует о том, что на выходе 12 устройства находится старший разряд .г реобразуемого кода.

С выхода второго генератора 7 им- пзшьсов тактовые ш шульсы поступают на вход сдвига регистра 1 Сдвиг преобразуемого кода в регистре 1 сдвига продолжается до тех пор, пока на вькоде второго деш1фратора 3 нуля не появляется О, который поступает на вход останова второго генератора 7 и шyльcoв, При этом отри цат ел)Ный перепад напряжения на вькоде второго дешифратора 3 нуля поступает на второй управляющий выход конец формата и свидетельствуе .: о том, что на выходе 12 устройства находится младших разряд преобразуемого кода.

Второй деЕшфратор 3 нуля предназначен для фиксации нулевой информации на вькодах первого дешифратора 2 нуля в зависимости от состояния выходов дешифратора 4 о Например, если на

третьем выходе дешифратора 4 присутствует i единица, то второй депгяф- ратор 3 нуля определяет нулевое сос- тоякие то.1ько первьк трех выходов первого дешифратора 2 нуля. После каж,цого преобразования необходргмо подать на установочный вход I1 импульс нач;шьиой установки.

При нгишчии ненулевой информации на вькодах первого дешифратора 2 нуля на выходе второго деаифратора 3 нуля появляется пололштепьный перепад импульса s по которому происходит запуск одновибратора 17,

0

5

0

0

5

На вькоде второг о дешифратора 15 формируется двоичный код числа 3, 6, 9 и 12, если присутствует единичный сигнал на его первом, второй, третьем или четвертом входе соответственно.

Таким образом, после записи преобразуемого кода в регистр 1, в счетчик 16 импульса записывается приблизительное значение формата преобразуемого кода.

Импульсы максимальной частоты с выхода первого генератора 6 импульсов также поступают на вход обратного счета счетчика 16. Обратный счет продолжается до тех пор, пока с выхода 10-FO разряда регистра 1 сдвига (для данного случая) через коммутатор 5 на счетный вход триггера 8 поступает 1,

16

Таким образом, при появлении на выходе 12 старшего разряда преобразуемого кода- 1, на группе выходов ,19 преобразователя находится код

действительного значения формата преобразуемого кода. Элемент задержки 18 обеспечивает устранение эффекта

м

1603529

0

5

0

5

гонок при различных синхронизациях работы счетчика 16 импульсов.

Формула изобретения

Преобразователь параллельного кода в последовательный по авт.св. , № 1243098, отличающий,ся тем, что, с целью расширения области применения за счет формирования формата кода, в него введены одновибра- тор, элемент задержки, счетчик и второй дешифратор, входы которого объединены с одноименнЕ 1ми входами первого дешифратора, выходы второго де- . пшфратора соединены с соответствую- . щнми информационными входами счетчика, выходы которого являются выходом формата кода преобразователя, вход и выход элемента задержки подключены соответственно к выходу первого генератора импульсов и входу обратного счета счетчика, вход и выход одновибратора подключены соответственно к выходу второго дешифратора нуля.и входу параллельной записи счетчика.

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1243098A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-10-30—Публикация

1988-04-26—Подача