оэ

05 00

Изобретение относится к вычислительной TGXHirKB и может быть использовано в качестве оперативной памяти.

Цель изобретения - повышение быстродействия устройства.

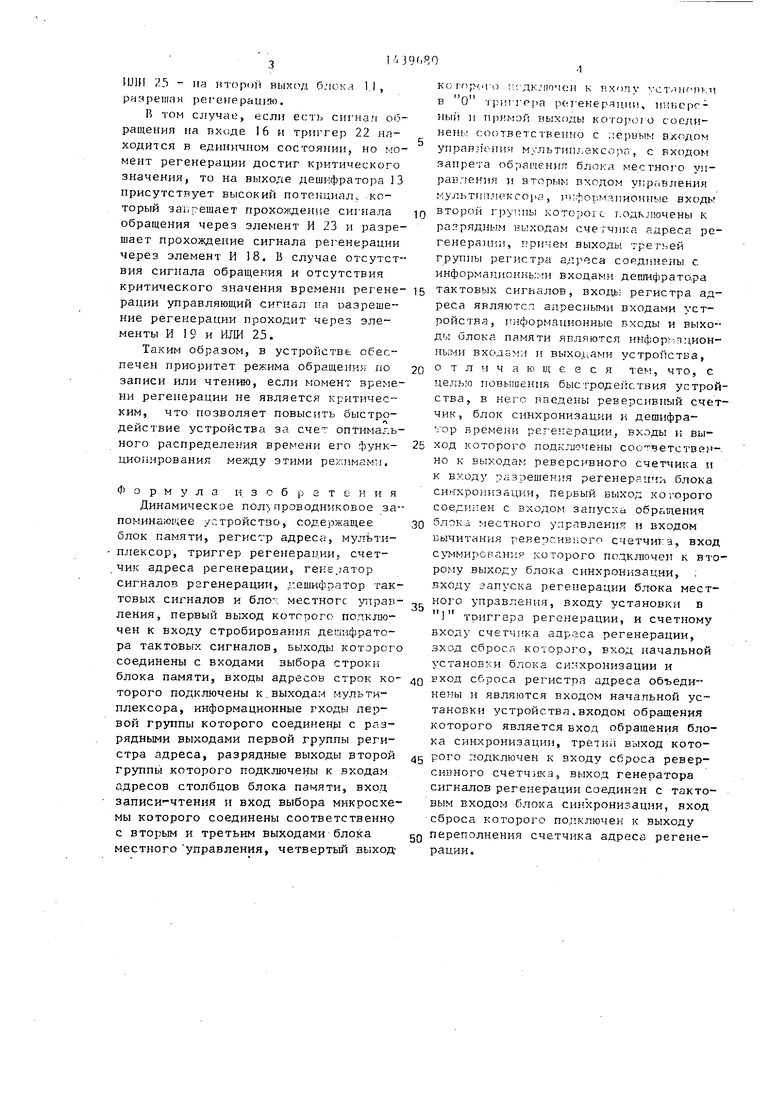

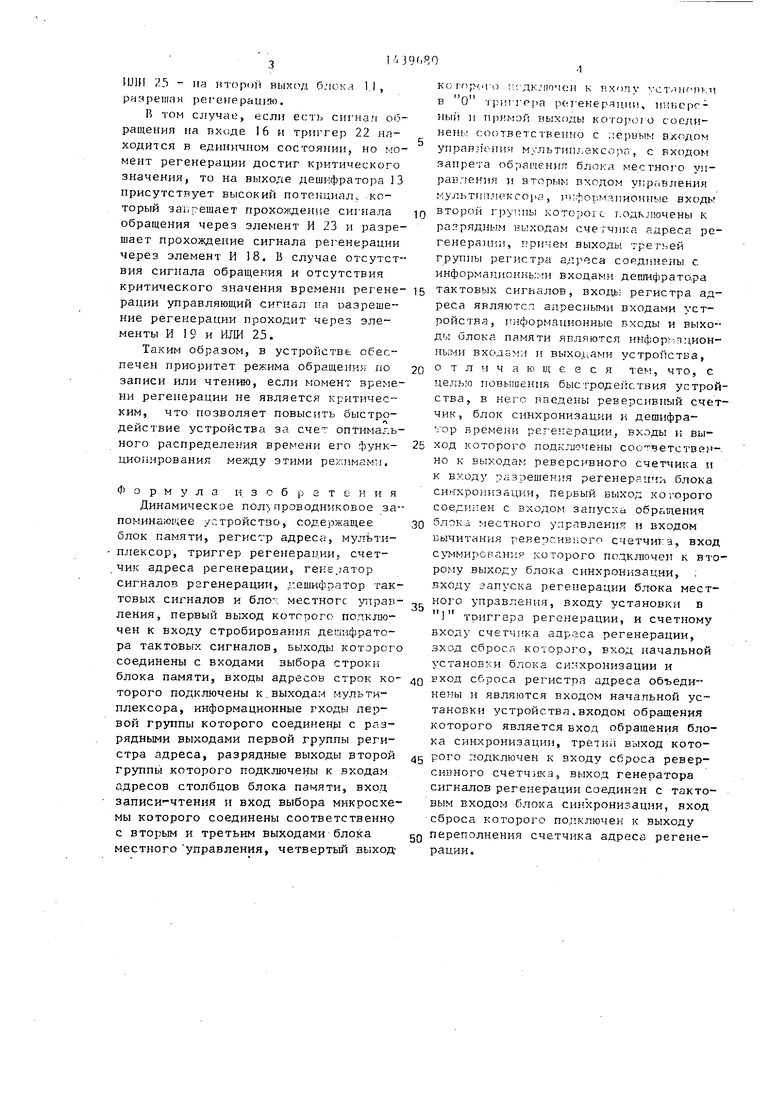

Па фиг,1 изображена функциональная схема нредлагаемого устройства; на фиг.2 - функциональная схема блока синхронизации.

Устройство содержит (фиг.1) регистр 1 адреса, адресные входы 2, мультиплексор 3, триггер Д регенерации, счетчик 5 адреса регенерации, блок 6 местного управления, дешифратор 7 тактовых сигналов, блок 8 памяти, информационные входы 9 и выхо- , ды 10, блок J синхронизации, ревер- С1ШНЫЙ счетчик 12, дешифратор 13 вреВ случае, когда на счетчике 5 находится очередной адрес регенерации, на счетчике 12 находится число п (п - целое число) циклов регенерации, проведенных в течение времени с начала текуш,его периода регенерации, за вычетом числа m (m обращений к блоку времени, т.е. число чика 12 равно , так как на сумми- рутощий вход счетчика 12 поступают сигналь разрешения регенерации, а на вычитающий вход - сигнал разрешемени регенерации, генератор J4 сигна- 20 „„я обращения к блоку 8 соответствец- JLOB регенерации, вход 15 начальной

но с второго и первого выходов блока 11. Если приход1 т некоторьй адрес 1 на обращение, то он устанавливается на регистре 1, с Б(1ходов которого на дешифратор 7 подаются управляющие потенциалы для считывания или записи информации. Одновременно поступает сигнал обращения на вход 16 блока 11, KOTOpbifi устанавливает триггер 22 в единичное С(. стояние, При этом если содержимое счетчика 2 не является кр1 тическям, то на выходе дешифратора J3 появляется гизкий потенциал, который 1, оступает на элемент НЕ 17 и га один мс. входов элемента И 18, за счет чего выходной сигнал с генератора JA, пройдя элемент 20 задер;- жи, не проходит через элемент И S8 и г лемент И JO, закрытый сигналом с выхода триггера 22, и далее через элемен л МЛИ 25 - на второй выход блока 11, т.е. режим регенерации оказьюается запрещенным. Поэтому второй сигнал с выхода эле- :eнтa 20 задержки поступает на второй вход элемента И 23 и проходит через первый выход блока 1J к блоку 6 и на вход счетчика 12. уменьшая на дииицу число на его выходах. Этот же сигнал проходит на ЕХОД триггера 22 через элемент ИЛИ 24, сбрасывая триггер 22 в нулевое состоянир-. Элемент 20 задержки предотвращает переходные процессы при смене режимов при асинхронном появлении сигналов. обращения. Следующий сиг-нал с генератора iA, если нет сиптала обращения на входе 6, постунае / черрз мент И 19 и далее через элемент

установки и вход J6 обращения.

Блок 11 синхронизации содержит (фиг.2) элемент НЕ 17, элементы И 18 и J9, Элемент 20 задержки, элемент linii 2-1, триггер 22, элемент И 23 и элементы ИЛИ 24 и 25.

Блок 3 памяти может построен из запоминающих элементов памяти, например, типа К565 РУ I.

Блок 6 местного управления может быть выполнен, например, аналог ично серийно выпускаемому модулю управления М-2К U3.0J КЛЗ.

Устройство работает следующим об- разом.

Устройство работает в трех режимах: записи, чтения и регенерации.

Любое обращение к строке накопи- таля блока 8 вызывает регенерацию во всех запоминающих элементах, подклю- ченных при вмборе строки к усилителям считывания столбцов (не показаны) Слока 8. Кроме того, в течение периода регенерации необходимо провести циклы регенерации с целью предотвращения искажения или потери информации. Предлагаемое устройство позволяет организовать асинхронный режим регенерации, отдавая приоритет режи- му записи или считьшанил если момент Бремени регенерации по другим адресам не. является критическим, В пределах требований надежного хранения информации.

Перед началом работЕ 1 на вход J5 (фиг.1) поступает сигнал начальной установки, в результате чего триг- г ер 22 (фиг,2) устанавливается в О,

0

5

Блок 6 формирует сигналы вь борн микросхе пз1, режимов записи или чте- НИН, стробирования дешифратора 7 и установки в О триггера 4,

В случае, когда на счетчике 5 находится очередной адрес регенерации, на счетчике 12 находится число п (п - целое число) циклов регенерации, проведенных в течение времени с начала текуш,его периода регенерации, за вычетом числа m (m обращений к блоку времени, т.е. число чика 12 равно , так как на сумми- рутощий вход счетчика 12 поступают сигналь разрешения регенерации, а на вычитающий вход - сигнал разрешецелое число) в течение этого на выходе.,счет0 „„я обращения к блоку 8 соответствец-

0 „„я обращения к блоку 8 соответствец-

5

0

5

0 5 0

5

но с второго и первого выходов блока 11. Если приход1 т некоторьй адрес 1 на обращение, то он устанавливается на регистре 1, с Б(1ходов которого на дешифратор 7 подаются управляющие потенциалы для считывания или записи информации. Одновременно поступает сигнал обращения на вход 16 блока 11, KOTOpbifi устанавливает триггер 22 в единичное С(. стояние, При этом, если содержимое счетчика 2 не является кр1 тическям, то на выходе дешифратора J3 появляется гизкий потенциал, который 1, оступает на элемент НЕ 17 и га один мс. входов элемента И 18, за счет чего выходной сигнал с генератора JA, пройдя элемент 20 задер;- жи, не проходит через элемент И S8 и г лемент И JO, закрытый сигналом с выхода триггера 22, и далее через элемен л МЛИ 25 - на второй выход блока 11, т.е. режим регенерации оказьюается запрещенным. Поэтому второй сигнал с выхода эле- :eнтa 20 задержки поступает на второй вход элемента И 23 и проходит через первый выход блока 1J к блоку 6 и на вход счетчика 12. уменьшая на дииицу число на его выходах. Этот же сигнал проходит на ЕХОД триггера 22 через элемент ИЛИ 24, сбрасывая триггер 22 в нулевое состоянир-. Элемент 20 задержки предотвращает переходные процессы при смене режимов при асинхронном появлении сигналов. обращения. Следующий сиг-нал с генератора iA, если нет сиптала обращения на входе 6, постунае / черрз мент И 19 и далее через элемент

или ; 5 - па iiTopoii BbixcvJ. блока 1.1 , раз ре Ilia и ре г е рай 1Ж.

В том случае, если есть сш нал обращения на входе 16 и триггер 22 находится в единичном состоянии, но момент регенерации достиг критического значения, то на выходе дешифратора 3 присутствует высокий потенциал, который запрещает Г1рохо){сден1-;е сигнала обращения через элемент И 23 и разрешает прохождение сигнала регенерации через элемент И 18, В случае отсутствия сигнала обращения и отсутствия критического значения времени регенерации управляющий сигнал па разрешение регенерации проходит через элементы И 19 и ИЛИ 25.

Таким образом, в устройстве обеспечен приоритет режима обращения по записи или чтению, если момент времени регенерации не является критическим, что позволяет повысить быстродействие устройства за оптимального распределения времени его функционирования мбйсду этими режимами,

Формула изобретения

Динамическое полупроводниковое запоминающее устройство, содержащее блок памяти, регистр адреса, мулътиплексор, триггер регенерации, счетчик адреса регенерации, геие.атор сигналов рггенерации, дешифратор тактовых сигналов и бло ч местного управления, первый выход которого подключен к входу стробирования деиг фрато- ра тактовых сигналов, выходы которого соединены с входами выбора строки блока памяти, входы адресов строк которого подключены к,выходам мультиплексора, информационные гходы первой группы которого соединен(11 с разрядными выходами первой группы регистра адреса, разрядные выходы второй группы которого подключены к входам адресов столбцов блока памяти, вход

записи -чтения и вход выбора микросхемы которого соединены соответственна с вторым и третьим выходами блока местного управления, четвертый выходке-rf pcirrj IC ДК.ЧЮ ИМ К ПХПЛу .СТ ПППКИ

в о i-pHiTPiia регенерчции, иинерс- Hbiii и прямой выходы KOTOJHM о сосди- непь: с;о()тветственно с лерным входом управ.п епии мультип.пе.ксора, с входом запрета об7-1а1иен}гя блока местного управления и Бторыь входом упр;1влекия мульт;-;плексора, ииформапионные входы

Q второй Г)у1ты которого i:OAKjrro4eHbi к ра- рядным выходам счегчика адреса регенерации, причем выходы третьей группы регистра адреса соединегты с информациоикь;ми входами дешифрато-ра

5 тактовых сигналов, входь; регистра адреса являются адресными входами устройства, информационные входы и выходы блока памяти являются инфорь-пцион- входами и выхо,и,ями устройства,

Q о т л и ч а ю щ е е с я теь , что, с цел,ью повь1шения быстродействия устройства, в неге лведены реверсивный счетчик, блок синхронизацр5и и дешифратор времени регенерации, входы и вы5 ход которого подключены соответстве -. но к выходам реверсивного счетчика и к входу разрешен Я регенерац ;- блока синхронизации, первый выход которого соединен с входом запуска обрг пения

Q блока местного управления и входом вычитания реверс.ивг.ого счетчика, вход суммирования которого no.n;KjD04eH к второму выходу блока синхронизации, ; входу запуска регенерации блока местного управления, входу установки в j триггера регенерации, и счетному входу счетчика адреса регенерации, вход сброса которого, вход начальной установки блока синхронизации и

Q вход сброса регистра адреса объединены и являются входом начальной установки устройства.входом обращения которого является вход обращения блока синхронизации, трети;: выход кото5 рого подключен к входу сброса реверсивного счетчика, выход генератора сигналов регенерации соедиизн с тактовым входом блока синхронизации, вход сброса которого подключен к выходу

Q переполнения счетчика адреса регенерации.

5

Фие.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1534509A2 |

| Устройство для регенерации динамической памяти | 1987 |

|

SU1434497A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Динамическое запоминающее устройство | 1982 |

|

SU1065886A1 |

| Запоминающее устройство | 1977 |

|

SU691925A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для управления памятью | 1984 |

|

SU1236489A1 |

Изобретение относится к ьычис- лительной технике и можат быть использовано в качестве оперативней па мяти. Целью изобретения является повышение быстродействия устройства, i c тройств о содержит регистр J адреса, мультиплексор 3, триггер 4 регенерации, счетчик 5 адреса регенерации, блок 6 местного управления, дешифратор 7 тактовых сигналов, блок 8 памяти, блок 11 синхронизации, ревер- сийный счетчик 12, дешифратор 13 времени регенерации, генератор 14 сигналов регенерации. В устройстве обеспечивается aciiHxpoHHbrii режим регенерации, причем приоритет отдается режиму записи или чте}гия если момент времени регенерации по другим адресам ке является критическим, что позволяет повысить быстродействие устройства за.счет оптимального распределения времени функционирования устройства между режимами pereaepaiqiH -и обращения по записи илл чтению. 2 ил. &

| Патент США № 4558335, кл | |||

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

| Полупроводниковые запоминаг- щие .устройства и их применение./ Под ред.А.Ю.Гордонова.-М.; Радио и связь, 1981, с.130-139, рис.3.24. | |||

Авторы

Даты

1988-11-23—Публикация

1987-02-10—Подача