(54) ЦИФРОВОЕ УСТРОЙСТВО ОГРАНИЧЕНИЯ ЧИСЛА ПО МОДУЛЮ

разряды регистра ограничителя и регистра операнда подключены соответственно к первым и вторым входам первого блока анализа знаков и блока коррекции 2.

Недостатком известного устройства является низкое быстродействие.

Целью изобретения является увеличение быстродействия устройства

Цель достигается тем, что в устройство введены второй преобразователь кодов и второй блок анализа знаков, входы которого соединены соответственно со знаковыми разрядами регистра операнда и регистра результата, а выход второго блока анализа знаков через первый блок анализа знаков соединен с управляющим входом второго преобразователя кода, информационные входы .которого соединены с выходами регистра операнда, а выходы его - со вторыми входами сумматора.

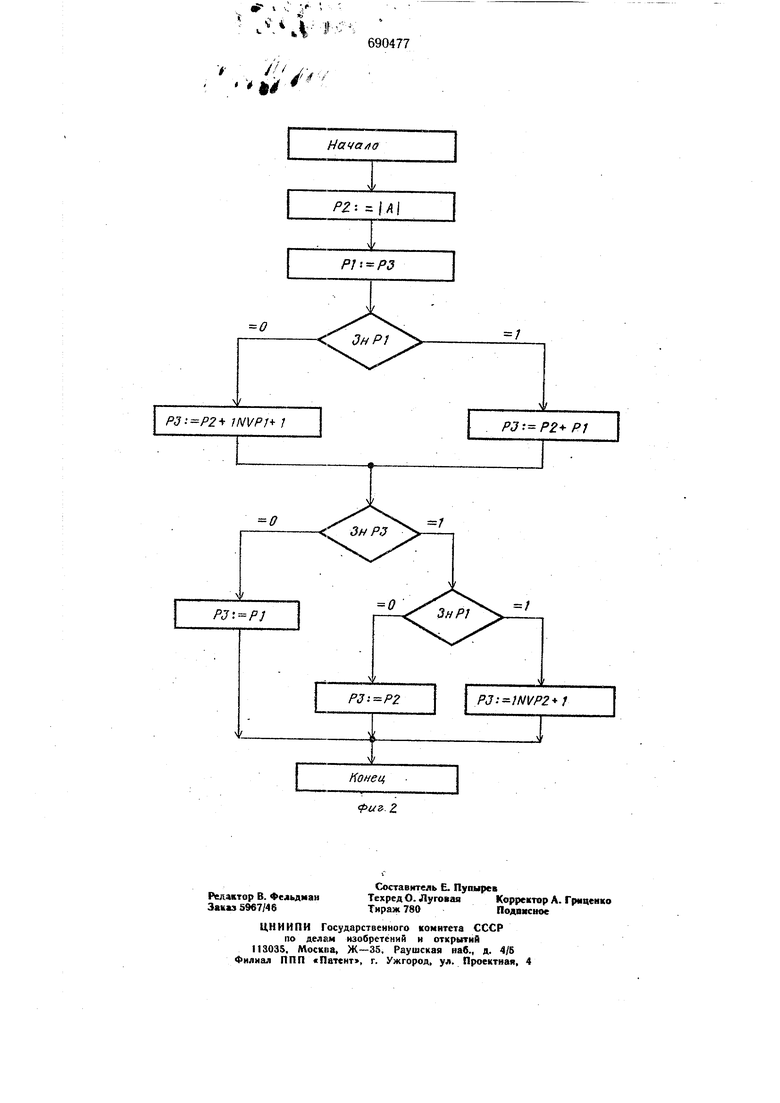

На фиг. 1 дана структурная схема устройства ограничения числа по модулю; на фиг. 2 - блок-программа работы устройства.

Устройство содержит регистр 1 операнда, регистр 2 ограничителя, регистр 3 результата сумматор 4, первый преобразователь кодов 5 первый блок 6 анализа знаков, блок 7 коррекции, группу элементов И 8 прямой передачи кодов, группу элементов И 9 передачи кодов со сдвигом влево, группу элементов .ИЛИ 10, элемент И II, второй преобразователь кодов 12, второй блок 13 анализа знаков.

Устройство работает следующим образом.

Ограничиваемое Число заносится в ре. гистр 3, оно же может быть результатом предыдущей операции. Модуль ограничителя заносится в регистр 2.

Числа складываются положительными, если их знаковые разряды находятся в состоянии нуля, и отрицательными, если - в состоянии единицы.

При подаче первого синхроимпульса ограничиваемое число переписывается из регистра 3 в регистр 1. Для определения большего по модулю из числа подготовленных в регистрах I и 2 на вход первого слагаемого сумматора 4 через группу элементов И 8 прямо.й передачи преобразователя кодов 5 поступает содержимое регистра 2. На вход второго слагаемого сумматора 4 через преобразователь кодов 12 поступает содержимое регистра 1 в прямом коде, если оно отрицательно или в обратном коде, если оно положительно. Анализ знаков в случае ведется первым блоком 6, он же выбирает соответствующие сигналы, управляющие работой преобразователей 5 и 12.

В случае подачи на первый или второй входы сумматора обратного (инверсного) кода одного из слагаемых в цепь переноса млад)иего разряда сумматора 4 с блока коррекции 7 в такте суммирования этих

690477

чисел поступает единица. Анализ знака содержимого регистра 1 осуществляется вторым блоком 13 анализа знаков, который является дополнительным к первому, блоку 6 анализа знаков.

J Оба блока анализа знаков представляют собой набор элементов И, ИЛИ, вырабатывающих управляющие сигналы для управления преобразователями кодов 5 и 12.

Результат вычитания модулей содержимого регистра 2 и perHCTpjf 1 запись1вается через группу элементов И 8 прямой передачи кодов и группу элемет-сж ИЛИ 10 в регистр 3.

Новое значение регистра 3 анализируется по знаку результата вторым блоком 13. Если . знак результата положительный, то модуль содержимого регистра 2 (ограничитель) при вычитании был больше, если знак отрицательный, то меньше.

В первом случае, если знак содержимого регистра положительный, в следующем такте ZO Иа вход первого слагаемого поступает О, на вход второго слагаемого через вентили прямой передачи преобразователя кодов 12, поступает содержимое регистра 1, т. е. происходит сложение с нулями содержимого регистра 1, или переписьего (ограничиваемого числа) в регистр 3.

Во втором случае, если знак содержимого, регистра 3 отрицательный (фиг. 2), в следующем такте на вход слагаемого сумматора 4 через вентили прямой передачи кода- преобразователя кодов 5 поступает содержимое регистра 2, если знак ограничиваемого числа регистра операнда положительный или инверсия содержимого регистра ограничителя 2 с прибавлением единицы с блока коррекции 11 на вход младшего разряда сумматора если знак ограничителя отрицательный.

На вход второго слагаемого сумматора 4 поступает 0. Результат с сумматора переписывается через группы элементов И 8 и ИЛИ 10 в регистр 3.

Таким образом, на регистре 3 в результате операции ограничения фиксируется значение ограничиваемого числа, если модуль его меньше модуля ограничителя, или ограничителя, если его модуль меньше.

Быстродействие предложенного устройства ограниче1Ийя определяется по максимальному циклу операции (фиг. 2) и равно Т 2ir,

so где -время короткой операции типа сложения в ЦВМ.

Для проведения этой бперации Иа известном устройстве путем деления ограничиваемого числа на ограничитель и анализа li результата, а затем выбора меньшего из них с помощьюлогической обработки резул)1тата необходимы затраты времени равного 4п(, где п - количество разрядов устройства . Таким образом, быстродействие предложенного устройства в 2п раз превосходит известное.. Оборудование предложенного устройства практически равно оборудованию известного устройства, выбранного в качестве прототипа, а функциональные возможности при этом шире, чем в известном; Формула изобретения Цифровое устройство ограничения числа по модулю, содержащее регистр операнда, регистр ограничителя, регистр результата, сумматор, первый преобразователь кодов, первый блок анализа знаков, блок коррекции, две группы элементов И, группу элементов ИЛИ и элемент И, управляющий вход которого соединен с выходом блока коррекции и управляющими входами первой группы элементов И, информационные входы первой и второй групп элементов И соединены с выходами сумматора, а их выходы через группу элементов ИЛИ соединены с информационными входами регистра результата, выходы которого подсоединены к информационным входам регистра операнда, а управляющие входы регистра операнда и регистра результата соединены с шиной синхроимпульсов, выходы регистра операнда через первый .преобразователь кодов подсоединены к первым входам сумматора, а вторые входы первого преобразователя кодов соединены с выходом первого блока анализа знаков и младшим разрядом регистра результата, знаковые разряды регистра ограничителя и регистра операнда подключены соответственно к первым и вторым входам первого блока анализа знаков и блока коррекции, отличающееся тем, что, с целью увеличения быстродействия, э него введегны второй преобразователь кодов и второй блок анализа знаков, входы которого соединень соответственно со знаковыми разрядами регистра операнда и регистра результата, а выход второго блока анализа знаков через первый блок анализа знаков соединен с управляющим входом второго преобразователя кода, информационные входы которого соединены с выходами регистра операнда, а выходы - со вторыми входами сумматора. Источники информации, принятые во внимание при экспертизе. 1.Авторское свидетельство СССР № 472347, кл.О Об F 7/12, 1973. 2.Авторское свидетельство СССР № 551642, кл. G 06 F 7/39, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для ограничения чисел | 1978 |

|

SU767758A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

/

/ i V V А- Vv-

,.

0

Авторы

Даты

1979-10-05—Публикация

1977-06-01—Подача