Изобретение относится к вычислительной технике и предназначено для использованияв высоконадежных многопроцессорных вычислительных систе- м.аХ,

Целью изобретения является расширение функциональных возможностей устройства и увеличение достоверности контроля информации и признаков.

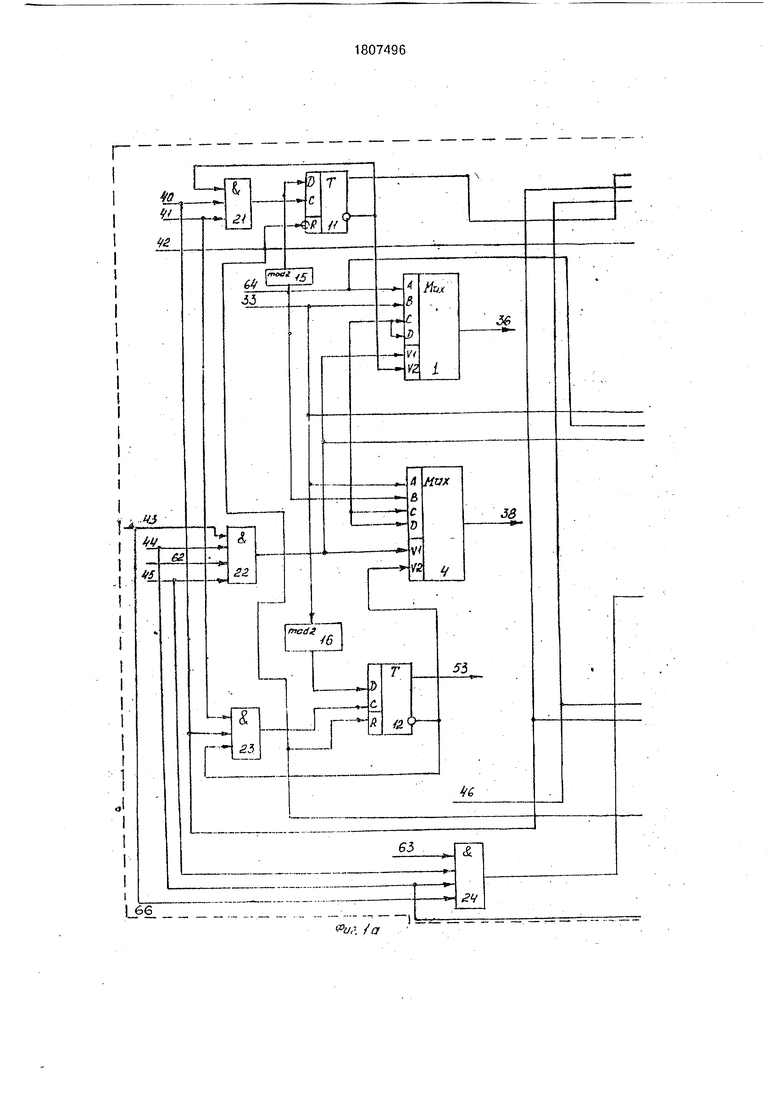

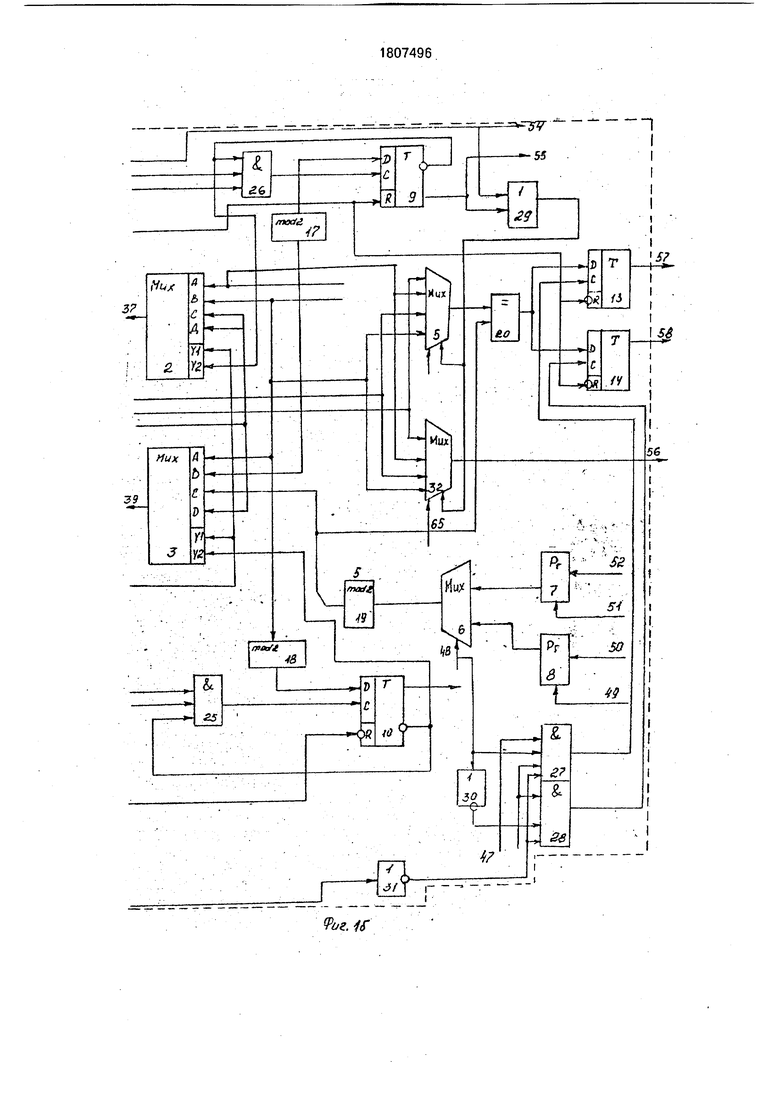

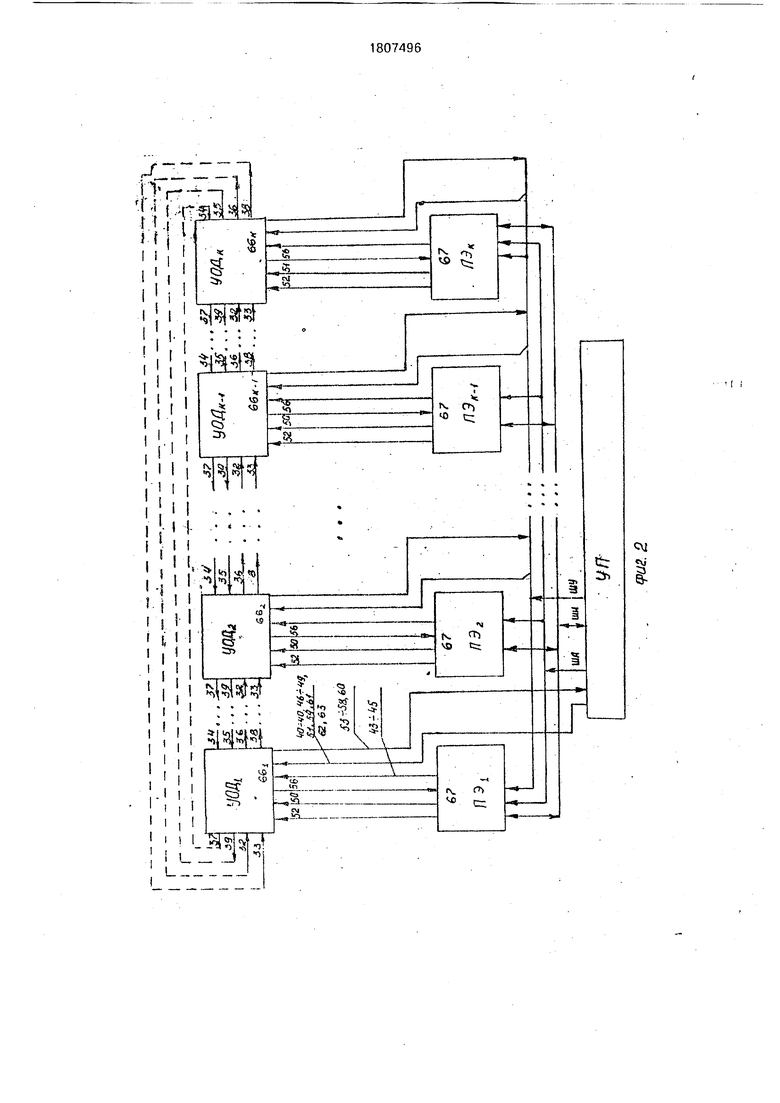

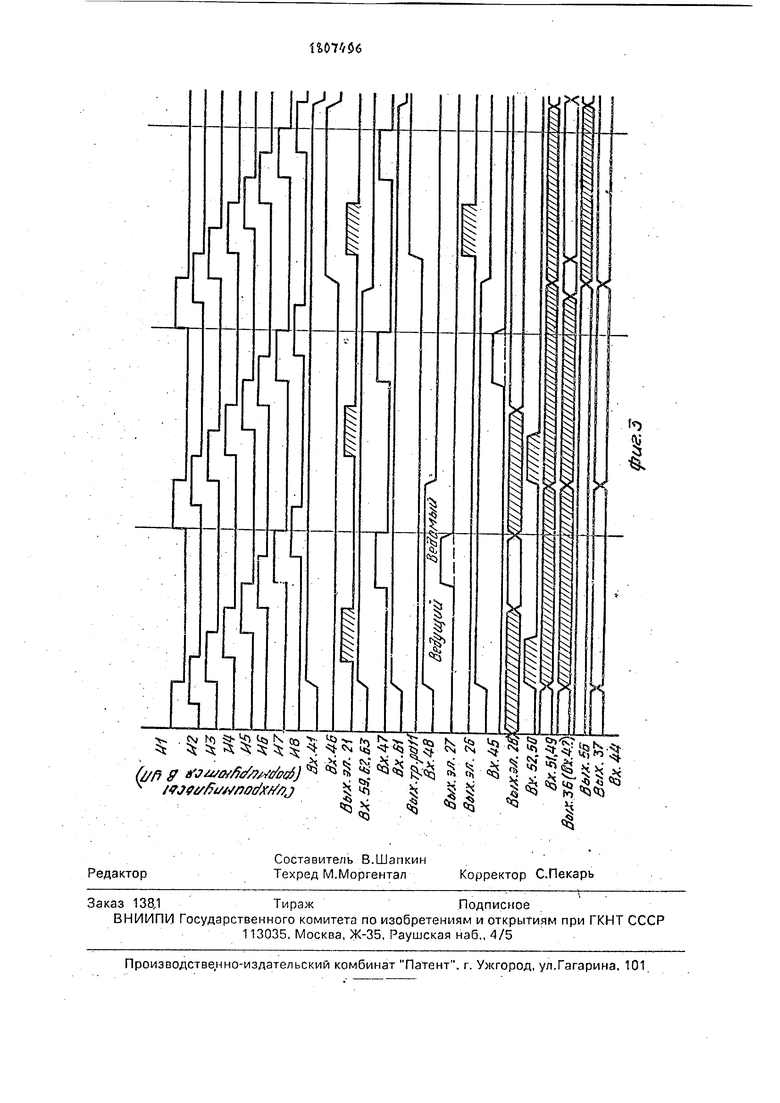

На фиг. 1а, 16 представлена функциональная схема устройства для обмена данным ; на фиг. 2 представлен пример построения многопроцессорной системы, с использованием в ней предлагаемого устройства; на фиг. 3 представлена временная диаграмма работы устройства. .

Устройство для обмена данными (фиг. 1) содержит первый-седьмой мультиплексоры 1, 4, 5, 32, 2, 3, 6 выполненные на ИМС 1533КП12 (см. 6К0.347.364-04ТУ), первый регистр 7, второй регистр 8, первый-шестой триггеры 11, 12, 9, 10. 13. 14, первый пятый

сумматоры 15-19 по модулю два, узел 20 сравнения, первый-восьмой элементы 21, 23, 26, 25, 22, 24, 27, 28 И, элемент 29 ИЛИ, первый элемент 31 НЕ. второй элемент 30 НЕ, причем первый вход 40 синхронизации устройства подключен к первым входам с первого по четвертый элементов 21, 23, 25, 26 И, выходы которых подключены соответственно ко входам синхронизации с первого по четвертый триггеров 11, 12, 10,9, первый вход 41 признака контроля устройства подключен ко вторым входам первого и второго элементов 21, 23 И, вход 43 признака активности устройства, формируемого абонентским процессором, подключен к первым входам пятого и шестого элементов 22 и 24 И, выход 44 признака ведущий/ведомый устройства подключен ко второму входу пятого и шестого элементов 22 и 24 И и ко входу первого элемента 31 НЕ. выход которого подключен к первым входам седьмого и восьмого элементов 27 и 2В И, выходы

СО

с

со

О

2

ю о

которых подключены соответственно ко входам синхронизации пятого 13 и шестого 14 триггеров, выходы которых подключены соответственно к первому и второму выходам 57 и 50 признака отказа устройства, первый вход 45 режима устройства, используемый для подключения абонентского процессора подключен к третьим входам пятого и шестого элементов 22 и 24 И, второй и третий входы 62 и 63.режимов устройства, используемые для подключения управляющего процессора, подключены соответственно к четвертым входам пятого и шестого элементов 22 и 24 И, информационные входы 64 первой группы а-ro устройства, ис- пользуемые для подключения ( о-1)-го устройства, где а 1,.... и, н -число абонентских процессоров, подключены соответст- венно ко входам первого сумматора 15 по модулю два, к информационным входам первых групп первого, второго, третьего, четвертого мультиплексоров 1, 4, 5, 32, информационные входы 33 второй группы а-го устройства, используемые для подключения (а-1) устройства, подключены ко входам вто- рого сумматора 16 по модулю два, к информационным входам вторых групп первого, второго, третьего и четвертого мультиплексоров 1, 4, 5, 32 информационные входы 34 третьей группы а-го устройства, используе- мы.е для подключения (аИ)-го устройства, подключены ко входам третьего сумматора 17 по модулю два, к информационным входам первой группы пятого мультиплексора 2, к информационным входам третьей труп- пы третьего мультиплексора 5, к информационным входам третьей группы четвертого мультиплексора 32 и к информационным входам первой группы шестого мультиплексора 3, информационные входы 35 четвер- той группы а-го устройства, используемые для подключения (а-И)-го устройства подключены к информационным входам вторых групп пятого и шестого мультиплексоров 2 и 3, к информационным входам четвертых групп третьего и четвертого мультиплексоров 5 и 32 и ко входам четвертого сумматора 18 по модулю два, информационные входы 52 и J50 пятой и шестой групп устройства, используемые для подключения абонент- ского процессора, подключены соответственно к информационным входам первого и второго регистров 7 и 8. выходы которых подключены соответственно к информационным входам первой и второй групп седь- мого мультиплексора 6, выходы которого подключены ко входам пятого сумматора 19 по модулю два, выход которого подключен к информационным входам трех групп первого, второго, пятого и шестого мультиплексоров 1, 4, 2, 3 и ко входам первой группы узла 20 сравнения, выход которого подключен к информационным входам пятого и шестого триггеров 13 и 14, вход 61 разрешения контроля устройства, используемый для подключения управляющего процессора, подключен ко вторым входам седьмого и восьмого элементов 27 и 28 И, вход 46 признака контроля устройства подключен ко вторым входам третьего и четвертого элементов 26 и 25 И, второй вход 47 синхронизации устройства подключен к третьему входу седьмого и восьмого элемента 27 и 28 И, входы 59, 65, 5.1, 49 режима с четвертого по седьмой .устройства,, используемые для подключения управляющего процессора, подключены соответственно к первому управляющему входу третьего мультиплексора 5, к первому управляющему входу четвертого мультиплексора 32, ко входу записи/считывания первого регистра 7 и ко входу записи/считывания второго регистра 8, восьмой вход 48 режима устройства, используемый для подключения управляющего процессора, подключен к управляющему входу седьмого мультиплексора 6. к четвертому входу седьмого элемента 27 И и ко входу второго элемента 30 НЕ. выход которого подключен к третьему входу восьмого элемента 28 И, вход 42 сброса устройства подключен ко входам установки в ноль второго и третьего триггеров 12 и 9 и к инверсным входам установки в ноль первого, четвертого, пятого и шестого триггеров 11,

10. 13, 14. инверсный выход первого триггера 11 подключен к третьему входу первого элемента 21 И и к первому управляющему входу первого мультиплексора 1, выход которого подключен к первому информационному выходу 36 устройства, выход первого сумматора .15 по модулю два подключен к информационному, входу первого триггера

11. прямой выход которого подключен к первому выходу 54 признака отказа устройства и к первому входу элемента 29 ИЛИ, выход которого подключен ко вторым управляющим входам третьего и четвертого мультиплексоров 5 и 32, выход четвертого мультиплексора 32 подключен ко второму информационному выходу 56 устройства, выход второго сумматора 16 по модулю два подключен к информационному входу второго триггера 12, прямой выход которого подключен ко второму выходу 53 признака Отказа устройства, инверсный выход второго триггера подключен к третьему входу второго элемента 23 И и к первому управляющему входу второго мультиплексора 4. выход которого подключен к третьему информационному выходу 38 устройства,

прямой выход третьего триггера 9 подключен к третьему вы ходу 55 п ризнака отказа устройства и ко второму входу элемента 29 ИЛИ, инверсный выход третьего триггера 9 подключен к третьему входу третьего элемента 26 И и к первому управляющему входу пятого мультиплексора 2, выход которого подключен к четвертомуинформационному выходу 37 устройства, выход третьего сумматора 17 по модулю два подключен к информационному входу третьего триггера 9, выход четвертого сумматора 18 по модулю два подключен к информационному входу четвертого триггера 10, прямой выход которого подключен к четвертому выходу 60 признака отказа уст- ройства, инверсный выход четвертого триггера 10 подключен к третьему входу четвертого элемента 25 И и к первомуусрав- ляющему входу шестого мультиплексора 3, выход которого подключен к пятому инфор- мационному выходу 39 устройства, выход пятого элемента 22 И подключен ко вторым управляющим входам первого и второго мультиплексоров 1 и 4, выход шестого элемента И подключен к вторым управляющим входам пятого и шестого мультиплексоров 2 иЗ.

В состав многопроцессорной системы входят k устройств обмена данными-66 (УОД), а также, не входящие в состав устрой- ства k-процессорных элемента (ПЭ) 67 и управняющий процессор 68 (УП). Также обозначены: ША - шина адреса; ШИ - шина информации; ШУ - шина управления,

Устройство работает в следующих ре- жимах;

; -выдача информации вправо с возможностью приема информации слева или справа;

- выдача информации влево с возмож- ностыо приема информации слева или справа;

- выдача информации влево и вправо с возможностью приема информации слева или справа;.

-трансляция информации влево или (и) вправо с возможностью приема информации слева или справа;

- выдача признаков АЛУ влево. Рассмотрим работу устройства в режиме выдачи информации вправо с приемом информации слева.

УП программно настраивает процессорные элементы (ПЭ). Каждый ПЭ и соот- ветствующий ему УОД программно приводится и следующее состояние:

- активный (выполняет все команды) или неактивный (вход 43 признака активности устройства);

- ведущий выполняет все команды и выдает информацию или признаки через УОД(вход44 признака Ведущий/ведомый устройства;

- ведомый выполняет все команды, но не выдает информацию или признаки через УОД, а только сравнивает ее на схеме сравнения 20 с принятой информацией от ведущего.

Остальные управляющие сигналы УОД получают из устройства управления управляющего процессора. Таким образом неактивные, ведомые или неактивные на выдачу УОД (низкие уровни сигналов на соответствующих входах пятого элемента 22 И) будут находится в режиме трансляции информации влево или (и) вправо. С другой стороны на третьем входе седьмого элемента 27 И и на втором входе восьмого элемента 28 И появится высокий уровень сигнала, разрешающий контроль информации у ведомого УОД.

Рассмотрим работу устройства, которое ассоциировано с ведущим ПЭ. На информационный вход пятой группы устройства поступает информация, которая заносится по переднему фронту синхроимпульсов (поступает на третий вход 51 режима устройства) в первый регистр 7. На восьмом входе 48 режима устройства присутствует высокий уровень сигнала, подключающий на выход седьмого мультиплексора 6 содержимое первого регистра 7. Затем к этой информации подформировывается бит дополнения до нечетности (свернутая инфбрмация на пятом сумматоре 19 по модулю два. На второй вход 62 режима устройства подается высокий уровень, который через пятый элемент 22 И подключает информацию с выхода седьмого мультиплексора 6 и бит дополнения до нечетности на выход второго мультиплексора 4 и на выход первого мультиплексора 1. В этом режиме на третий вход 63 режима устройства также подается кий уровень сигнала, который через шестой элемент 24 И также подключает эту информацию на выход пятого и шестого мультиплексоров 2 и 3. Информация поступает в левое УОД, которое является ведомым и в котором будет осуществляться сравнение ее со своей информацией. Таким образом информация выдается вправо для дальнейшего распространения по кольцу и для приема в один или несколько правых ПЭ, настроенных на прием и влево для сравнения ее с информацией в ведомом УОД. Информация, которая аналогичным образом выдана из левого ведущего УОД, поступает на информационные входы первых групп третьего и четвертого мультиплексоров 5 и

32 и на первый сумматор 15 по модулю два. Кроме того, аналогичная информация поступает по резервному каналу на информационные входы вторых групп третьего и четвертого мультиплексоров 5 и 32. На втором информационном выходе 56 устройства появляется информация, которая принимается далее ПЭ, настроенным на прием.

На четвертый вход 59 режима устройства поступает высокий уровень сигнала, который подключает правую группу основных информационных входов 64 первой группы устройства на вход узла 20 сравнения. Однако в. ведущем УОД фиксация результата сравнения о пятом триггере 13 отказа не происходит, так как на третьем входе седьмого элемента 27 И низкий уровень.

На выходе первого или второго сумматора 15 или 16 по модулю два появляется результат свертки всех информационных разрядов, а также бита дополнения до нечетности, То есть, если результат будет четным, что левый канал (основной или резервный) исправен (на фиг. 3 показан этот случай). Если результат нечетный, то взводится первый триггер 11, который прямым плечом переключает через элемент 29 ИЛИ третий и четвертый мультиплексоры 5 и 32 на прием информации, поступающей на информационные входы 33 второй группы устройства. Инверсным плечом первый триггер 11 блокирует последующий контроль,

Рассмотрим работу ведомого УОД, которое находится слева. На выдачу информации ведомое УОД закрыто, так как на втором входе пятого элемента 22 И низкий уровень сигнала. Это УОД находится в режиме трансляции информации вправо через первый и второй мультиплексор ы 1 и 4 в ведущий УОД. Кроме того ведомое УОД аналогичным образом контролирует принимаемую информацию на первом и втором триггерах 11 и 12 и записывает в пятый триггер 13 результат сравнения своей информации с поступающей справа от ведущего УОД (на четвертом входе управления 59 режима устройства также как и у ведущего УОД высокий уровень). Настроенный на прием ведомый ПЭ принимает информацию с выхода четвертого мультиплексора 32.

Рассмотрим режим выдачи признаков работы АЛУ ПЭ с контролем. Когда не производится обмен информацией через УОД, то его ресурсы используются для контроля признаков работы АЛУ (знак результата, ноль результата, переполнение разрядной сетки, переносы) В этом режиме у ведущего УОД на выход седьмого мультиплексора 6 и далее на выход пятого и шестого мультиплексоров 2 и 3 подключается содержимое второго регистра 8.

Ведомое УОД принимает эти признаки с информационных входов 34 третьей группы устройства через третий мультиплексор 5 на узел сравнения. Результат сравнения заносится в шестой триггер 14..

Режим трансляции влево и вправо показан на фиг. 3 с соответствующим управлени0 ем на входах устройства.

Формул а изобретения Устройство для обмена данными, содержащее с первого по седьмой мультиплексоры, первый и второй регистры, первый и

5 второй триггеры, с первого по восьмой элементы И, первый сумматор по модулю два, узел сравнения и элемент ИЛИ, отличаю- ще ее я тем, что, с целью повышения достоверности контроля за счет контроля инфор0 мационных признаков, формируемых в абонентских процессорах, .оно содержит с третьего по шестой триггеры, с второго по пятый сумматоры по модулю два, первый и второй элементы НЕ, причем первый вход

5 синхронизации устройства подключен к первым входам с первого по четвертый эле- ,ментов И, выходы которых подключены соответственно к входам синхронизации с первого по четвертый триггеров, первый

0 вход признака контроля устройства подключен к вторым входам первого и второго элементов И, вход признака активности устройства, формируемого абонентским процессором, подключен к первым входам

5 пятого и шестого элементов И, выход признака ведущий/ведомый устройства подключен к второму входу пятого и шестого элементов И и входу первого элемента НЕ, выход которого подключен к первым входам

0 седьмого и восьмого элементов И, выходы которых подключены соответственно к входам синхронизации пятого и шестого триггеров, выходы которых подключены соответственно к первому и второму выхо5 дам признака отказа .устройства, .первый вход режима устройства, используемый для подключения абонентского процессора, подключен к третьим входам пятого и шестого элементов И, второй и третий входы

0 режимов устройства, используемые для подключения управляющего процессора, подключены соответственно к четвертым входам пятого и шестого элементов И, информационные входы первой группы а-го

5 устройства, используемые для подключения (а-1)-го устройства, где а 1, ..., н, н - число абонентских процессоров, подключены соответственно к входам первого сумматора по модулю два, к информационным входам первых групп первого, второго, третьего,

четвертого мультиплексоров, информационные входы второй группы а-го устройства, используемые для подключения (а-1)-го устройства, подключены к входам второго сумматора по модулю два, к информационным входам вторых групп первого, второго, третьего и четвертого мультиплексоров, информационные входы третьей группы а-го устройства, используемые для подключения (а+1)-го устройства, подключены к входам третьего сумматора по модулю два, к информационным входам первой группы пятого мультиплексора, информационным входам третьей группы третьего мультиплексора, информационным входам третьей группы четвертого мультиплексора и информационным входам первой группы шестого мультиплексора, информационные вяоды четвертой группы а-го устройства, используемые для подключения (а+1)-го устройства, подключены к информационным входам вторых групп пятого и шестого мультиплексоров, информационным входам четвертых групп третьего и четвертого мультиплексоров и входам четвертого сумматора по модулю два, информационные входы пятой и шестой групп устройства, используемые для подключения абонентского процессора, подключены соответственно к информационным входам первого и второго регистров, выходы которых подключены соответственно к информационным входам первой и второй групп седьмого мультиплексора, выходы которого подключены к входам пятого сумматора по модулю два, выход которого подключен к информационным входам трех групп первого, второго, пятого и шестого мультиплексоров и входам первой группы узла сравнения, выход которого подключен к информационным входам пятого и шестого триггеров, вход разрешения контроля устройства, используемый для подклю- че ния .управляющего процессора, подключен к вторым входам седьмого и восьмого элементов И, вход признака контроля устройства подключен к вторым входам третьего и четвертого элементов И, второй вход синхронизации устройства подключен к третьему входу седьмого элемента И, входы режима с четвертого по седьмой устройства, используемые для подключения управляющего процессора, подключены соответственно к первому управляющему входу третьего мультиплексора, первому управляющему входу четвертого мультиплексора, к входу записи-считывания первого регистра и входу записи-считывания второго регистра, восьмой вход режима устройства, используемый для подключения

управляющего процессора, подключен к управляющему входу седьмого мультиплексора, четвертому входу седьмого элемента И и входу второго элемента НЕ, выход которого 5 подключен к третьему входу восьмого элемента И, вход сброса устройства подключен к входам установки в О второго и третьего триггеров и инверсным входам установки в О первого, четвертого, пятого и шестого

0 триггеров, инверсный, выход первого триггера подключен к третьему входу первого элемента И и первому управляющему входу первого мультиплексора, выход которого подключен к первому информационному

5 выходу устройства, выход первого сумматора по модулю два подключен к информационному входу первого триггера, прямой выход которого подключен к первому выхо- ду признака отказа устройства и первому

0 входу элемента ИЛИ, выход которого подключен к вторым управляющим входам третьего и четвертого мультиплексоров, выход четвертого мультиплексора подключен к второму информационному выходу уст5 ройства. выход второго сумматора по модулю два подключен к информационному входу второго триггера, прямой выход которого подключен к второму выходу признака отказа устройства, инверсный выход второ0 го триггера подключен к третьему входу второго элемента И и первому управляющему входу второго мультиплексора, выход кото- .рого подключен к .третьему информационному выходу устройства, прямой выход

5 третьего триггера подключен к f ретьему выходу признака отказа устройства и второму входу элемента ИЛИ, инверсный выход третьего триггера подключен к третьему входу третьего элемента И и первому управ0 ляющему входу пятого мультиплексора, выход которого подключён к четвертому информационному выходу устройства, выход третьего сумматора по модулю два подключен к информационному входу третьего

5 триггера, выход четвертого сумматора по модулю два подключен к информационному входу четвертого триггера, прямой выход которого подключен к четвертому выходу признака отказа устройства, инверсный вы0 ход четвертого триггера подключен к третьему входу четвертого элемента И и первому управляющему входу шестого мультиплексора, выход которого подключен к пятому информационному выходу устройства, вы5 ход пятого элемента И подключен к вторым управляющим входам первого и второго мультиплексоров, выход шестого элемента И подключен к вторым управляющим входам пятого и шестого мультиплексоров.

%r . /a

96W.081

CM

I

Ъ

§ i

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| ЭЛЕКТРОННОЕ УСТРОЙСТВО КАТАПУЛЬТНОГО КРЕСЛА ДЛЯ САМОЛЕТА | 2017 |

|

RU2669720C1 |

| Логический процессор | 1986 |

|

SU1315995A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| Устройство связи для вычислительной системы | 1984 |

|

SU1164722A1 |

Изобретение относится к вычислительной технике и предназначено для использования в высоконадежных многопроцессорных системах. Цель изобретения - повышение достоверности контроля за счет контроля информационных признаков, формируемых в абонентских процессорах. Устройство для обмена данными содержит первый-шестой коммутаторы шин, регистр информации, регистр признаков, первый-шестой триггеры, первый-пятый элементы сумматор по модулю 2, схему сравнения, первый-восьмой элементы И, элемент 29 ИЛИ, первый элемент НЕ. второй элемент НЕ, седьмой коммутатор 32 шин. 3 ил.

| Устройство для обмена данными | 1986 |

|

SU1410049A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Система коммутации | 1986 |

|

SU1410047A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-04-07—Публикация

1991-02-06—Подача