Изобретение относится к цифровой вычислительной технике и может быть использовано в КМДП интегральных схемах при реализации устройств логической обработки многоразрядных двоичных данных.

Известна реализация многоразрядного устройства логического сравнения на КМДП транзисторах, которое содержит логические элементы 2И-НЕ в каждом разряде и выходной блок статического типа (Патент США №5281946, G 05 B 1/03, G 06 F 7/02, НКИ 340-146.2 от 25.01.94). Недостаток устройства - ограничение быстродействия при увеличении числа разрядов, что обусловлено линейным ростом числа емкостных нагрузок на выходах логических элементов и увеличением величины нагрузок в том числе за счет пропорционального роста числа последовательно включенных логических транзисторов р-типа выходного блока.

Наиболее близким техническим решением к предлагаемому является устройство логического сравнения на основе парафазного каскадного логического устройства на КМДП транзисторах (Патент РФ по заявке №2002112513/09, фиг.1-2, от 13.05.2002. Решение о выдаче патента от 04.02.2003). Это устройство, принятое за прототип, содержит последовательно включенные каскады - одноразрядные блоки сравнения с использованием парафазных входных и выходных сигналов, которые работают под общим однофазным тактированием с асинхронной последовательной передачей логического сигнала через разделительные инверторы. Парафазный выходной блок, содержащий звенья из двух выходных транзистора n-типа на разряд, при этом параллельно осуществляет выборку результата сравнения.

Недостатком этого устройства является недостаточное быстродействие при большом числе разрядов сравниваемых операндов, что связано с использованием в каждом блоке (каскаде) сравнения одноразрядных логических элементов с последовательным распространением сигнала соответствующего критерию равенства от блока сравнения старшего разряда операндов к более младшему. В результате величина задержки выходного сигнала результата сравнения в наихудшем случае (на равенство) определяется двумя логическими переходами на один разряд и линейно зависит от числа разрядов N.

Технической задачей, решаемой в изобретении, является повышение быстродействия устройства при сравнении многоразрядных операндов.

Поставленная цель достигается тем, что устройство сравнения на КМДП транзисторах, содержащее k блоков сравнения и выходной блок, каждый блок сравнения содержит три транзистора р-типа, тактовый транзистор n-типа, три инвертора и первый логический элемент, выполненный на шести транзисторах n-типа, из которых соединены попарно последовательно первый и второй, третий и четвертый, пятый и второй, шестой и четвертый, стоки первого и третьего транзисторов n-типа являются соответственно первым и вторым выводами логического элемента, объединенные стоки пятого и шестого транзисторов n-типа являются третьим выводом логического элемента, истоки второго и четвертого транзисторов n-типа подключены к общему выводу логического элемента, объединенные по два затворы первого и шестого, третьего и пятого транзисторов n-типа подключены соответственно к первому и второму входам первого логического элемента, на которые подаются парафазные сигналы соответствующего разряда первого операнда, затворы второго и четвертого транзисторов n-типа подключены соответственно к третьему и четвертому входам первого логического элемента, на которые подаются парафазные сигналы одноименного разряда второго операнда, в каждом блоке сравнения первый и второй выводы первого логического элемента подключены непосредственно к входам одноименных инверторов и соответственно через первый и второй транзисторы р-типа соединены с шиной питания, а третий транзистор р-типа включен между шиной питания и входом третьего инвертора, общий вывод первого логического элемента через тактовый транзистор n-типа соединен с общей шиной, выходы первого, второго и третьего инверторов являются одноименными выходами блока сравнения, затворы транзисторов р-типа и тактового транзистора n-типа в каждом блоке сравнения объединены, а в первом блоке сравнения подключены дополнительно к тактовой шине, выходной блок содержит первый и второй транзисторы р-типа и тактовый транзистор n-типа, затворы которых подключены к тактовой шине, выходной блок содержит k транзисторных звеньев, каждое из которых включает в себя первый и второй выходные транзисторы n-типа, затворы которых подключены соответственно к первому и второму выходам одноименного с транзисторным звеном блока сравнения, а стоки которых подключены соответственно к первому и второму выходам устройства, которые через одноименные транзисторы р-типа выходного блока соединены с шиной питания, истоки первого и второго выходных транзисторов n-типа в каждом транзисторном звене объединены, а в первом транзисторном звене через тактовый транзистор n-типа выходного блока дополнительно соединены с шиной земли, и каждый блок сравнения содержит m идентичных логических элементов, причем в каждом блоке сравнения первые выводы всех логических элементов соединены между собой, вторые выводы всех логических элементов также соединены между собой, а третий вывод каждого предыдущего логического элемента соединен с общим выводом последующего логического элемента, третий вывод последнего из m логических элементов в каждом блоке сравнения соединен с входом третьего инвертора, выходной блок содержит третий транзистор р-типа, который включен между шиной питания и третьим выходом устройства и затвор которого соединен с тактовой шиной, а каждое транзисторное звено содержит третий выходной транзистор n-типа, исток которого соединен с истоками первого и второго выходных транзисторов n-типа, а затвор подключен к третьему выходу одноименного с данным транзисторным звеном блока сравнения, сток третьего выходного транзистора n-типа каждого предыдущего транзисторного звена соединен с истоками выходных транзисторов n-типа последующего транзисторного звена, сток третьего выходного транзистора n-типа последнего из k транзисторных звеньев соединен с третьим выходом устройства.

Существенными отличительными признаками в указанной совокупности признаков являются наличие в каждом блоке сравнения нескольких - (m) одноразрядных логических элементов с соответствующими связями, введение в выходной блок третьего транзистора р-типа и в каждое транзисторное звено дополнительно третьего выходного транзистора n-типа, затвор которого соединен с третьим выходом соответствующего блока сравнения, и новые связи выходных транзисторов n-типа транзисторных звеньев в выходном блоке.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - повышение быстродействия устройства при сравнении многоразрядных операндов за счет уменьшения числа логических переходов и следовательно числа временных задержек путем одновременного сравнения нескольких одноименных разрядов операндов в каждом из k блоков сравнения и параллельной передачи результатов сравнения по критерию равенства от каждого блока сравнения в выходной блок.

Действительно, использование в блоке сравнения m логических элементов, каждый из которых реализует функцию одноразрядного сравнения, не ведет к соответствующему росту числа логических переходов, а задержка в блоке сравнения пропорциональна значению m. В случае наибольшей задержки - при равенстве группы из m разрядов двух операндов каждый из k блоков сравнения одновременно формирует на третьем выходе сигнал, который открывает третий выходной транзистор n-типа соответствующего транзисторного звена выходного блока. Последовательное соединение указанных транзисторов, число которых равно k, также не связано с дополнительными логическими переходами, а задержка в выходном блоке пропорциональна значению k. Таким образом, функция равенства реализуется посредством трех логических переходов (один из них - инвертор) с задержкой, пропорциональной (m+k) при числе разрядов сравниваемых операндов N=m·k.

Минимальная величина задержки в устройстве в случае транзисторов равных размеров имеет место при k=2m, поскольку в каждом из m логических элементов цепь содержит два транзистора на разряд, а в каждом из k транзисторных звеньев выходного блока - один. В результате суммарная задержка в заявленном устройстве в зависимости от числа разрядов в наихудшем случае растет пропорционально  , в то время как в известном устройстве задержка пропорциональна 2N (по одной задержке на каскад и на инвертор). Для 8-разрядного устройства m=2, а k=4, для 32-разрядного m=4, а k=8.

, в то время как в известном устройстве задержка пропорциональна 2N (по одной задержке на каскад и на инвертор). Для 8-разрядного устройства m=2, а k=4, для 32-разрядного m=4, а k=8.

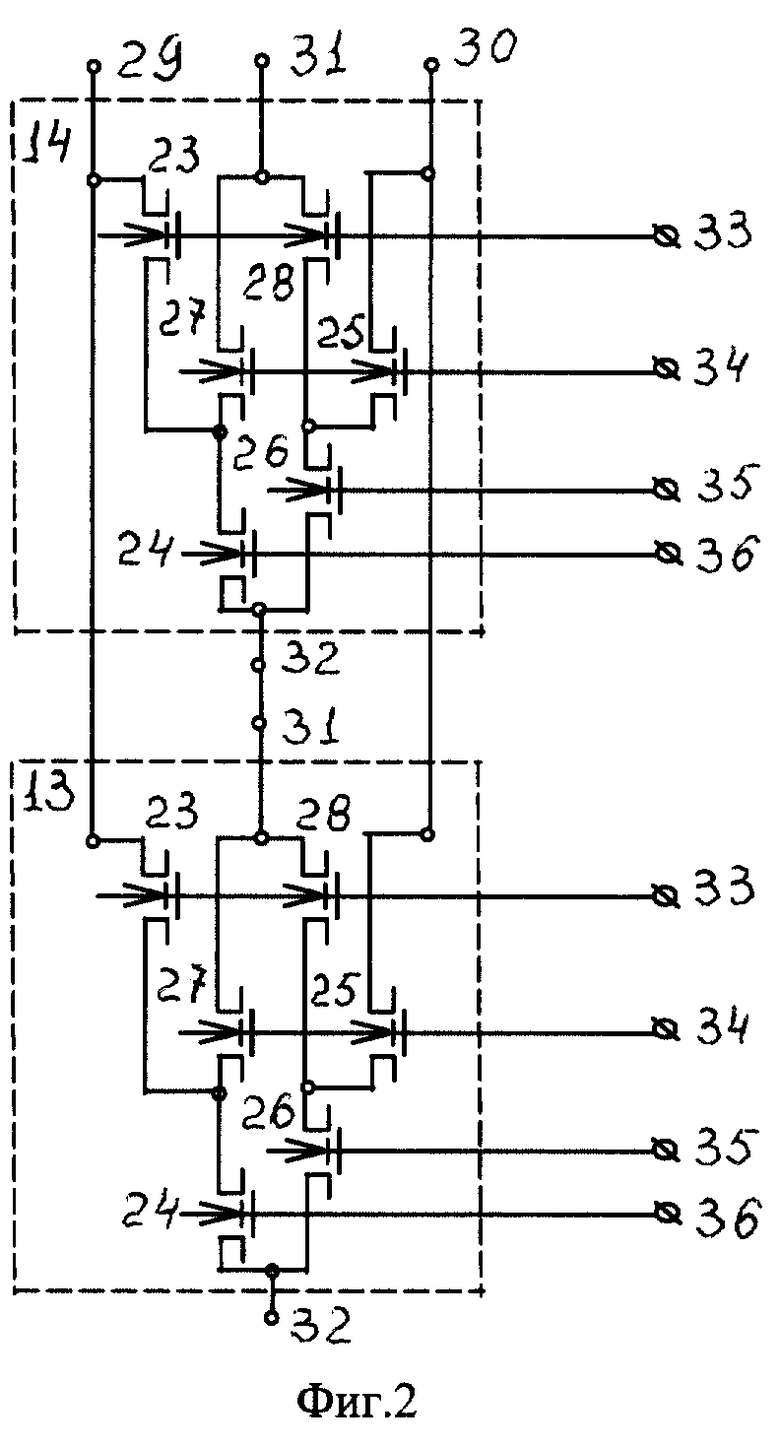

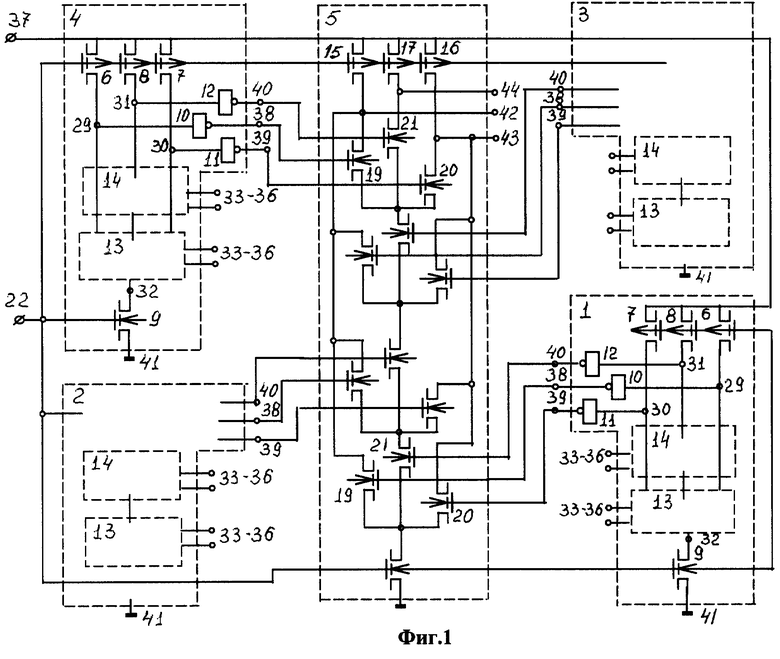

На фиг.1 приведена принципиальная схема заявляемого устройства, представленного в виде 8 разрядного устройства сравнения при k=4. На фиг.2 приведена принципиальная схема двух логических элементов (при m=2).

Устройство сравнения на КМДП транзисторах (фиг.1) содержит четыре блока сравнения 1-4 и выходной блок 5. Каждый блок сравнения содержит три транзистора 6-8 р-типа, тактовый транзистор 9 n-типа, три инвертора 10-12, а также два идентичных логических элемента 13-14 соответственно блоку сравнения на два разряда. Выходной блок 5 содержит три транзистора 15-17 р-типа, тактовый транзистор 18 n-типа, а также четыре транзисторных звена, каждое из которых состоит из трех выходных транзисторов 19-21 n-типа.

Затворы транзисторов 6-8 р-типа и тактового транзистора 9 n-типа блоков сравнения 1-4, а также затворы транзисторов 15-17 р-типа и тактового транзистора 18 n-типа выходного блока 5 подключены к тактовой шине 22.

Каждый из логических элементов 13-14 (фиг.2) выполнен на шести транзисторах 23-28 n-типа, из которых соединены попарно последовательно первый 23 и второй 24, третий 25 и четвертый 26, пятый 27 и второй 24, шестой 28 и четвертый 26. Стоки первого 23 и третьего 25 транзисторов n-типа являются соответственно первым 29 и вторым 30 выводами логического элемента, объединенные стоки пятого 27 и шестого 28 транзисторов n-типа являются третьим выводом 31 логического элемента, истоки второго 24 и четвертого 26 транзисторов n-типа подключены к общему выводу 32 логического элемента.

Объединенные по два затворы первого 23 и шестого 28, третьего 25 и пятого 27 транзисторов n-типа подключены соответственно к первому 33 и второму 34 входам логического элемента, на которые подаются парафазные сигналы соответствующего разряда первого операнда, затворы второго 24 и четвертого 26 транзисторов n-типа типа подключены соответственно к третьему 35 и четвертому 36 входам логического элемента, на которые подаются парафазные сигналы одноименного разряда второго операнда.

В каждом блоке сравнения 1-4 первый транзистор 6 р-типа включен между шиной питания 37 и входом первого инвертора 10, к которому подключены также первые выводы 29 логических элементов 13 и 14, а выход которого является первым выходом 38 соответствующего блока сравнения. Второй транзистор 7 р-типа включен между шиной питания 37 и входом второго инвертора 11, к которому подключены также вторые выводы 30 логических элементов 13 и 14, а выход которого является вторым выходом 39 соответствующего блока сравнения. Третий транзистор 8 р-типа включен между шиной питания 37 и входом третьего инвертора 12, выход которого является третьим выходом 40 соответствующего блока сравнения. Тактовый транзистор 9 n-типа включен между общим выводом 32 первого логического элемента 13 и шиной земли 41. Третий вывод 31 первого логического элемента 13 подключен к общему выводу 32 последующего - второго логического элемента 14, третий вывод которого соединен с входом третьего инвертора 12 того же блока сравнения.

В выходном блоке 5 первый транзистор 15 р-типа включен между шиной питания 37 и первым выходом 42 устройства, к которому подключены также стоки первых выходных транзисторов 19 n-типа всех 4 транзисторных звеньев. Второй транзистор 16 р-типа включен между шиной питания 37 и вторым выходом 43 устройства, к которому подключены также стоки вторых выходных транзисторов 20 n-типа всех транзисторных звеньев. Тактовый транзистор 18 n-типа включен между объединенными истоками выходных транзисторов 19-21 n-типа первого транзисторного звена и шиной земли 41. Сток третьего выходного транзистора 21 n-типа каждого предыдущего транзисторного звена соединен с истоками выходных транзисторов 19-21 n-типа последующего транзисторного звена, а сток третьего выходного транзистора 21 n-типа последнего четвертого транзисторного звена подключен непосредственно к третьему выходу 44 устройства и через третий транзистор 17 р-типа соединен с шиной питания 37.

Затворы первого 19, второго 20 и третьего 21 выходных транзисторов n-типа транзисторных звеньев подключены соответственно к первому 38, второму 39 и третьему 40 выходам одноименного с транзисторным звеном блока сравнения.

Инверторы 10-12 включены между шиной питания 37 и шиной земли 41.

Устройство работает следующим образом. При сравнении двух 8-разрядных операндов (двоичных чисел) А=X8X7...X2X1 и В=У8У7...У2У1 на первый 33 и второй 34 входы первого логического элемента 13 первого блока сравнения 1 подаются парафазные сигналы старшего 8-го разряда первого операнда А, соответствующие X8, а на третий 35 и четвертый 36 входы того же логического элемента - парафазные сигналы старшего 8-го разряда второго операнда В, соответствующие У8. На те же входы 33-35 второго логического элемента 14 первого блока сравнения 1 подаются парафазные сигналы более младшего 7-го разряда операндов А и В, соответствующие Х7 и У7. На аналогичные входы 33-36 первого 13 и второго 14 логических элементов второго блока сравнения 2 подаются парафазные сигналы, соответствующие 6 и 5 разрядам операндов (Х6-У6 и Х5-У5). На входы 33-36 логических элементов третьего блока сравнения 3 подаются парафазные сигналы, соответствующие 4 и 3 разрядам операндов (Х4-У4 и Х3-Y3). На входы 33-34 второго 14 логического элемента последнего четвертого блока сравнения 4 подаются парафазные сигналы, соответствующие младшему 1 разряду первого операнда (X1), а на входы 35-36 - парафазные сигналы, соответствующие младшему 1 разряду второго операнда (Y1). Причем первый 33 и третий 35 входы логических элементов соответствуют прямому значению двоичного разряда, а второй 34 и четвертый 36 входы -логически дополняющему значению того же разряда. Двоичному значению логической 1 соответствует высокий уровень напряжения шины питания, а значению логического 0 - низкий уровень напряжения шины земли. Открытому или замкнутому состоянию транзистора n-типа соответствует сигнал логической 1, поданный на затвор транзистора.

В исходном состоянии - на первом полутакте, при нулевом сигнале на тактовой шине 22 все тактовые транзисторы 9 и 18 n-типа закрыты, а транзисторы 6-8 и 15-17 р-типа блоков сравнения 1-4 и выходного блока 5 открыты. От шины питания 37 через указанные транзисторы р-типа происходит процесс предзаряда узловых емкостей, связанных с входами первого, второго и третьего инверторов 10-12 блоков сравнения 1-4, и емкостей нагрузки, связанных с выходами 42-44 устройства до уровня логической 1. При этом на выходах соответствующих инверторов и выходах 38-40 блоков сравнения 1-4 поддерживаются состояния логического 0. Поэтому выходные транзисторы 19-21 n-типа всех транзисторных звеньев выходного блока 5 закрыты, а на выходах 42-44 устройства - сигналы логической 1. На первом полутакте на входах 33-36 логических элементов 13-14 всех блоков сравнения 1-4 устанавливаются соответствующие операндам парафазные сигналы.

На втором полутакте после подачи положительного сигнала на тактовую шину 22 тактовые транзисторы 9 и 18 n-типа всех блоков открываются, а транзисторы р-типа закрываются.

Каждый логический элемент реализует функцию полного одноразрядного логического сравнения. Причем, когда Х>У в открытом состоянии находятся первый 23 и второй 24 транзисторы n-типа каждого логического элемента, и узловая емкость, связанная с входом первого инвертора 10 через указанную цепь и тактовый транзистор 9, может разряжаться до уровня логического 0. На выходе первого инвертора 10 и соответственно на первом выходе 38 блока сравнения при этом формируется сигнал логической 1. Когда Х<У, в открытом состоянии находятся третий 25 и четвертый 26 транзисторы n-типа логического элемента, и узловая емкость, связанная с входом второго инвертора 11, может разряжаться до уровня логического 0. При этом на втором выходе 39 блока сравнения формируется сигнал логической 1. В случае равенства Х=У замыкается цепь между третьим выходом 31 и общим выводом 32 логического элемента, поскольку открытыми являются либо пятый 27 и второй 24 транзисторы n-типа логического блока (Х=У=0), либо шестой 28 и четвертый 26 транзисторы n-типа (Х=У=1). При этом на третьем выходе 40 блока сравнения формируется сигнал логической 1.

Если первая или вторая логические ситуации характерны уже для старшего разряда операндов и реализуются соответственно в первом логическом элементе 13 первого блока сравнения 1 (X8>У8 или Х8<У8), то независимо от состояний других логических элементов открывается первый 19 или второй 20 выходные транзисторы n-типа первого транзисторного звена выходного блока 5, и емкость нагрузки, связанная с первым 42, или со вторым 43 выходами устройства, разряжается через указанные транзисторы и тактовый транзистор n-типа 18 выходного блока 5 до уровня логического 0. Таким образом реализуются функции А>В и А<В.

В случае Х8=У8 состояние выходов устройства зависит прежде всего от сигналов, поданных на входы 33-36 второго логического элемента 14 первого блока сравнения 1, соответствующих переменным Х7-У7. При Х7>У7 или Х7<У7 также разряжаются узловые емкости, связанные с входами первого 10 или второго 11 инверторов первого блока сравнения 1, поскольку цепь между третьим выходом 31 и общим выводом 32 первого логического элемента 13 логического элемента первого блока сравнения 1 замкнута. Первый 19 или второй 20 выходные транзисторы n-типа первого транзисторного звена выходного блока 5 открыты, и емкость нагрузки, связанная с первым 42, или со вторым 43 выходами устройства, также разряжается до уровня логического 0. Таким образом реализуются функции А>В и А<В по значениям переменных, соответствующих 7 разряду операндов.

При равенстве переменных, соответствующих старшим 8 и 7 разрядам операндов А и В (Х8=У8=Х7=У7), первый 38 и второй 39 выходы первого блока сравнения 1 сохраняют состояние логического 0, первый 19 и второй 20 выходные транзисторы n-типа первого транзисторного звена выходного блока 5 закрыты, а на третьем выходе 40 первого блока сравнения 1 формируется сигнал логической 1 и третий выходной транзистор 21 n-типа первого транзисторного звена открыт, поскольку узловая емкость, связанная с входом третьего инвертора 12 первого блока сравнения 1 разряжается через транзисторные цепи, соответствующие реализации функции равенства первого 13 и второго 14 логических элементов первого блока сравнения. Открытый третий выходной транзистор 21 n-типа первого транзисторного звена выходного блока 5 совместно с тактовым транзистором 18 n-типа создают проводящую цепь для функционирования выходных транзисторов 19-21 n-типа второго транзисторного звена выходного блока 5, затворы которых подключены к выходам второго блока сравнения 2, на входы 33-36 логических элементов 13-14 которого подаются парафазные сигналы, соответствующие 6 и 5 разрядам операндов А и В. Формирование сигналов на выходах второго блока сравнения 2 по переменным, соответствующим 6 и 5 разрядам (Х6-У6, Х5-У5), происходит также, как в первом блоке сравнения 1, а формирование сигналов сравнения на выходах устройства происходит при включении одного из выходных транзисторов 19-21 n-типа второго транзисторного звена выходного блока 5. Аналогично происходит взаимодействие логических элементов 13 и 14 третьего 3 и четвертого 4 блоков сравнения соответственно с выходными транзисторами 19-21 n-типа третьего 3 и четвертого 4 транзисторных звеньев выходного блока 5.

В случае логического равенства операндов А и В первые и вторые выходные транзисторы 19-20 n-типа всех 4 транзисторных звеньев выходного блока 5 закрыты, а третьи выходные транзисторы 21 n-типа всех 4 транзисторных звеньев открыты. На третьем выходе 44 устройства при этом формируется сигнал логического 0.

Устройство позволяет реализовать функцию полного сравнения операндов (по критериям - "больше", "меньше", "равно"). Подключение в качестве нагрузки к первому 42 и третьему 44 выходам устройства логического элемента 2И-НЕ позволяет получить значение функции сравнения по критерию "больше или равно" - "меньше", а подключение в качестве нагрузки к второму 43 и третьему 44 выходам устройства логического элемента 2И-НЕ позволяет получить значение функции сравнения по критерию "меньше или равно" - "больше". Подключение к выходам 42-44 устройства логического элемента 3И-НЕ позволяет сформировать асинхронный сигнал завершения операции сравнения, который может быть использован для ограничения длительности такта, благодаря чему повышается быстродействие устройства на системном уровне.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| МНОГОРАЗРЯДНОЕ УСТРОЙСТВО ЛОГИЧЕСКОГО СРАВНЕНИЯ | 2007 |

|

RU2328026C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в КМДП интегральных схемах в качестве устройства логической обработки многоразрядных двоичных данных. Технический результат заключается в повышении быстродействия устройства при сравнении многоразрядных операндов. Устройство содержит k блоков сравнения, каждый из которых содержит три транзистора р-типа 6-8, тактовый транзистор n-типа 9, три инвертора 10-12 и m логических элементов, выполненных в виде одноразрядного элемента сравнения на шести транзисторах n-типа 23-28, а также содержит выходной блок 5, содержащий три транзистора р-типа 15-17, тактовый транзистор n-типа 18 и соответственно числу блоков сравнения k транзисторных звеньев, каждое из которых выполнено на трех транзисторах 19-21 n-типа. Устройство позволяет реализовать функцию полного сравнения операндов по критериям - "больше", "меньше", "равно". 2 ил.

Устройство сравнения на КМДП транзисторах, содержащее k блоков сравнения и выходной блок, каждый блок сравнения содержит три транзистора р-типа, тактовый транзистор n-типа, три инвертора и первый логический элемент, выполненный на шести транзисторах n-типа, из которых соединены попарно последовательно первый и второй, третий и четвертый, пятый и второй, шестой и четвертый, стоки первого и третьего транзисторов n-типа являются соответственно первым и вторым выводами логического элемента, объединенные стоки пятого и шестого транзисторов n-типа являются третьим выводом логического элемента, истоки второго и четвертого транзисторов n-типа подключены к общему выводу логического элемента, объединенные по два затворы первого и шестого, третьего и пятого транзисторов n-типа подключены соответственно к первому и второму входам первого логического элемента, на которые подаются парафазные сигналы соответствующего разряда первого операнда, затворы второго и четвертого транзисторов n-типа подключены соответственно к третьему и четвертому входам первого логического элемента, на которые подаются парафазные сигналы одноименного разряда второго операнда, в каждом блоке сравнения первый и второй выводы первого логического элемента подключены непосредственно к входам одноименных инверторов и соответственно через первый и второй транзисторы р-типа соединены с шиной питания, а третий транзистор р-типа включен между шиной питания и входом третьего инвертора, общий вывод первого логического элемента через тактовый транзистор n-типа соединен с общей шиной, выходы первого, второго и третьего инверторов являются одноименными выходами блока сравнения, затворы транзисторов р-типа и тактового транзистора n-типа в каждом блоке сравнения объединены, а в первом блоке сравнения подключены дополнительно к тактовой шине, выходной блок содержит первый и второй транзисторы р-типа и тактовый транзистор n-типа, затворы которых подключены к тактовой шине, выходной блок содержит k транзисторных звеньев, каждое из которых включает в себя первый и второй выходные транзисторы n-типа, затворы которых подключены соответственно к первому и второму выходам одноименного с транзисторным звеном блока сравнения, а стоки которых подключены соответственно к первому и второму выходам устройства, которые через одноименные транзисторы р-типа выходного блока соединены с шиной питания, истоки первого и второго выходных транзисторов n-типа в каждом транзисторном звене объединены, а в первом транзисторном звене через тактовый транзистор n-типа выходного блока дополнительно соединены с шиной земли, отличающийся тем, что каждый блок сравнения содержит m идентичных логических элементов, причем в каждом блоке сравнения первые выводы всех логических элементов соединены между собой, вторые выводы всех логических элементов также соединены между собой, а третий вывод каждого предыдущего логического элемента соединен с общим выводом последующего логического элемента, третий вывод последнего из m логических элементов в каждом блоке сравнения соединен с входом третьего инвертора, выходной блок содержит третий транзистор р-типа, который включен между шиной питания и третьим выходом устройства и затвор которого соединен с тактовой шиной, а каждое транзисторное звено содержит третий выходной транзистор n-типа, исток которого соединен с истоками первого и второго выходных транзисторов n-типа, а затвор подключен к третьему выходу одноименного с данным транзисторным звеном блока сравнения, сток третьего выходного транзистора n-типа каждого предыдущего транзисторного звена соединен с истоками выходных транзисторов n-типа последующего транзисторного звена, сток третьего выходного транзистора n-типа последнего из k транзисторных звеньев соединен с третьим выходом устройства.

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| US 4668880, 26.05.1987 | |||

| US 5281946, 25.01.1994 | |||

| ШАРНИРНЫЙ ОТКЛОНИТЕЛЬ КОМПОНОВКИ БУРИЛЬНОЙ КОЛОННЫ | 1992 |

|

RU2082864C1 |

Авторы

Даты

2004-09-20—Публикация

2003-04-11—Подача