X

Изобретение относится к вычислительной технике и автоматике и может быть использовано в вычислительных системах для цифровой обработки Данных.

Целью изобретения является расширение области применения за счет реализации программной перестройки структуры и увеличение разрядности обрабатываемых чисел.

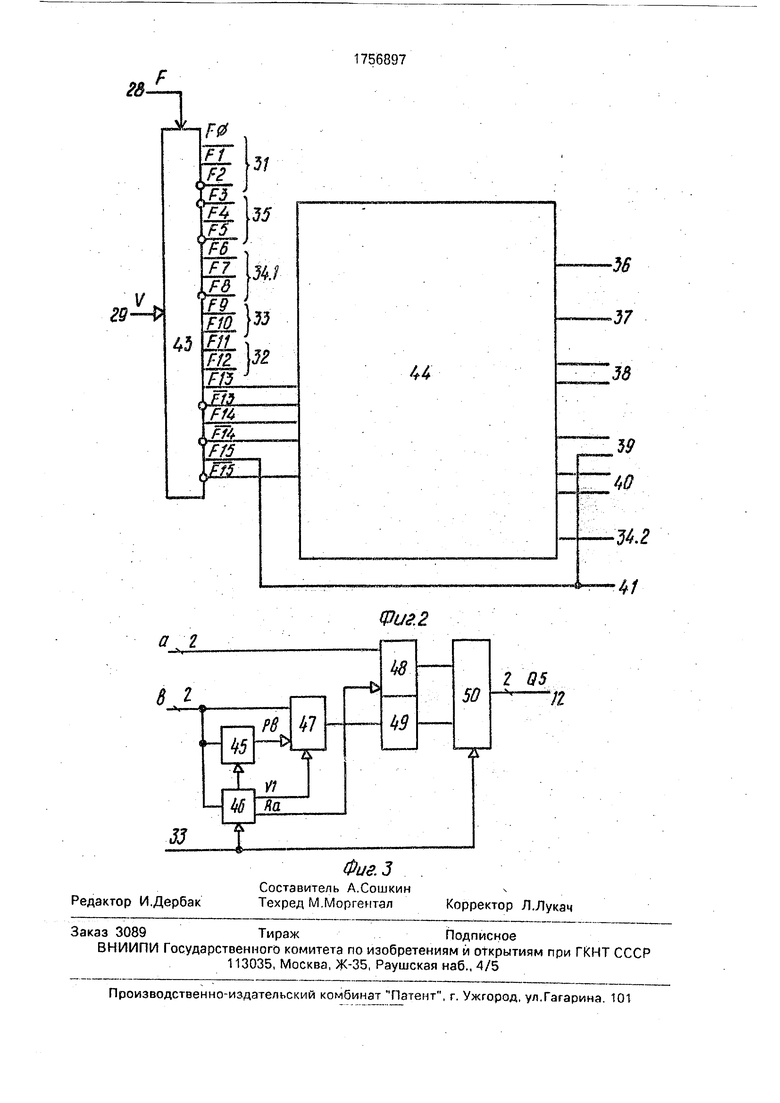

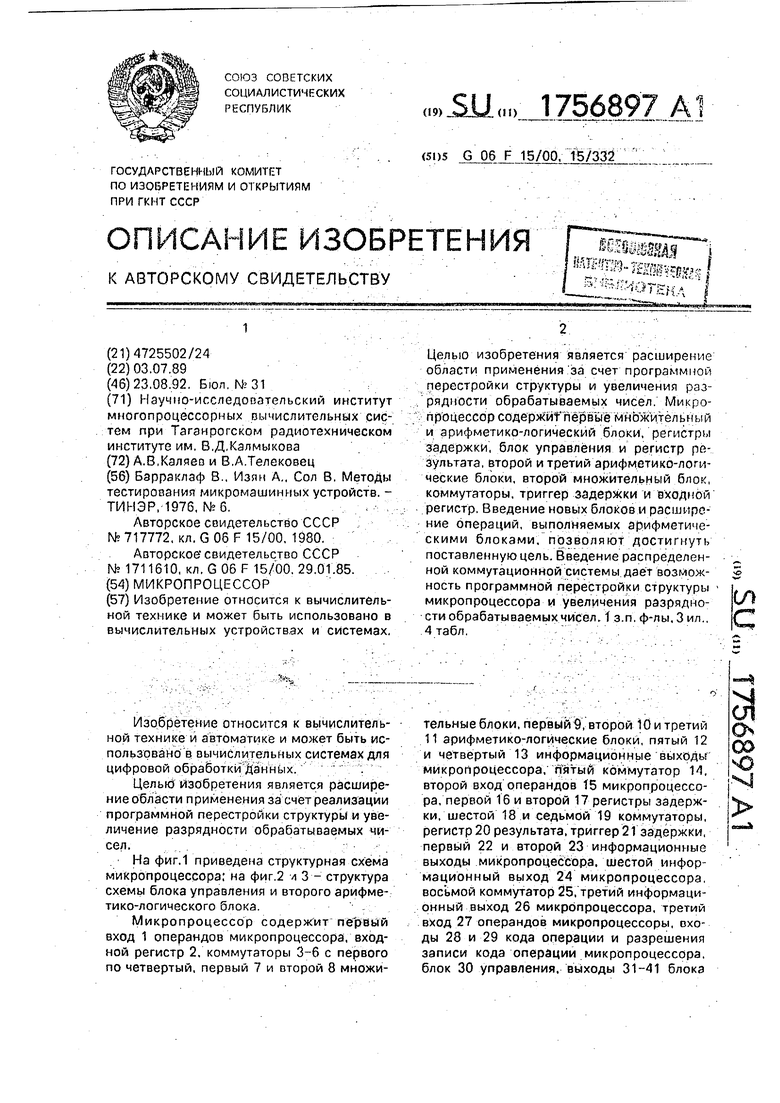

На фиг.1 приведена структурная схема микропроцессора: на фиг.2 л 3 - структура схемы блока управления и второго арифметико-логического блока.

Микропроцессор содержит первый вход 1 операндов микропроцессора, входной регистр 2, коммутаторы 3-6 с первого по четвертый, первый 7 и второй 8 множительные блоки, первый, второй 10 и третий 11 арифметико-логические блоки, пятый 12 и четвертый 13 информационные выходы микропроцессора, пятый коммутатор 14, второй вход операндов 15 микропроцессора, первой 16 и второй 17 регистры задержки, шестой 18 и седьмой 19 коммутаторы, регистр 20 результата, триггер 21 задержки, первый 22 и второй 23 информационные выходы микропроцессора, шестой информационный выход 24 микропроцессора, восьмой коммутатор 25, третий информационный выход 26 микропроцессора, третий вход 27 операндов микропроцессоры, охо- ды 28 и 29 кода операции и разрешения записи кода операции микропроцессора, блок 30 управления, выходы 31-41 блока

-т,

Я

управления, вход 42 синхронизации микропроцессора.

Блок 30 управления (фиг.2) содержит регистр 43 сдвига кода операции микропроцессора и дешифратор 44.

Второй арифметико-логический блок 15 (фиг.3) содержит первый 45 и второй 46 формирователи управляющих сигналов, коммутатор 47, регистры первого 48 и второго 49 операндов и последовательный сум- матор 5 в избыточной двоичной системе счисления.

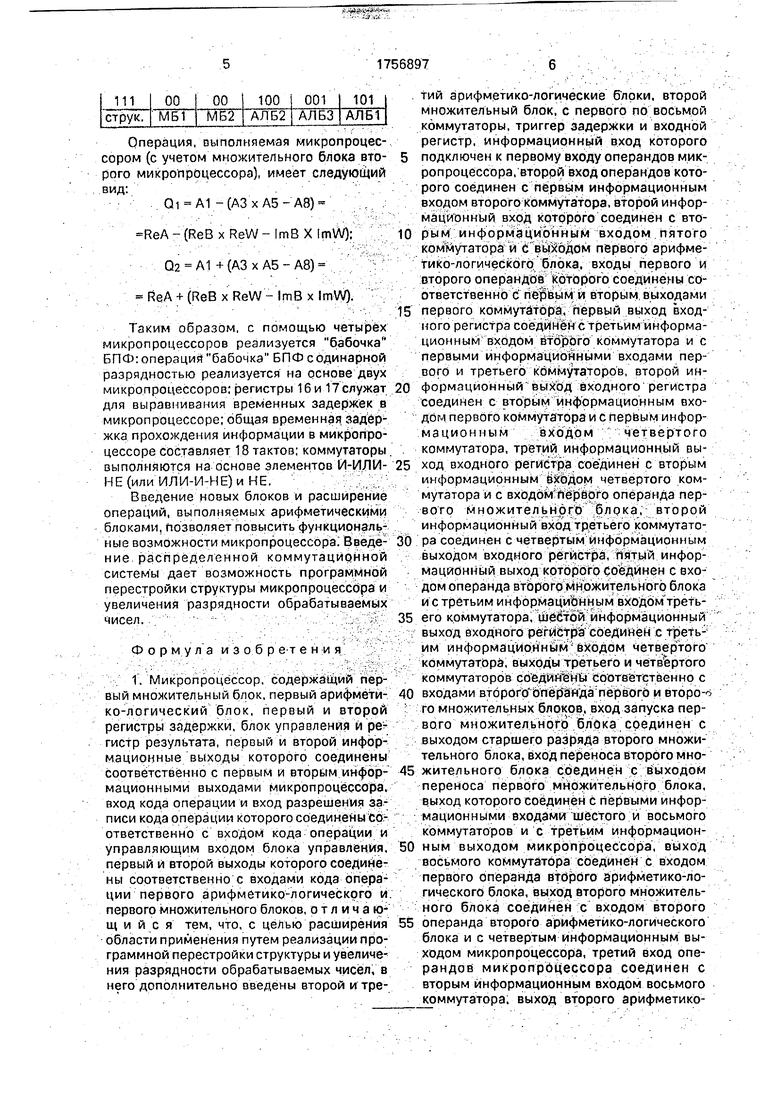

Выполнение любой из макроопераций в микропроцессоре задается кодом операции, который заносится в регистр 43 блока 30 управления последовательным кодом с входа 28 микропроцессора. Запись кода операции осуществляется по импульсам записи (шестнадцать импульсов), которые поступают на вход 29 микропроцессора. Тринадцать младших разрядов кода операции (F0-Fi2) содержат коды операций арифметико-логических блоков и блоков умножения, а три старших разрядов (Fi3- FIS) содержат код коммутации информаци- онных входов блоков микропроцессора, т.е. определяют структуру микропроцессора (табл.1).

Сигналы кодов операций подаются с выходов регистра 43 блока 30 управления на входы 31-41. Первый 9 и третий 11 арифметико-логические блоки идентичны и имеют одинаковые коды операций (F0-F2 для блока 9 и для блока 11). Множительные блоки 7 и 8 также идентичны и имеют одинаковые коды операций (Fg, Рю для блока 8 и Fn, Fi2 для блока 7). Коды операций этих блоков приведены в табл.2.

Второй арифметико-логический блок 10 отличается от первого 9 и третьего 11 ариф- метико-логического блоков алгоритмом выполнения логических операций (Мах и Min), которые выполняются совместно с множительными блоками 7 и 8. Коды арифметическихоперацийвторогоарифметико-логического блока 10 приведены в табл.3.

Коды логических операций второго арифметико-логического блока 10 приведены в табл.4.

Пример выполнения макроопераций.

При нулевых значениях F0-Fi2 выполняется следующая мзкрооперация микропроцессора:

Q1 А1 + А2; Q2 (А1 + А2) + (A3 х А4) +

-KAS х Аб).

При F4 - 1 и остальных пулевых значениях FO - Fa, Fs - Fi2 получают:

Q1 . А1 + А2; Q2 A3 х А4 + А х Аб.

Выполнение макрооперации приближенного вычисления модуля комплексного числа рассматривают по формуле:

IDI Max |ReDU mDl +1/2Min iReDl , I ImDI

Максимум двух чисел вычисляется в первом АЛБ9 (F0 FI 1, Fa - 0), а минимум вычисляется с помощью первого 7 и второго 8 множительных блоков второго АЛБ10 (операция 1/2 Min при FG F FB 1). Первый множительный блок 7 выдает значение у1 А3 IReDl (операция А ь О при FH 1 и Fi2 0), а второй множительный блок 8 выдает разность у2 As - Ае I ReD |-ilrnDf (операция А-В при Fg Fto 1) реальной и мнимой частей комплексного числа. В формирователе 45 (Фиг.З) второго АЛБ10 выделяется знак разности (S) и формируется сигнал (Rb) запирания входов второго операнда (о) второго АЛБ10 в коммутаторе 47

В зависимости от знака разности (S) коммутатор 47 выдает значение второго операнда АЛ Б (Ь), равное нулю (Ь О при у2 0) или значению разности с от рицатель- ным знаком (Ь -у2 при у2 0). Отрицательный знак второго операнда получается путем коммутации шин положительных (Ь4) и отрицательных (Ь) значений в коммутаторе 47.

Таким образом, при |ReD| llmDI результат второго АЛБ10 равен:

-(IReDl)- MmD|)

1/2 llmDI 1/2 ReDl , ImDI .

При iReDl MmDf второй операнд АЛБ15 имеет нулевое значение (запирается в коммутаторе 47) и поэтому результат равен:С 1/2 IReDl 1/2 Min IReDl , llmDI.

Коэффициент 1/2 задается управляющим входом F8 1 (масштабирование) коммутатора 47.

Код макрооперации (А) имеет следующий формат:

Объединяя два микропроцессора путем соединения выхода 13 (Q4) одного микропроцессора с входом 27 (А8) другого микропроцессора, можно получить сумматор произведений с удвоенной разрядностью чисел (полубабочку) БПФ. При этом формат кода макрооперации каждого из микропроцессоров имеет вид:

Операция, выполняемая микропроцессором (с учетом множительного блока второго микропроцессора), имеет следующий вид:

Ql A1 -(АЗх А5-А8)

ReA - (ReB x ReW - ImB X ImW):

Q2 - A1 + (A3 x A5 - A8) ReA + (ReB x ReW - ImB x ImW).

Таким образом, с помощью четырех микропроцессоров реализуется бабочка БПФ: операций бабочка БПФ с одинарной разрядностью реализуется на основе двух микропроцессоров: регистры 16 и 17 служат для выравнивания временных задержек в микропроцессоре; общая временная задержка прохождения информации в микропроцессоре составляет 18 тактов; коммутаторы выполняются на основе элементов И-ИЛИ- НЕ (или ИЛИ-1/l-HE) и НЕ.

Введение новых блоков и расширение операций, выполняемых арифметическими блоками, позволяет повысить функциональные возможности микропроцессора. Введение распределенной коммутационной системы дает возможность программной перестройки структуры микропроцессора и увеличения разрядности обрабатываемых чисел.

Формула изобретения

1, Микропроцессор, содержащий первый множительный блок, первый арифметико-логический блок, первый и второй регистры задержки, блок управления и регистр результата, первый и второй информационные выходы которого соединены соответственно с первым и вторым информационными выходами микропроцессора, вход кода операции и вход разрешения записи кода операции которого соединены соответственно с входом кода операции и управляющим входом блока управления, первый и второй выходы которого соединены соответственно с входами кода операции первого арифметико-логического и первого множительного блоков, отличающийся тем, что, с целью расширения области применения путем реализации программной перестройки структуры и увеличения разрядности обрабатываемых чисел, в него дополнительно введены второй и третий арифметико-логические блоки, второй множительный блок, с первого по восьмой коммутаторы, триггер задержки и входной регистр, информационный вход которого

5 подключен к первому входу операндов микропроцессора, второй вход операндов которого соединен с первым информационным входом второго коммутатора, второй информационный вход которого соединен с вто0 рым информационным входом пятого коммутатора и с выходом первого арифметико-логического блока, входы первого и второго операндов которого соединены соответственно с первым и вторым выходами

5 первого коммутатора, первый выход входного регистра соединен с третьим информационным входом второго коммутатора и с первыми информационными входами первого и третьего коммутаторов, второй ин0 формационный выход входного регистра соединен с вторым информационным входом первого коммутатора и с первым инфор- мациониым входом четвертого коммутатора, третий информационный вы5 ход входного регистра соединен с вторым информационным входом четвертого коммутатора и с входом первого операнда первого множительного блока, второй информационный вход третьего коммутато0 ра соединен с четвертым информационным выходом входного регистра, пятый информационный выход которого соединен с входом операнда второго множительного блока и с третьим информационным входомЧреть5 его коммутатора, шестой информационный выход входного регистра соединен с третьим информационным ЁХОДОМ четвертого коммутатора, выходы третьего и четвертого коммутаторов соединены соответственно с

0 входами второго операнда первого и второ-о го множительных блоков, вход запуска первого множительного блока соединен с выходом старшего разряда второго множительного блока, вход переноса второго мно5 жительного блока соединен с выходом переноса первого множительного блока, выход которого соединен с первыми информационными входами шестого и восьмого коммутаторов и с третьим информацион0 ным выходом микропроцессора, выход восьмого коммутатора соединен с входом первого операнда второго арифметико-логического блока, выход второго множительного блока соединен с входом второго

5 операнда второго арифметико-логического блока и с четвертым информационным выходом микропроцессора, третий вход операндов микропроцессора соединен с вторым информационным входом восьмого коммутатора, выход второго арифметикелогического блока соединен с третьим информационным входом первого коммутатора, с входом первого операнда третьего арифметико-логического блока и с пятым информационным выходом микропроцессо- ра, вход второго операнда третьего арифметико-логического блока соединен с выходом седьмого коммутатора, выход третьего арифметико-логического блока соединен с первым информационным входом регистра результата, второй информационный вход которого соединен с выходом пятого комму- татора, выход второгб регистра задержки соединен с первыми информационными входами пятого и седьмого коммутаторов и с четвертым информационным входом первого коммутатора, вход второго регистра задержки подключен к выходу шестого коммутатора, первый выход первого регистра задержки соединен с вторым информа- ционным входом шестого коммутатора, выход второго коммутатора соединен с информационным входом первого регистра задержки, второй выход которого подключен к второму информационному входу седьмого коммутатора, третий информационный вход которою соединен с шестым выходом микропроцессора и с выходом триггера задержки, информационный вход которого подключен к первому выходу реги- стра результата, входы кода операций второго множительного блока, второго и третьего арифметико-логических блоков и управляющие входы с первого по восьмой коммутаторов соединены соответственно с третьего по одиннадцатый выходами блока управления, вход синхронизации микропроцессора соединен с входами синхронизации входного регистра, с первого по третий арифметико-логических блоков, первого и второго множительных блоков, первого и второго регистров задержки, регистра результата и триггера задержки.

2. Микропроцессор по п. 1, от л и ч а ю- щ и и с я тем, что блок управления содержит регистр сдвига и дешифратор, причем информационный и управляющий входы блока подключены соответственно к информационному входу м входу синхронизации регистра сдвига, выходы с первого по пятое полей местного управления которого соединены соответственно с первого по пятый выходами блока, выход шестого поля местного управления регистра сдвига соединен с входом дешифратора, выходы с первого по пятый которого подключены соответственно к выходам с шестого по десятый блока, выход седьмого поля местного управления сдвигового регистра подключен к один над цатому выходу блока, шестой выход дешифратора подключен к четвертому выходу блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Микропроцессор | 1977 |

|

SU717772A1 |

| МНОГОПРОЦЕССОРНАЯ ВЕКТОРНАЯ ЭВМ | 1995 |

|

RU2113010C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЙ | 1991 |

|

RU2006929C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Микропроцессор | 1979 |

|

SU894715A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системах. Целью изобретения является расширение области применения за счет программной перестройки структуры и увеличения разрядности обрабатываемых чисел. Микропроцессор содержит первые множительный и арифметико-логический блоки, регистры задержки, блок управления и регистр результата, второй и третий арифметико-логические блоки, второй множительный блок, коммутаторы, триггер задержки и входной регистр. Введение новых блоков и расширение операций, выполняемых арифметическими блоками, позволяют достигнуть поставленную цель. Введение распределенной коммутационной системы дает возможность программной перестройки структуры микропроцессора и увеличения разрядности обрабатываемых чисел, t з.п. ф-лы,3ил.. 4 табл. (Л

Таблица 1

1756897

.

в™ р ™в вив«1 «-1 « «« й« вив«вввв™1 «

F3 F7 F6 J °перация F5 F; Fg I Операция

О О А+В1

0 1 A-B1

1 0 0+B1

О О 1/2(A+B)

0f 1/2(A-B)

10 1/2(0+B)

Min

K,

Vt

. Знак b

Операция

0 1 1 1

ъ o

b 0 b 0 b-c 0

1

A-B /Ч-В

1/2(A-B) 1 1/2(A+0)

10

I-2JLЈ y...a..3Lji.

Max

1C5 F,3 Fv F6 Знак Ь 0пеРаЦия

01

11

b 0

b4 0

b 0 b 0

A+B Л+В

1/2(Л4-В) 1/2(A-fO)

Фиг.2

| Барраклаф В , Излк А., Сол В | |||

| Методы тестирования микромашинных устройств | |||

| - ТИНЭР, 1976, №6 | |||

| Микропроцессор | 1977 |

|

SU717772A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1711610, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1992-08-23—Публикация

1989-07-03—Подача