соединены с соответствуницими управляющими вхсщами коммутатора, а выходы - подключены к входам „соответствую щих элементов ИЛИ блока элементов ИЛИ, выходы которых соединены с первыми входами соответствующих элемен.тов И блока элементов И, вторые входи которых соединены с синхронизируюmfiM входом ко№1утатора, а выходы - с соответствующими выходами коммутатора

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство определения конца блока циклического кода | 1982 |

|

SU1061279A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для декодирования сверточного кода | 1989 |

|

SU1725400A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

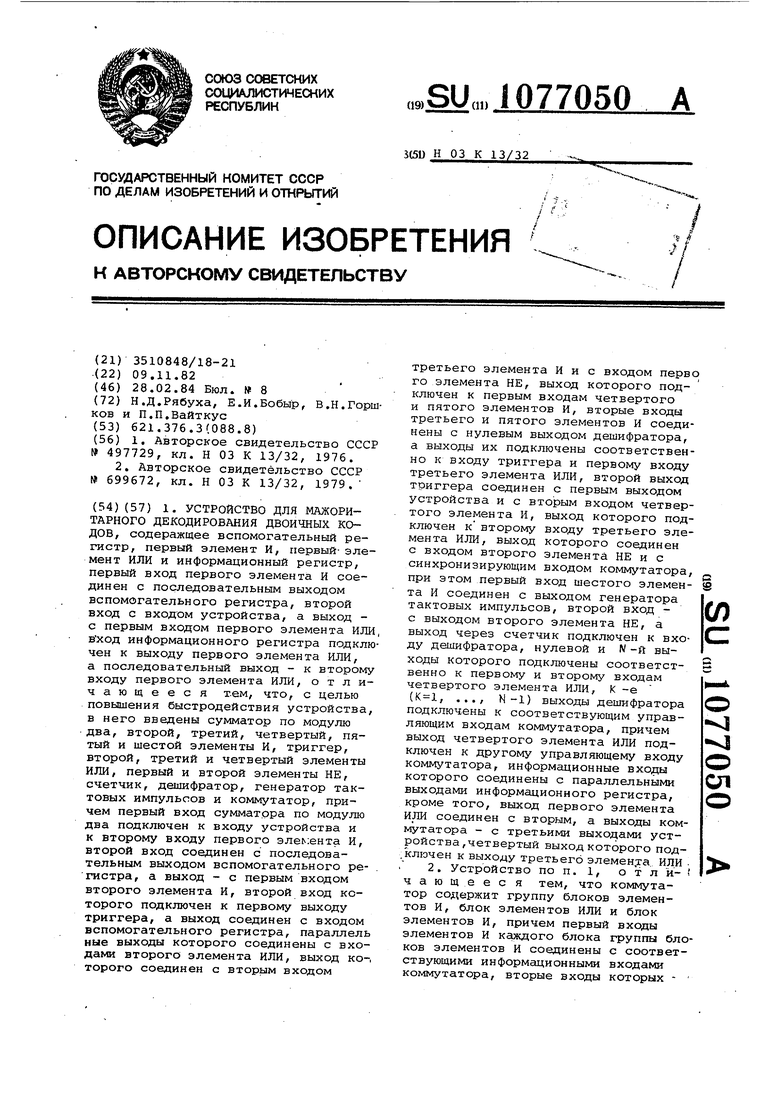

1. УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ДЕКОДИРОВАНИЯ ДВОИЧНЫХ КОДОВ, содеражщее вспомогательный регистр, первый элемент И, первый- элемент ИЛИ и информационный регистр, первый вход первого элемента И соединен с последовательным выходом вспомогательного регистра, второй вход с входом устройства, а выход с первым входом первого элемента ИЛИ, вход информационного регистра подключен к выходу первого элемента ИЛИ, а последовательный выход - к второму входу первого элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены сумматор по модулю два, второй, третий, четвертый, пятый и шестой элементы И, триггер, второй, третий и четвертый элементы ИЛИ, первый и второй элементы НЕ, счетчик, дешифратор, генератор тактовых импульсов и коммутатор, причем первый вход сумматора по модулю два подключен к входу устройства и к второму входу первого элеь:ента И, второй вход соединен с последовательным выходом вспомогательного регистра, а выход - с первым входом второго элемента И, второй вход которого подключен к первому выходу триггера, а выход соединен с входом вспомогательного регистра, параллель ные выходы которого соединены с входами второго элемента ИЛИ, выход ко-, торого соединен с вторым входом третьего элемента И и с входом перво го элемента НЕ, выход которого подключен к первым входам четвертого и пятого элементов И, вторые входы третьего и пятого элементов И соединены с нулевым выходом дешифратора, а выходы их подключены соответственно к входу триггера и первому входу третьего элемента ИЛИ, второй выход триггера соединен с первым выходом устройства и с вторым входом четвертого элемента И, выход которого подключен к второму входу третьего элемента ИЛИ, выход которого соединен с входом второго элемента НЕ и с синхронизирующим входом коммутатора, при этом первый вход шестого элеменS та И соединен с выходом генератора (Л тактовых импульсов, второй вход с выходом второго элемента НЕ, а выход через счетчик подключен к входу дешифратора, нулевой и N-ft выходы которого подключены соответственно к первому и второму входам четвертого элемента ИЛИ, К -е (, ..., N-1) выходы дешифратора подключены к соответствующим управ-J ляющим входам коммутатора, причем выход четвертого элемента ИЛИ подключен к другому управляющему входу о коммутатора, информационные входы О1 которого соединены с параллельными выходами информационного регистра, кроме того, выход первого элемента ИЛИ соединен с вторым, а выходы коммутатора - с третьими выходами устройства,четвертый выход которого под.ключен к выходу третьего элемен.та ИЛИ . 2. Устройство по п. 1, о т л ичающеес я тем, что коммутатор содержит группу блоков элементов И, блок элементов ИЛИ и блок элементов И, причем первый входы элементов И каждого блока группы блоков элементов И соединены с соответствующими информационными входами ко1чмутатора, вторые входы которых

Изобретение относится к телемеханике, технике связи и вычислительной технике и- может быть использовано в системах передачи и хранения данных для декодирования двоичных кодов.

Известно устройство для мажоритарного декодирования двоичных кодов, содержащее вспомогательный регистр, мажоритарный элемент, элемент И, элемент ИЛИ и информационный регистр (1 Однако наличие в известном ус ройстве мажоритарного элемента, требующего трехкратного повторения информации, снижает его быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для мажоритарного декодирования двоичных кодов, содержащее вспомогательный регистр, первый элемент И, первый элемент ИЛИ и информационный регистр, первый вход перво о элемента И соединен с последр зтельным выходом вспомогательного, регистра, второй вход с входом устройства, а выход - с первым входом первого элемен.та ИЛИ, вход информационного регистра подключен к выходу первого элемента ИЛИ, а последовательный выход - к второму входу первого элемента ИЛИ 2.

Недостатком данного устройства является низкое быстродействие, обусловленное необходимостью трехкратного повторения.

Цель изобретения - повышение быстродействия.

Указанная цель достигается тем, что в устройство для мажоритарного декодирования двоичных кодов, содержащее вспомогательный регистр, первый элемент И, первый элемент ИЛИ и информационный регистр, первый вход первого элемента И соединен с последовательным выходом вспомогательного регистра, второй вход с входом устройства, а выход - с первым входом первого элемента ИЛИ, вход информационного регистра подключен к выходу первого элемента ИЛИ, а последовательный выход - к второму входу первого элемента ИЛИ, введены сумматор по модулю два, второй, третий, четвертый, пятый и шестой элементы И триггер, второй, третий и четвертый элементы ИЛИ, первый и второй элементы НЕ, счетчик, дешифратор, генератор тактовых импульсов и коммутатор, причем первый вход сумматора по модулю Два подключен к входу устройства, и к второму входу первого элемента И, второй вход соединен с последовательным выходом вспомогательного регистра, а выход - с первым входом второго элемента И, второй вход которого подключен к первому выходу триггера, а выход соединен с входом вспомогательного регист ра, параллельные выходы которого соединены с вxoдaгvШ второго элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И и с входом первого элемента НЕ, выхоц которого подключен к первым входам четвертого и пятого элементов И, вторые входы третьего и пятого элементов И соединены с нулевым выходом дешифратора, а выходы их подключены соответственно к входу триггера и первому входу третьего элемента ИЛИ, второй выход триггера соединен с первым выходом устройства и с вторым входом четвертого элемента И, выход которого подключен к второму входу третьего элемента ИЛИ, выход которого соединен с входом второго элемента НЕ и с синхронизирующим входом коммутатора, при этом первый вход шестого элемента И соединен с выходом генератора тактовых импульсов, второй вход с выходом второго элемента НЕ, а выход - -через счетчик подключен к входу дешифратора, нулевой и N-й выходы которого подключены соответственно к первому и второму входам четвертого элемента ИЛИ, К-е (,..., N-1) выходы дешифратора подключены к соответствующим управляющим входам коммутатора, причем выход четвертого элемента ИЛИ подключен к другому управляющему входу коммутатора, информационные входы которого соединены с парашлельными выходами информационного регистра, кроме того, выход первого элемента ИЛИ соединен с вторьом, а выходы коммутатора - с третьими выходами устро ства, четвертый выход которого под; ключен к выходу третьего Элемента ИЛИ. Коммутатор содержит группу блоков элементов И, блок элементов ИЛИ и

блок элементов И, причем первые входы элементов И. каждого блока группы блоков элементов И соединены с соответствующими информационными вх дами коммутатора, вторые входы которых соединены с соответствующими управляющими входами коммутатора, а выходы подключены к входам соотве ствующих элементов ИЛИ блока элементов ИЛИ, выходы которых соединены с первыми входами соответствующих элементов и блока элементов И, вторые входы которых соединены с синхронизирующим входом коммутатора, а выходы - с соответствующими выходами коммутатора.

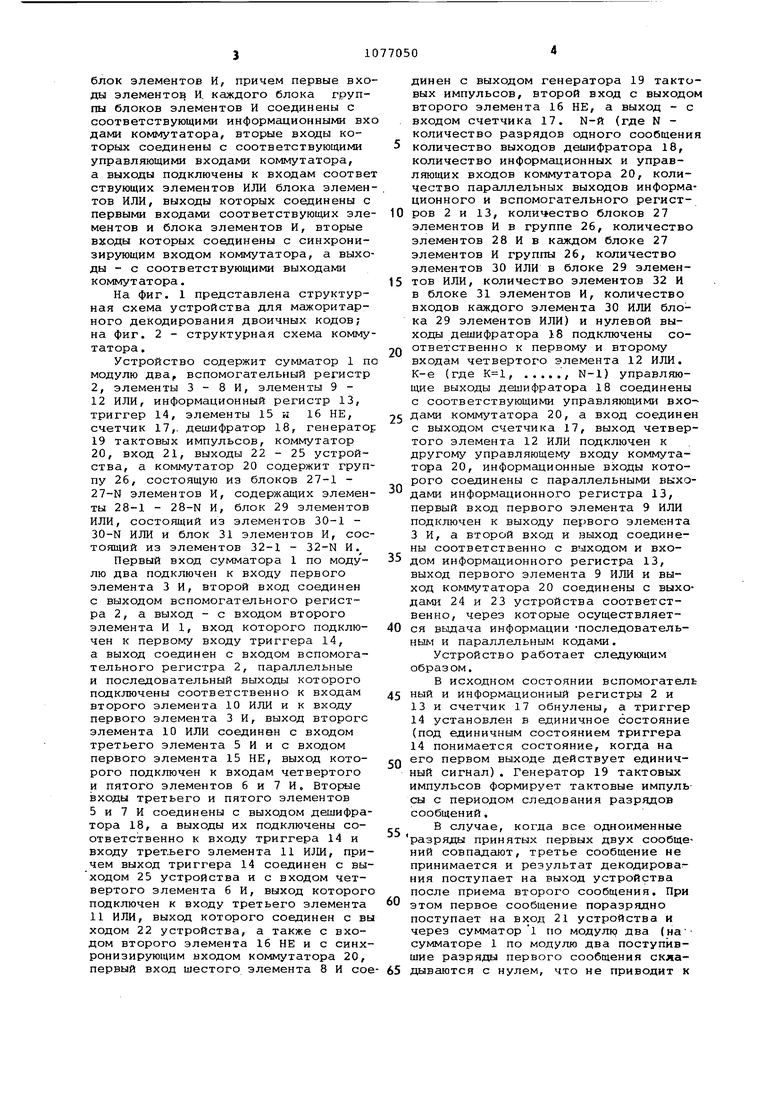

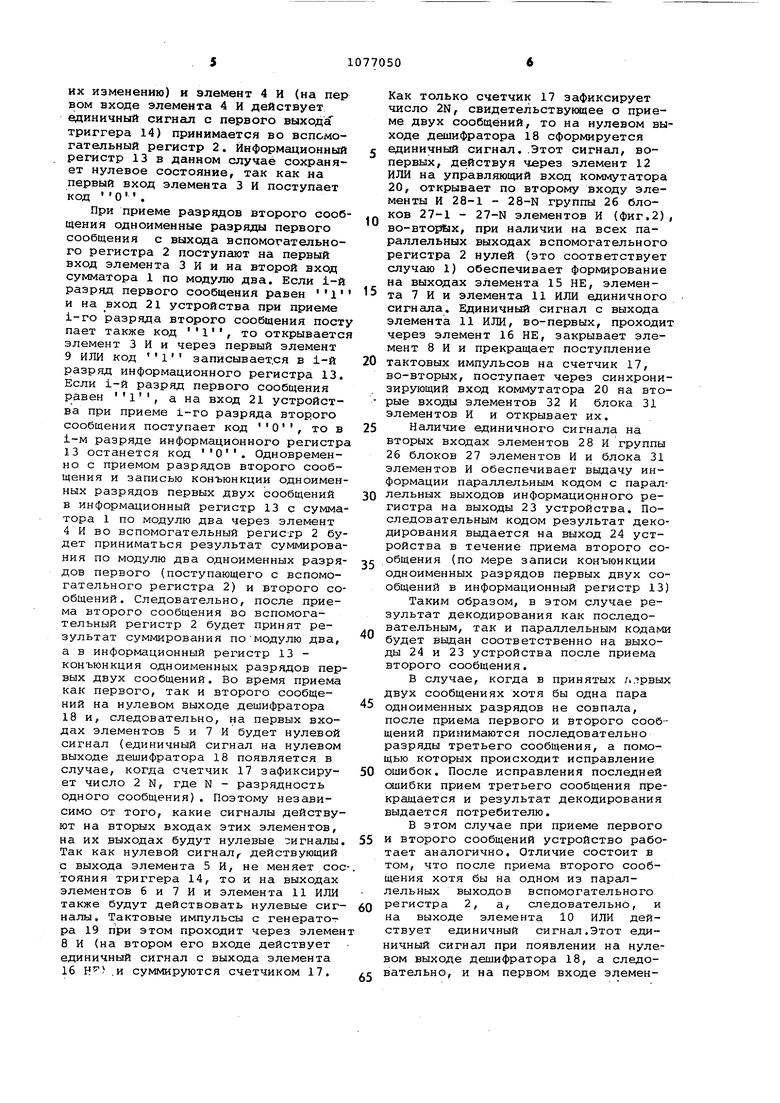

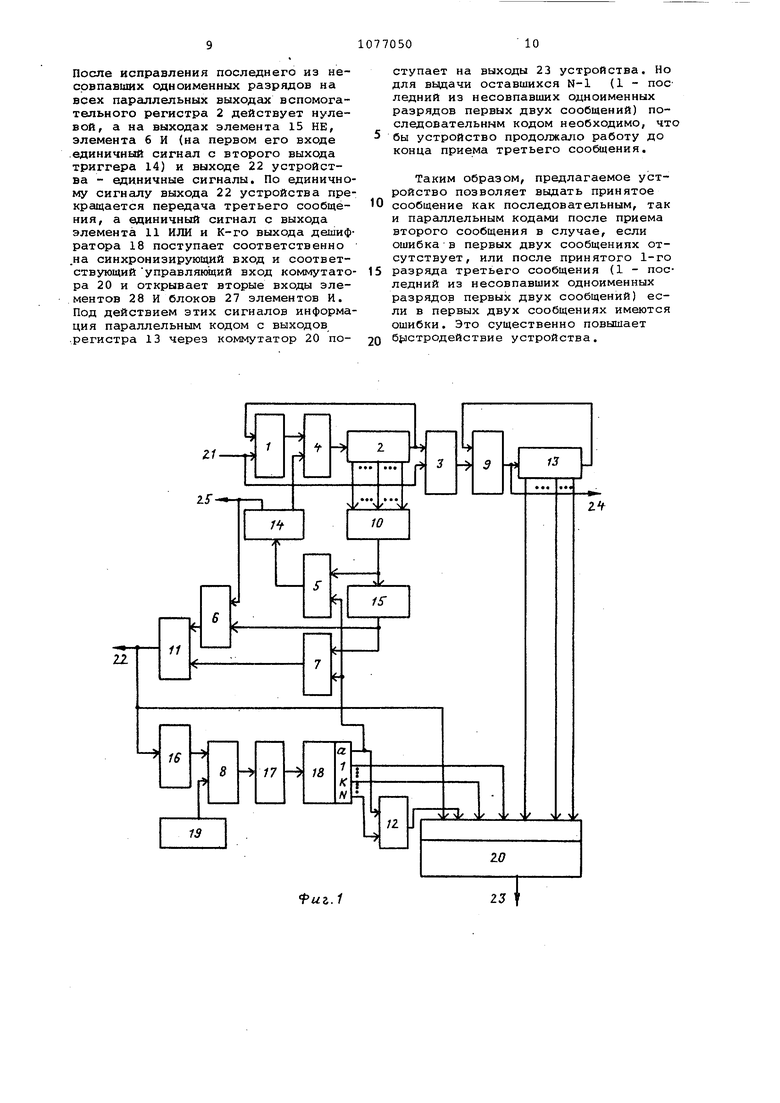

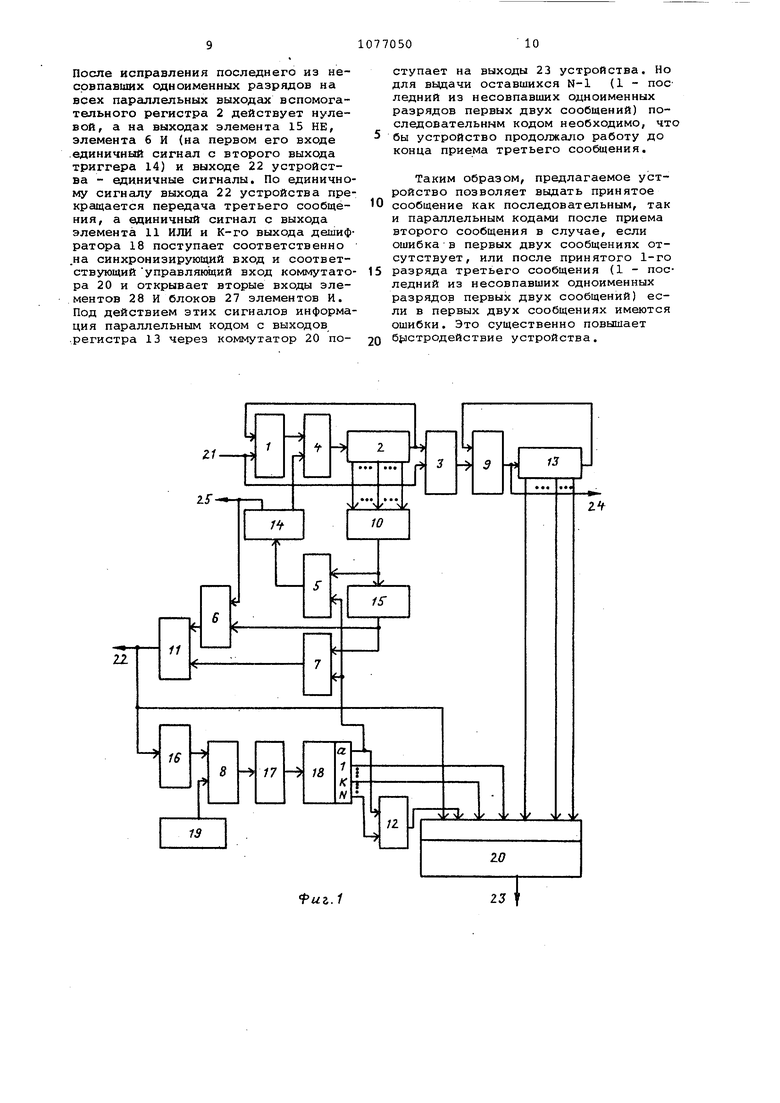

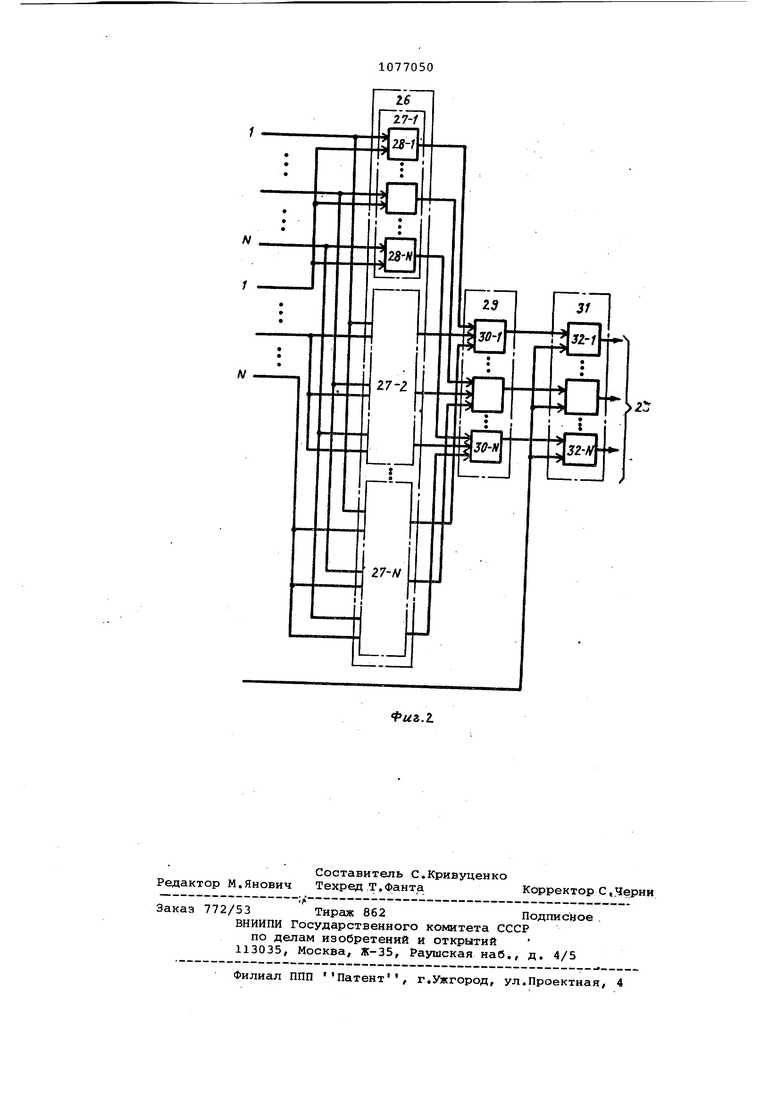

На фиг. 1 представлена структурная схема устройства для мажоритарного декодирования двоичных кодов; на фиг. 2 - структурная схема коммутатора .

Устройство содержит сумматор 1 п модулю два, вспомогательный регистр 2, элементы 3 - 8 И, элементы 9 12 ИЛИ, информационный регистр 13, триггер 14, элементы 15 ы 16 НЕ, счетчик 17,. дешифратор 18, генерато 19 тактовых импульсов, коммутатор 20, вход 21, выходы 22 - 25 устройства, а коммутатор 20 содержит группу 26, состоящую из блоков 27-1 27-N элементов И, содержащих элементы 28-1 - 28-N И, блок 29 элементов ИЛИ, состоящий из элементов 30-1 30-N ИЛИ и блок 31 элементов И, состоящий из элементов 32-1 - 32-N И .

Первый вход сумматора 1 по модулю два подключе к входу первого элемента 3 И, второй вход соединен с выходом вспомогательного регистра 2, а выход - с входом второго элемента И 1, вход которого подключен к первому входу триггера 14, а выход соединен с входом вспомогательного регистра 2, параллельные и последовательный выходы которого подключены соответственно к входам второго элемента 10 ИЛИ и к входу первого элемента 3 И, выход второго элемента 10 ИЛИ соединен с входом третьего элемента 5 И и с входом первого элемента 15 НЕ, выход которого подключен к входам четвертого и пятого элементов 6 и 7 И. Вторие входы третьего и пятого элементов 5 и 7 И соединены с выходом дешифратора 18, а выходы их подключены соответственно к входу триггера 14 и входу трет.ьего элемента 11 ШШ, причем выход триггера 14 соединен с выходом 25 устройства и с входом четвертого элемента 6 И, выход которого подключен к входу третьего элемента 11 ИЛИ, выход которого соединен с вы ходом 22 устройства, а также с входом второго элемента 16 НЕ и с синхронизирующим входом коммутатора 20, первый вход шестого элемента 8 И соединен с выходом генератора 19 тактовых импульсов, второй вход с выходо второго элемента 16 НЕ, а выход - с входом счетчика 17. N-й (где N количество разрядов одного сообщени количество выходов дешифратора 18, количество информационных и управляющих входов коммутатора 20, количество параллельных выходов информационного и вспомогательного регистров 2 и 13, количество блоков 27 элементов И в группе 26, количество элементов 28 И в каждом блоке 27 элементов И группы 26, количество элементов 30 ИЛИ в блоке 29 элементов ИЛИ, количество элементов 32 И в блоке 31 элементов И, количество входов каждого элемента 30 ИЛИ блока 29 элементов ИЛИ) и нулевой выходы дешифратора 18 подключены соответственно к первому и второму входам четвертого элемента 12 ИЛИ. К-е (где , , N-1) управляющие выходы дешифратора 18 соединены с соответствующими управляющими входами коммутатора 20, а вход соедине с выходом счетчика 17, выход четвертого элемента 12 ИЛИ подключен к другому управляющему входу коммутатора 20, информационные входы которого соединены с параллельными выходами информационного регистра 13, первый вход первого элемента 9 ИЛИ подключен к выходу первого элемента 3 И, а второй вход и выход соединены соответственно с выходом и входом информационного регистра 13, выход первого элемента 9 ИЛИ и выход коммутатора 20 соединены с выходами 24 и 23 устройства соответственно, через которые осуществляется выдача информации -последовательным и параллельным кодами.

Устройство работает следующим образом.

В исходном состоянии вспомогател ный и информационный регистры 2 и

13и счетчик 17 обнулены, а триггер

14установлен в единичное состояние (под единичным состоянием триггера 14 понимается состояние, когда на его первом выходе действует единичный сигнал). Генератор 19 тактовых импульсов формирует тактовые импульсы с периодом следования разрядов сообщений.

В случае, когда все одноименные разряды принятых первых двух сообщений совпадают, третье сообщение не принимается и результат декодирования поступает на выход устройства после приема второго сообщения. При этом первое сообщение поразрядно поступает на вход 21 устройства и через сумматор l по модулк два (насумматоре 1 по модулю два поступившие разряды первого сообщения складываются с нулем, что не приводит к

их изменению) и элемент 4 И (на пер вом входе элемента 4 И действует единичный сигнал с первого выход триггера 14) принимается во вспомогательный регистр 2. Информационный регистр 13 в данном случае сохраняет нулевое состояние, так как на первый вход элемента 3 И поступает код О ,

При приеме разрядов второго сообщения одноименные разряды первого сообщения с выхсада вспомогательного регистра 2 поступают на первый вход элемента 3 И и на второй вход сумматора 1 по модулю два. Если i-й разряд первого сообщения равен i и на вход 21 устройства при приеме i-ro разряда второго сообщения посту пает также код 1, то открывается элемент 3 И и через первый элемент 9 ИЛИ код 1 записывается в 1-й разряд информационного регистра 13. Если i-й разряд первого сообщения равен Ч, а на вход 21 устройства при приеме i-ro разряда второго сообщения поступает код О, то в 1-м разряде информационного регистра 13 останется код . Одновременно с приемом разрядов второго сообщения и записью конъюнкции одноименных разрядов первых двух сообщений в информационный регистр 13 с сумматора 1 по модулю два через элемент 4 И во вспомогательный регистр 2 будет приниматься результат суммирования по модулю два одноименных разрядов первого (поступающего с вспомогательного регистра 2) и второго сообщений. Следовательно, после приема второго сообщения во вспомогательный регистр 2 будет принят результат суммирования помодулю два, а в информационный регистр 13 конъюнкция одноименных разрядов первых двух сообщений. Во время приема как первого, так и второго сообщений на нулевом выходе дешифратора 18 и, следовательно, на первых входах элементов 5 и 7 И будет нулевой сигнал (единичный сигнал на нулевом выходе дешифратора 18 появляется в случае, когда счетчик 17 зафиксирует число 2 N, где N - разрядность одного сообщения). Поэтому независимо от того, какие сигналы действуют на вторых входах этих элементов, на их выходах будут нулевые ::игналы. Так как нулевой сигнал, действующий С выхода элемента 5 И, не меняет сое тояния триггера 14, то и на выходах элементов б и 7 И и элемента 11 ИЛИ также будут действовать нулевые сигналы. Тактовые импульсы с генератора 19 при этом проходит через элемен 8 И (на втором его входе действует единичный сигнал с выхода элемента 16 Н ,и суммируются счетчиком 17.

Как только счетчик 17 зафиксирует число 2N, свидетельствующее о приеме двух сообщений, то на нулевом выходе дешифратора 18 сформируется единичный сигнал,.Этот сигнал, вопервых, действуя через элемент 12 ИЛИ на управляющий вход коммутатора 20, открывает по второму входу элементы И 28-1 - 28-N группы 26 блоков 27-1 - 27-N элементов И (фиг.2) во-вторйх, при наличии на всех параллельных выходах вспомогательного регистра 2 нулей (это соответствует случаю 1) обеспечивает формирование на выходах элемента 15 НЕ, элемента 7 И и элемента 11 ИЛИ единичного сигнала. Единичный сигнал с выхода элемента 11 ИЛИ, во-первых, проходит через элемент 16 НЕ, закрывает элемент 8 И и прекращает поступление тактовых импульсов на счетчик 17, во-вторых, поступает через синхронизирующий вход коммутатора 20 на вторые входы элементов 32 И блока 31 элементов И и открывает их.

Наличие единичного сигнала на вторых входах элементов 28 И группы 26 блоков 27 элементов И и блока 31 элементов И обеспечивает выдачу информации параллельным кодом с параллельных выходов информационного регистра на выходы 23 устройства. Последовательным кодом результат декодирования выдается на выход 24 устройства в течение приема второго сообщения (по мере записи конъюнкции одноименных разрядов первых двух сообщений в информационный регистр 13)

Таким образом, в этом случае результат декодирования как последовательным, так и параллельным кодами будет выдан соответственно на выходы 24 и 23 устройства после приема второго сообщения.

В случае, когда в принятых /.лрвых двух сообщениях хотя бы одна пара одноименных разрядов не совпала, после приема первого и второго сЬобщений принимаются последовательно разряды третьего сообщения, а помощью которых происходит исправление ошибок. После исправления последней сшибки прием третьего сообщения прекращается и результат декодирования выдается потребителю.

В этом случае при приеме первого и второго сообщений устройство работает аналогично. Отличие состоит в том, что после приема второго сообщения хотя бы на одном из параллельных выходов вспомогательного регистра 2, а, следовательно, и на выходе элемента 10 ИЛИ действует единичный сигнал.Этот единичный сигнал при появлении на нулевом выходе дешифратора 18, а следовательно, и на первом входе элемента 5 И разрешающего сигнала (разрешающий сигнал, появляется после того как счетчик 17 зафиксирует число 2N) проходит через элемент 5 И и устанавливает триггер 14 в нулевое состояние (в исходном состоянии три гер 14 находится в единичном состоя нии) . В результате этого закрывается элемент 4 И и на выходе 25 устройства (соответственно на первом входе элемента 6 И) формируется еди ничный сигнал, по которому на прием ной стороне стирается переданная последовательным кодом информация. Эта информация является неправильно так как i-e (, .../ N) одноименные разряды первого и второго сообщений не совпали (значения этих раз рядов будут определяться после прие ма i-x разрядов третьего сообщения по совпадению двух из трех одноимен ных разрядов трех сообщений). Кроме того, единичный сигнал с выхода эле мента 10 ИЛИ инвертируется элементом 15 НЕ и нулевой сигнал с его вы .хода закрывает элементы б и 7 И, в результате чего на выходе 22 уст;ройства, а следовательно, на синхро низирующем входе коммутатора 20 и входе элемента 16 НЕ действует нуле вой сигнал. Под действием нулевого сигнала на синхронизирующем входе закрываются вторые входы элементов 32 И блока 31 элементов И и информация с параллельных выходов регистра 13 не поступает на выходы 23 устройства. Под действием нулевого сигнала на входе элемента 16 НЕ на его выходе формируется единичный сигнал, который разрешает проходить тактовым импульсам с генератора 19 тактовых импульсов через элемент 8 И на счетчик 17, рде продолжается их суммирование. Третье сообщение поразрядно посту пает на вход сумматора 1 по модулю два и на вход элемента 3 И. На сумма торе 1 по модулю два происходит поразрядное суммирование третьего сообщения с содержимым вспомогательного регистра 2 (результатом поразрядного суммирования первых двух сообщений) без записи результата во вспомогательный регистр 2, так как-закрыт элемент 4 И. Пример.. Допустим первое и второе сообщение не совпали в j-м разряде. Это значит, что в j-м разряде вспомогательного регистра 2 имеется единица. При приеме i-x разрядов третьего сообщения (i j ) на выходе вспомогательного регистра 2, а следовательно., и на первом входе элемента 3 И действует нулевой сигнал (это значит, что все i-e (i j) одноименные разряды первых двух сбоС щений совпали). На втором входе элемента 3 И в то же время будут i-e разряды третьего сообщения ( или 1 J . Наличие- нуля на первом входе элемента 3 И приводит к тому, что в течение поступления всех i-x (i j) разрядов третьего сообщения на первом входе элемента 9 ИЛИ тоже нулевой сигнал и, следовательно, в результате их дизъюнкции с одноименными i-ми (i j) разрядами информационного регистра 13 содержимое регистра 13 не изменяется. Счетчик 17 при этом фиксирует число 2N+i (i j) и на К-м выходе дешифратора, (K-i) появляется единичный сигнал. Этот сигкал поступает на управляющий вход коммутатора 20 и открывает его (т.е. открывает по второму входу элементы 28 И группы 26 блока блоков элементов И. Но в этом случае закрытым остается синхронизирующий вход коммутатора 20 (т.е. за.фыты элементы 32 И блока 31 элементов И), так как состояние остальных узлов устройства не меняется и на выходах 23 устройства будет нулевой сигнал. На выход 24 устройства при этом выдаются i-e (i j) разряды информационного регистра 13. При поступлении на вход 21 устрой ство j-ro () разряда третьего сообщения, на выходе вспомогательного регистра. 2 действует единичный сигнал (так как первые два сообщения в j-м разряде не совпали). Если в этом случае j-й разряд третьего сообщения равен Ч, то она проходит через элемент 3 И и в результате дизъюнкции с j-м разрядом содержимого информационного регистра 13 эта единица оказывается в j-м разряде 13 (в информационном регистре 13 в разрядах, номера которых соответствуют несовпавшим одноименным разрядам первых двух сообщений, хранятся нули). В-случае, если j-й разряд третьего сообщения равен , на выходе элемента 3 И действует нулевой сигнал и содержимое информационного регистра 13 остается неизменным. Таким образом, по значению j-ro разряда третьего сообщения и значению содержимого j-ro разряда информационного регистра 13 осуществляется коррекция j-ro разряда результата декодирования. В общем случае несовпавшими могут быть несколько одноименных разрядов первых двух сообщений (в вспомогательном реги.стре несколько единиц). Тогда аналогично рассмотрен ному осуществляется коррекция всех несовпайщих разрядов до исправления последнего из несовпавших одноИм нрых разрядов первых двух сообщения

После исправления последнего из несрвпавших одноименньлх разрядов на всех параллельных выходах вспомогательного регистра 2 действует нулевой, а на выходах элемента 15 НЕ, элемента 6 И (на первом его входе .единичный сигнал с второго выхода триггера 14) и выходе 22 устройства - единичные сигналы. По единичному сигналу выхода 22 устройства прекращается передача третьего сообщения, а единичный сигнал с выхода элемента 11 ИЛИ и К-го выхода дешифратора 18 поступает соответственно .на синхронизирующий вход и соответствующий управляющий вход коммутатора 20 и открывает вторые входы элементов 28 И блоков 27 элементов И. Под действием этих сигналов информация параллельным кодом с выходов .регистра 13 через коммутатор 20 .1

ступает на выходы 23 устройства. Но для вьщачи оставшихся N-1 (1 - пос ледний из несовпавших одноименных разрядов первых двух сообщений) последовательным кодом необходимо, что бы устройство продолжало работу до конца приема третьего сообщения.

Таким образом, предлагаемое устройство позволяет выдать принятое

сообщение как последовательным, так и параллельным кодами после приема второго сообщения в случае, если ошибка в первых двух сообщениях отсутствует, или после принятого 1-го

разряда третьего сообщения (1 - последний из несовпавших одноименных разрядов первых двух сообщений) если в первых двух сообщениях имеются ошибки. Это существенно повышает

б лстродействив устройства.

23

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для мажоритарного декадирования двоичных кодов | 1974 |

|

SU497729A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для мажоритарного декодирования двоичных кодов | 1978 |

|

SU699672A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-02-28—Публикация

1982-11-09—Подача