Изобретение относится к вычислительной технике и может найти применение в автоматических системах испытаний, контроля качества, определения категорий.

Известно устройство для определения категорий качества объектов, содержащее группу блоков задания показателей, две группы элементов И, n групп блоков сравнения, две группы элементов задержки [1].

Однако данное устройство не позволяет осуществлять контроль качества динамически изменяющихся процессов при случайном характере оценок измерений показателей качества.

Ближайшим по своей технической сущности и достигаемому эффекту является устройство для допускового контроля функциональных состояний технических систем, содержащее группу блоков памяти, дифференцирующий элемент, триггер, группу блоков сравнения, каждый из которых содержит регистры памяти, сумматоры, блоки элементов И, блок элементов ИЛИ, компаратор, инвертор, элемент ИЛИ, группу регистров памяти, группу элементов И [2].

Показатели качества исследуемых n систем определяются в любой момент времени с приходом запускающего сигнала и сравниваются с хранящимися значениями верхней Рi B и нижней Рi H границы допусков. Неоднозначность классификации ситуации при нахождении параметра на границе области значения частично устраняется расширением области допуска параметра на 3σ относительно верхней и нижней границы допуска. Тем самым уменьшается вероятность ошибочного признания объекта контроля (ОК) неисправным.

Недостатком рассматриваемого устройства является невозможность повышения эффективности контроля качества динамически изменяющихся процессов путем уменьшения вероятности ошибочного признания ОК исправным (снижения риска заказчика).

Цель изобретения - создание устройства для допускового контроля функциональных состояний технических систем с расширенным классом решаемых задач.

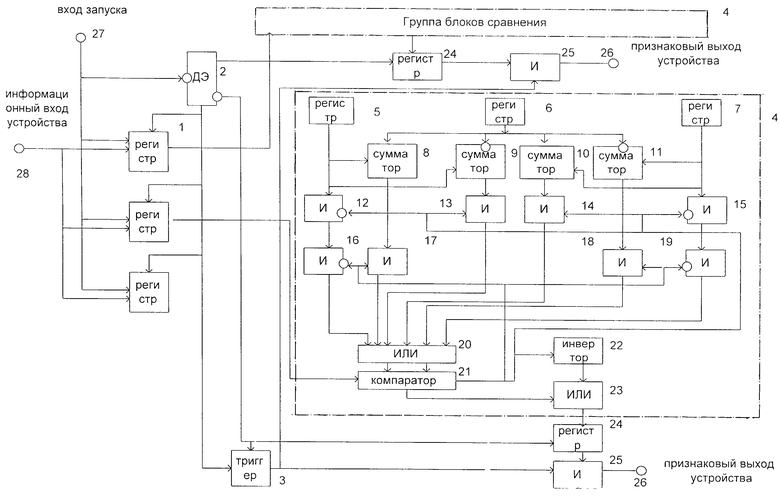

На чертеже представлена функциональная схема устройства, позволяющего устранить указанный недостаток.

Поставленная цель достигается тем, что устройство для допускового контроля функциональных состояний технических систем содержит группу блоков памяти 1i, дифференцирующий элемент 2, триггер 3, группу блоков сравнения 4i, каждый из которых содержит первый 5, третий 6, второй 7 регистры памяти, первый 8, второй 9, третий 10, четвертый 11 сумматоры, первый 12, второй 13, третий 14, четвертый 15, пятый 16, шестой 17, седьмой 18 и восьмой 19 блоки элементов И, блок элементов ИЛИ 20, инвертор 22, элемент ИЛИ 23, группу регистров памяти 24, группу элементов И 25, признаковый выход устройства 26, вход запуска устройства 27, группу информационных входов устройства 28 (i=1, ...,n, где n - число контролируемых подсистем). Блоки памяти 1, компараторы, дифференциальный элемент 2, триггер 3, группы элементов И 25, регистры памяти 24 по своему функциональному назначению аналогичны блокам задания показателей и схемам сравнения прототипа, поэтому они включены в ограничительную часть формулы изобретения.

В каждом блоке 4 группы блоков сравнения выходы регистра 5 соединены с информационными входами блока 12 элементов И и первыми входами сумматоров 8 и 9, инверсный вход сумматора 8 объединен с выходом регистра 6 и вторым входом сумматоров 9, 10, 11. Выходы сумматоров 8, 9, 10, 11 соединены с входами 17, 13, 14, 18 элементов И соответственно. Выходы 12 и 15 элементов И подключены к входам элементов И 16 и 19 соответственно. Инверсные входы блоков 12, 15, а также управляющие входы блоков 13, 14 подключены ко второму выходу компаратора 21 и через инвертор 22 ко второму входу элемента 23. Инверсные входы блоков 16, 19, а также управляющие входы блоков 17 и 18 соединены с первым выходом компаратора. Выходы блоков 13, 14, 16, 17, 18, 19 подключены к первому, второму, третьему, четвертому, пятому и шестому входам 20 элемента ИЛИ соответственно. Первый и второй выходы блока 20 соединены соответственно со вторым и третьим входами компаратора, первый выход которого соединен с первым выходом элемента ИЛИ 23 и управляющими входами 17 и 18 элементов И, а также с инверсными входами 16 и 19 элементов И.

Сравнительный анализ заявляемого устройства с прототипом показал, что новое устройство отличается введением в каждый блок сравнения 4i дополнительных сумматоров и группы элементов И, что говорит о "новизне" технического решения.

На дату подачи заявки не найдены технические решения с аналогичной совокупностью существенных признаков, требуемых для данного технического результата, что говорит об "изобретательском уровне" заявленного решения.

Решение начинается с записи в соответствующие блоки памяти группы блоков сравнения аналогично прототипу. С поступлением сигнала уровня логической единицы на вход 27 устройства разрешается запись в блоки 1 памяти информации с входов 28 устройства, соответствующие состояниям n подсистем контролируемого объекта. Одновременно сигнал запуска через дифференцирующий элемент 2, его прямой выход сбрасывает в "ноль" триггер 3 и группу регистров 24 памяти, поступая на входы их сброса. С блоков 1 памяти значения показателей поступают на информационные входы соответствующих блоков 4 сравнения, которые являются одновременно первыми информационными входами компараторов 21. Причем на вторую и третью группы входов каждого компаратора через соответствующие выходы блока 20 элементов ИЛИ, а также блоки 16 и 19 элементов И поступают значения Рi H и Рi В с информационных выходов регистров 5 и 7 соответственно. В компараторе осуществляется проверка условия

Pi H<Pi<Pi B. (1)

При невыполнении условия (1) срабатывает второй выход компаратора 21, сигнал с выхода которого закрывает блоки 12 и 15 элементов И и открывает блоки 13 и 14 элементов И, обеспечивая прохождение информации с сумматоров 9 и 10, которые обеспечивают расширение области допуска параметра на 3σ относительно верхней и нижней границы, причем величина σ хранится в блоке 6 памяти, которая вычитается из Рi H в сумматоре 9 и складывается с Рi B в сумматоре 10. В этом случае устраняется неоднозначность классификации ситуации при нахождении параметра на границе области значения анализируемых показателей согласно выражению (1). Таким образом, снижается вероятность ошибочного признания объекта контроля (ОК) неисправным, то есть уменьшается риск поставщика.

В случае выполнения условия (1) на первом выходе компаратора 21 появляется сигнал, который через блок 23 записывается в соответствующий регистр памяти 24, а также закрывает блоки 16 и 19 элементов И и открывает блоки 17 и 18 элементов И, обеспечивая прохождение информации с сумматоров 8 и 11, что обеспечивает сужение области допуска параметра на 3σ относительно верхней и нижней границы, причем величина σ складывается с Рi H в сумматоре 8 и вычитается из Рi B в сумматоре 11. Таким образом, снижается вероятность ошибочного признания ОК исправным или риск заказчика.

В результате второго цикла сравнения в компараторе 21 на одном из его входов снова появляется сигнал уровня логической единицы, который через элемент ИЛИ 23 (при попадании показателя в расширенную или суженную область) или через инвертор 22 и элемент ИЛИ 23 в противном случае поступает на выход соответствующего блока сравнения и записывается в регистр 24, в котором будет хранится сигнал логического нуля при непопадании проверяемого показателя либо в область Pi H+3σ<Pi<Pi B-3σ, (2), либо в область Рi H-3σ<Рi<Рi B+3σ. Длительность управляющего импульса выбирается из условия необходимой продолжительности двух циклов сравнения в блоках 4, после окончания действия управляющего импульса на входе 27 на инверсном выходе ДЭ 2 появляется сигнал, который перебрасывает в единицу триггер 3, после чего открываются элементы группы И 25, разрешая прохождение информации с выходов регистров 24 на признаковые выходы 26 устройства.

Достоверность (Д) принятия решения по результатам допускового контроля определяется как величина, обратная ошибке контроля: Д=1-Рош. Вероятность ошибки есть сумма двух слагаемых: ошибки первого рода - α (вероятность ошибочного признания ОК неисправным) или риска поставщика и ошибки второго рода - β (ошибочного признания ОК исправным) или риска заказчика, то есть Рош= α+β.

Систематическая составляющая погрешности измерения скомпенсирована, как правило, при калибровке приборов, а случайная составляющая учитывается с помощью дисперсии оценки σ2, тем самым повышается достоверность контроля.

Источники информации

1. Авторское свидетельство 1830536 СССР, кл. G 06 F 15/20, 1993.

2. Патент 2178199 RU, МПК7 G 05 В 23/02 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ ФУНКЦИОНАЛЬНЫХ СОСТОЯНИЙ ТЕХНИЧЕСКИХ СИСТЕМ | 2000 |

|

RU2178199C1 |

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

| Устройство контроля | 1984 |

|

SU1198542A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1545226A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Устройство для моделирования деятельности человека-оператора | 1990 |

|

SU1778761A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОБУЧЕНИЕМ И ОЦЕНИВАНИЕМ ЗНАНИЙ ОБУЧАЮЩИХСЯ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2011 |

|

RU2467388C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОЛУЧЕНИЕМ ОЦЕНКИ КАЧЕСТВА ЗНАНИЙ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2001 |

|

RU2248610C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

Изобретение относится к области вычислительной техники и может быть использовано в автоматических системах испытаний, контроля качества, определения категорий. Техническим результатом является расширение класса решаемых задач. Устройство содержит группу блоков памяти, дифференцирующий элемент, триггер, группу регистров памяти, группу элементов И, группу блоков сравнения, каждая из которых содержит три регистра памяти, четыре сумматора, восемь блоков элементов И, блок элементов ИЛИ, компаратор, инвертор, элемент ИЛИ. 1 ил.

Устройство для допускового контроля функциональных состояний технических систем, содержащее группы блоков сравнения и блоков памяти, а также дифференцирующий элемент, входы управления которых соединены с входом запуска устройства, группу элементов И, входы которых соединены с триггером и регистром, а выходы с соответствующими признаковыми выходами устройства, информационные входы блоков сравнения группы блоков сравнения соединены с выходом соответствующих блоков памяти, при этом каждый упомянутый блок сравнения содержит группу регистров памяти, компаратор, группу сумматоров, блоки элементов И, блок элементов ИЛИ, инвертор, элемент ИЛИ, отличающееся тем, что в каждый упомянутый блок сравнения дополнительно введены третий и четвертый сумматоры, а также группа элементов И, при этом в каждом упомянутом блоке сравнения первый и второй выходы блока элементов ИЛИ соединены со вторым и третьим входами компаратора, первый выход которого соединен с первым входом элемента ИЛИ и инверсными входами пятого и восьмого блоков элементов И, и прямыми входами шестого и седьмого блоков элементов И, а второй выход через инвертор - со вторым входом элемента ИЛИ, выход которого является выходом блока сравнения группы и соединен с информационными входами соответствующих регистров памяти группы регистров памяти, информационные входы блока сравнения являются первыми информационными входами компаратора, второй выход компаратора соединен с инверсными входами первого и четвертого блоков элементов И, и прямыми входами второго и третьего блоков элементов И, выход первого регистра памяти, предназначенного для хранения нижней границы допуска, соединен с первыми входами первого и второго сумматоров, выходы первого и второго сумматоров соединены соответственно с входами шестого и второго блоков элементов И, выход первого блока элементов И соединен с входом пятого блока элементов И, выход которого объединен с первым входом блока элементов ИЛИ, выход второго блока элементов И соединен с третьим входом блока элементов ИЛИ, выход шестого блока элементов И соединен со вторым входом блока элементов ИЛИ, выход второго регистра памяти подключен к третьему и четвертому сумматорам, при этом второй регистр памяти предназначен для подачи значения верхней границы области допуска контроля функциональных состояний технических систем на информационные входы третьего и четвертого сумматоров, выходы третьего и четвертого сумматоров подключены соответственно к информационным входам третьего и седьмого блоков элементов И соответственно, выход четвертого блока элементов И подключен к входу восьмого блока элементов И, выход восьмого блока элементов И подключен к шестому входу блока элементов ИЛИ, выход третьего блока элементов И - к четвертому входу блока элементов ИЛИ, выход седьмого блока элементов И подключен к пятому входу блока элементов ИЛИ, информационные выходы третьего регистра памяти подключены к инверсным входам второго и четвертого сумматоров и ко вторым входам первого и третьего сумматоров, вход запуска устройства через инверсный вход дифференцирующего элемента соединен со входами сброса блоков памяти группы блоков памяти, при этом инверсный выход дифференцирующего элемента соединен с информационным входом триггера, прямой выход дифференцирующего элемента объединен со входами сброса триггера и регистров памяти группы регистров памяти, выход триггера соединен с управляющими входами элементов И группы элементов И, информационные входы элементов И группы элементов И соединены с выходами соответствующих регистров памяти группы регистров памяти, группа информационных входов устройства соединена с информационными входами блоков памяти группы блоков памяти.

| УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ ФУНКЦИОНАЛЬНЫХ СОСТОЯНИЙ ТЕХНИЧЕСКИХ СИСТЕМ | 2000 |

|

RU2178199C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ И КОНТРОЛЯ ПАРАМЕТРОВ | 1992 |

|

RU2029345C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ | 1990 |

|

RU2062502C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ | 2000 |

|

RU2160919C1 |

| Устройство для определения категорий качества объектов | 1991 |

|

SU1830536A1 |

| Устройство для выбора оптимальных решений | 1984 |

|

SU1244672A1 |

| US 4851985 A, 25.07.1989 | |||

| СПОСОБ ИССЛЕДОВАНИЯ ФУНКЦИОНАЛЬНОГО СОСТОЯНИЯ МОЗГА | 1995 |

|

RU2130753C1 |

Авторы

Даты

2004-01-27—Публикация

2002-05-27—Подача