11

Изобретение отн-осится к системам и средствам автоматического контроля функциональных элементов и устройств импульсной техники и находит широкое применение для контроля надежности функционирования последовательно соединенной цепи сумматоров-.

Цель изобретения состоит в уменьшении времени контроля.

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит вход 1 запуска, первый триггер 2, счетчик 3, второй триггер 4, группу 5 триггеров, входы 6 задания фиксированного кода, первьш регистр 7 сдвига, входы 8 задания фиксированного кода,, второй регистр 9 сдвига, генератор 10 тактовых импульсовJ сумматоры 11, контролируемый, сумматор 12, первую 13 и вторую 14 группы сумматоров по модулю два, блок 15 сравнения, дешиф-с ратор 16, элемент ИЛИ 17, группу 18 элементов ИЛИ, контрольные выходы 19 и выход 20 результата контроля.

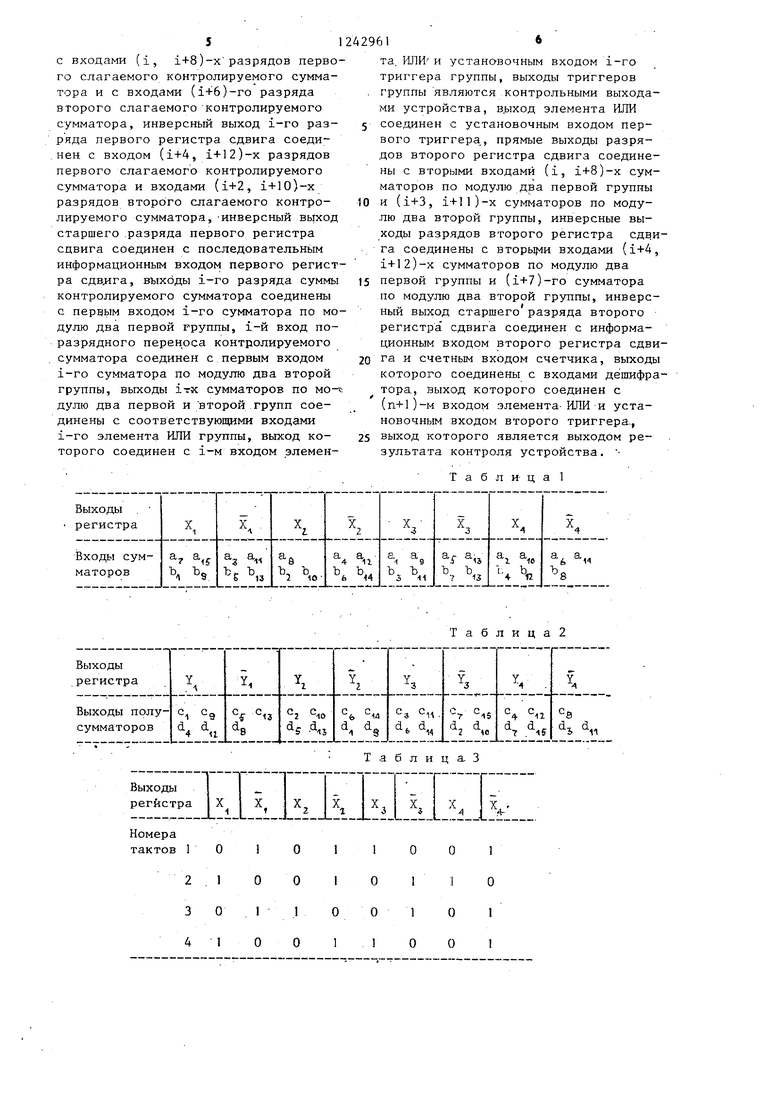

В табл. 1 соединений первого регистра 7 сдвига (Х. и Х- (,4) обозначают соответственно прямой i-й и инверсный i-й выходы регистра 7; (,15) - соответствующий вход разрядов первого слагаемого контролируемого сумматора 12; Ъ (1 1,15) - соответствующий вход разрядов второго слагаемого контролируемого сумматора 12, причем пример приведен для случая контроля цепи последовательно соединенных пятнадцати сумматоров 1 1 .

В табл. 2 соединений второго регистра 9 сдвига у и у. (i,4) обозначают соответственно прямой и ин- вареный i-e выходы регистра 9, и d. (,15) - соответственно вторы входы первого 13 и второго 14 сумматоров по модулю два..

В табл. 3 и 4 сигналов первого 7 и второго 9 регистров сдвига приведены временные-диаграммы изменений сигналов на выходах указанных регистров по тактам, задаваемым генератором 10 тактовых импульсов.

Временные диаграммы (табл. 5) содержат следующие обозначения: 1-й такт - такт, задаваемый генератором 10 тактовых импульсов- А - множе- ство сигналов на входах разрядов первого слагаемого сумматоров 1Ь ;. Ь. е в - множество сигналов на вторых

0

«1

входах разрядов второго слагаемого сумматоров р. е Р - множество сигналов на выходах поразрядного ле- реноса сумматоров 1 Ь ; е S - множество сигналов на выходах разрядов сумм сумматоров 11, -.

Устройство для контроля сумматоров работает следующим образом.

По входу 1 производится -запуск, устройства. В этом случае импульс с входа 1 перебрасывает триггер 2 в . . единичное .состояние, а также сбрасывает в нулевые состояния счетчик 3, второй триггер 4 и триггеры группы 5. 5 Потенциал с выхода триггера 2 запускает генератор 10 тактовых импульсов, который подает тактовые сигналы на тактовые входы первого 7 и второго 9 регистров сдвига.

Алгоритм работы устройства контроля . су мматоров строится на свойствах кольцевых кодов, например четырехразрядного кольцевого кода, который имеет вид: ... 1111011001010000 ....

Возьмем два частных кольца ... . . .00001 1 . . . и . . .1 10100Ш. . ,.

При этом каждое из частных колец дает половину всевозможных четырехразрядных комбинаций, причем разные кольц.з не содержат одинаковых комбинаций .

Применим частные кольца для конт- - роля сумматоров. Рассмотрим возможный вариант. Пусть соответственно на вхо- де разрядов первого слагаемого а , .входе разрядов второго слагаемого Ъ, входе переноса Р , выходе переноса Р и выходе . суммы S первого сумматора 1 формируются следующие последова.- тельности:

а,

5

0

0

0

5

I

Ъ, РО

Р,

Я

lOllOiOO

00101101

01111000

00111100

11100001

При этом законы формирования следующие Р а а Р V Ь Р , S . Аналогично возможно сформировать следующие последовательности выходах сумматоров 11.Ej 00101101 Ъ 01001011 Р 00011110 РЗ 00001111 Зз 011П000

а 01001011 Ъ5 11010010.

Очевидно достоинство применения кольцевых кодов для контроля сумматоров базируется на том, что последовательность сигналов на выходах сумматора 1Ij отличается от последовательности сигналов сумматора 1Ц только временным сдвигом на один такт . Кроме того, вторая половина последовательности является инверсией первой, что позволяет генерировать требуемые последовательности сигналов четырехразрядным регистром сдвига, Проверку любого числа сумматоров можно производить за восемь тактов,

Исходя из изложенного, для орга- низации процесса контроля имеем следующие начальные условия: по первой группе входов 6 фиксированного кода в первый регистр 7 сдвига заносится кодовая комбинация 0010, по второй группе входов 8 фиксированного кода во второй регистр сдвига .заносится код 1110. Причем данные кодовые комбинации заносятся до подачи сигнала по входу 1,

образом, если все сумматоры 11 исправны, то- на выходах сумматоров 13 и 14 по модулю два за восемь тактов - нулевые потенциалы. Тогда счетчик 3 досчитывает до трех, дешифратор 16 дешифрирует это состояние, потенциал с его выхода перево-. дит второй триггер 4 в единичное состояние, а также через элемент ИЛИ i 7 переводит триггер 2 в нулевое состояние и останавливает генератор 10, Сигнал на выходе 20 результата контроля говорит об исправности всех сумматоров контролируемого сумматора 12, Если в одном из сумматоров 11 есть неисправность, то она определяется, так как в этом случае с выходо

2429614

сумматоров 11 и второго регистра 9 различны. Тогда на выходе соответствующего сумматора 13, или по модулю два присутствует потенциал, ко- 5 торьш через элемент ИЛИ 18 перебрасывает триггер 5 в e щничнoe состояние. Сигнал на контрольном выходе 19,- говорит о том, что i-й сумматор I 1у в контролиру емом сумматоре 12 неис10 правен. Кроме того, потенциал с выхода элемента ИЛИ I8 через элемент ИЛИ 17 переводит триггер 2 в единичное состояние, что приводит к остановке генератора 10,

J5 В известном устройстве при выходе из строя цепи сумматоров необходимо затратить время на контроль сумматоров Tjj, время на поиск неисправного сумматора Т и время ремонта Тр .

20 В предлагаемом устройстве время поиска неисправного сумматора TH, значительно меньше. Необходимо, например, проконтролировать только выходы сумм и переноса неисправного

25 сумматора, найденного за время Т, т,е. ..Т . Тогда эффективность предлагаемого устройства определяетс формулой

э 3jc±Itii - -Tp

,

Формула изобретения

Устройство для контроля суммато- ррв, содержащее первый регистр сдвига, первую и вторую группы сумматоров по модулю два, отличающее- с я тем, что, с целью уменьшения времени контроля, в него введены второй регистр сдвига, счетчик, дешифратор, группа элементов ИЛИ, первый и второй триггеры, генератор тактовых импульсов, группа триггеров, причем группа информационных входов первого регистра сдвига является первой группой входов задания фиксированного кода устройства, тактовые входы первого и второго регистров сдвига соединены с выходом генератора тактовых импульсов, вход пуска которого соединен с выходом первого триггера, входы сброса первого и второго триггеров и счетчика соединены с входом запуска устройства, группа информационных входов второго регистра является второй группой входов заания фиксированного кода устройста, прямой выход i-ro разряда первого регистра сдвига () соединен

51

с входами (i, i+8)-x разрядов первого слагаемого контролируемого сумматора и с входами (1+6)-го разряда второго слагаемого контролируемого сумматора, инверсный выход i-ro разряда первого регистра сдвига соединен с входом (i+4, i+12)-x разрядов первого слагаемого контролируемого сумматора и входами (1+2, 1+10)-х разрядов второго слагаемого контролируемого сумматора, -инверсный вьгход старшего разряда первого регистра сдвига соединен с последовательным информационным входом первого регистра , выходы 1-го разряда суммы контролируемого сумматора соединены с первым входом 1-го сумматора по модулю два первой группы, 1-й вход поразрядного перенрса контр1олируемого сумматора соединен с первым входом 1-го сумматора по модулю два второй группы, выходы 1тх сумматоров по мо- дулю два первой и второй групп соединены с соответствующими входами 1-го элемента ИЛИ группы, выход которого соединен с 1-м входом элемен2429616

та. ШШ и установочным входом 1-го триггера группы, выходы триггеров . группы являются контрольными выходами устройства, зз.ыход элемента ИЛИ 5 соединен с установочным входом первого триггера., прямые выходы разрядов второго регистра сдвига соединены с вторыми входами (1, 1+8)-х сумматоров по модулю два первой группы

10 и (1+3, i+ll)-x сумматоров по модулю два второй группы, инверсные выходы разрядов второго регистра сдчи- га соединены с вторы 4и входами (1+4, 1+12)-х сумматоров по модулю два

15 первой группы и (1+7)-го сумматора по модулю два второй группы, инверсный выход старшего разряда второго регистра сдвига соединен с информационным входом второго регистра сдви20 га и счетным входом счетчика, выходы которого соединены с входами дешифратора, выход которого соединен с (п+1)-м входом элемента-ИЛИ И установочным входом второго триггера.,

25 выход которого является выходом результата контроля устройства. Т а б л и- ц а 1

Т а б л и ц а 2

ТаблицаЗ

Т а б л и ц а 5

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2019 |

|

RU2711054C1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для формирования тестовых воздействий | 1984 |

|

SU1168953A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1037257A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

Изобретение относится к системам и средствам автоматического контроля функциональных элементов и устройств импульсной техники. Цель - уменьшение времени контроля. Устройство содержит два регистра сдвига, две группы сумматоров по модулю два, счетчик, дешифратор, группу элементов ИЛИ, два триггера, группу триггеров, генератор тактовых импульсов. 1 ил. 5 табл. о 4 to О)

| Устройство для контроля сумматора | 1973 |

|

SU510716A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Контролируемый п-разрядный сумматор | 1973 |

|

SU500527A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля сумматора | 1972 |

|

SU483673A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1983-11-21—Подача