Изобретение относится к цифровой вычислительной технике и может быть использовано в КМДП интегральных схемах при реализации устройств логической обработки многоразрядных двоичных данных.

Известна реализация устройства логического сравнения на КМДП транзисторах, которое содержит логические элементы 2И-НЕ в каждом разряде и выходной блок статического типа (Патент США №5281946, G05B 1/03, G06F 7/02, НКИ 340-146.2 от 25.01.94). Недостаток устройства - ограничение быстродействия при увеличении числа разрядов, что обусловлено линейным ростом числа емкостных нагрузок на выходах логических элементов и увеличением величины нагрузок, в том числе за счет пропорционального роста числа последовательно включенных логических транзисторов p-типа выходного блока.

Наиболее близким техническим решением к предлагаемому является устройство сравнения на КМДП транзисторах (Патент РФ №2236696, G05B 1/03, Н03К 19/094 от 11.04.2003). Это устройство, принятое за прототип, содержит k блоков сравнения на основе m одноразрядных элементов сравнения с нагрузкой в виде предзарядовых транзисторов p-типа и выходной блок на основе k трехтранзисторых звеньев, на которые поступают сигналы с выходов k блоков сравнения. Недостатком этого устройства является недостаточное быстродействие при большом числе разрядов D=km сравниваемых операндов, что связано с большим числом последовательно включенных транзисторов в каждом блоке сравнения (2m) и в выходном блоке (k).

Технической задачей, решаемой в изобретении, является повышение быстродействия устройства при сравнении многоразрядных операндов.

Поставленная цель достигается тем, что многоразрядное устройство логического сравнения, содержащее k блоков сравнения и выходной блок, каждый блок сравнения содержит три предзарядовых транзистора p-типа и m логических элементов, каждый из которых выполнен на шести транзисторах n-типа, которые соединены попарно последовательно, причем первый и второй транзисторы n-типа включены между первым и общим выводами логического элемента, третий и четвертый включены между вторым и общим выводами логического элемента, а пятый и второй, шестой и четвертый включены между третьим и общим выводами логического элемента, первые и вторые выводы логических элементов в каждом блоке сравнения соединены соответственно с первым и вторым выходами данного блока, третий вывод логического элемента соединен с общим выводом последующего логического элемента, причем третий вывод последнего из m логических элементов в каждом блоке сравнения соединен с третьим выходом данного блока, объединенные по два затворы первого и шестого, третьего и пятого транзисторов n-типа подключены соответственно к первому и второму входам логического элемента, на которые подаются парафазные сигналы соответствующего разряда первого операнда, затворы второго и четвертого транзисторов n-типа подключены соответственно к третьему и четвертому входам логического элемента, на которые подаются парафазные сигналы одноименного разряда второго операнда, при этом входы первого логического элемента в каждом блоке сравнения соответствуют старшему разряду из соответствующей m-разрядой группы операндов, а входы последнего m-го логического элемента соответствуют младшему разряду той же группы разрядов операндов, в каждом блоке сравнения соответствующий предзарядовый транзистор p-типа включен между шиной питания и одноименным выходом блока сравнения, затворы всех предзарядовых транзисторов p-типа подключены к тактовой шине, а выходной блок содержит три транзистора p-типа, которые включены между шиной питания и соответственно одноименным выходом устройства, затворы которых подключены к тактовой шине, и транзисторные звенья первого типа, каждое из которых содержит три выходных транзистора n-типа, затворы которых подключены к одноименным входам транзисторного звена, причем первый и второй выходные транзисторы n-типа включены общим выводом своего транзисторного звена и соответственно первым и вторым выходами устройства, а третьи выходные транзисторы n-типа включены между общими выводами своего и последующего транзисторных звеньев, третий выходной транзистор n-типа последнего транзисторного звена первого типа включен между третьим выходом устройства и общим выводом этого транзисторного звена, содержит n блоков свертки, каждый из которых содержит три предзарядовых транзистора n-типа, которые включены между шиной земли и одноименным выходом данного блока свертки, и k/n транзисторных звеньев второго типа, каждое из которых содержит три логических транзистора p-типа, затворы которых подключены к одноименным входам транзисторного звена второго типа, первый и второй логические транзисторы p-типа в каждом транзисторном звене второго типа включены между общим выводом своего транзисторного звена и одноименным выходом данного блока свертки, а третьи логические транзисторы p-типа в каждом блоке свертки включены между общими выводами своего и последующего тразисторных звеньев второго типа, причем третий логический транзистор p-типа последнего k/n тразисторного звена второго типа включен между общим выводом своего транзисторного звена и третьим выходом данного блока свертки, а число транзисторных звеньев первого типа в выходном блоке равно n, общие выводы первых логических элементов всех блоков сравнения, общий вывод первого транзисторного звена выходного блока и затворы предзарядовых транзисторов n-типа всех блоков свертки соединены с противофазной тактовой шиной, общие выводы первых транзисторных звеньев второго типа всех блоков свертки соединены с тактовой шиной, выходы блоков сравнения подключены к одноименным входам соответствующих транзисторных звеньев второго типа, причем выходы первого блока сравнения подключены к входам первого транзисторного звена второго типа первого из n блоков свертки, выходы последнего k-го блока сравнения подключены к входам последнего k/n тразисторного звена второго типа последнего n-го блока свертки, выходы блоков свертки подключены к одноименным входам соответствующего транзисторного звена первого типа выходного блока, причем выходы блоков свертки соответствуют одноименным транзисторным звеньям первого типа выходного блока.

Существенными отличительными признаками в указанной совокупности признаков является наличие в устройстве n блоков свертки, каждый из которых включен между группой k/n блоков сравнения и выходным блоком, содержащим n транзисторных звеньев с соответствующими связями, а также выполнение блоков свертки на транзисторах дополняющего типа в сочетании с противофазным тактированием.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - повышение быстродействия устройства при сравнении многоразрядных операндов благодаря тому, что в одноименных блоках процесс переключения происходит одновременно, и при наличии блоков свертки уменьшается или ограничивается число последовательно включенных транзисторов в цепях переключения емкостных нагрузок выходов каждого из блоков и, следовательно, число временных задержек, причем без использования дополнительных инверторов.

Действительно, в цепи последовательно соединенных транзисторов задержка переключения пропорциональна их числу. При одинаковых размерах транзистор n-типа вносит задержку Т0, а транзистор p-типа - 2Т0. В случае наибольшей задержки - при равенстве разрядов двух операндов - задержка в блоке сравнения составляет 2mТ0, в выходном блоке - kT0. При разрядности операндов, равной N=m·k, с учетом инверторов суммарная задержка в устройстве-прототипе составляет Т=T0(2m+2+k)=T0(2N/k+2+k). В 32-разрядном устройстве (N=32, m=4, k=8) задержка составляет Т=18Т0, а в 64-разрядном устройстве (N=64, m=8, k=8) задержка составляет Т=26Т0.

В предложенном устройстве суммарная задержка составляет T=T0(2m+2k/n+n)=T0(2N/k+2k/n+n). В 32-разрядном устройстве (N=32, m=4, k=8, n=4) задержка равна Т=16Т0, а в 64-разрядном устройстве (N=64, m=4, k=16, n=4) задержка равна Т=20Т0.

При разрядности устройства больше 16 предложенное устройство всегда имеет меньшую задержку, чем известное, когда n больше 2 и k больше или равно 4. При этом практически неэффективно использовать цепи с числом последовательно соединенных транзисторов более 8, поскольку задержка возрастает дополнительно за счет узловых емкостей. Поэтому 128-разрядное устройство (N=128, m=4, k=32, n=8) с высоким быстродействием (24Т0) можно реализовать только на основе предложенного.

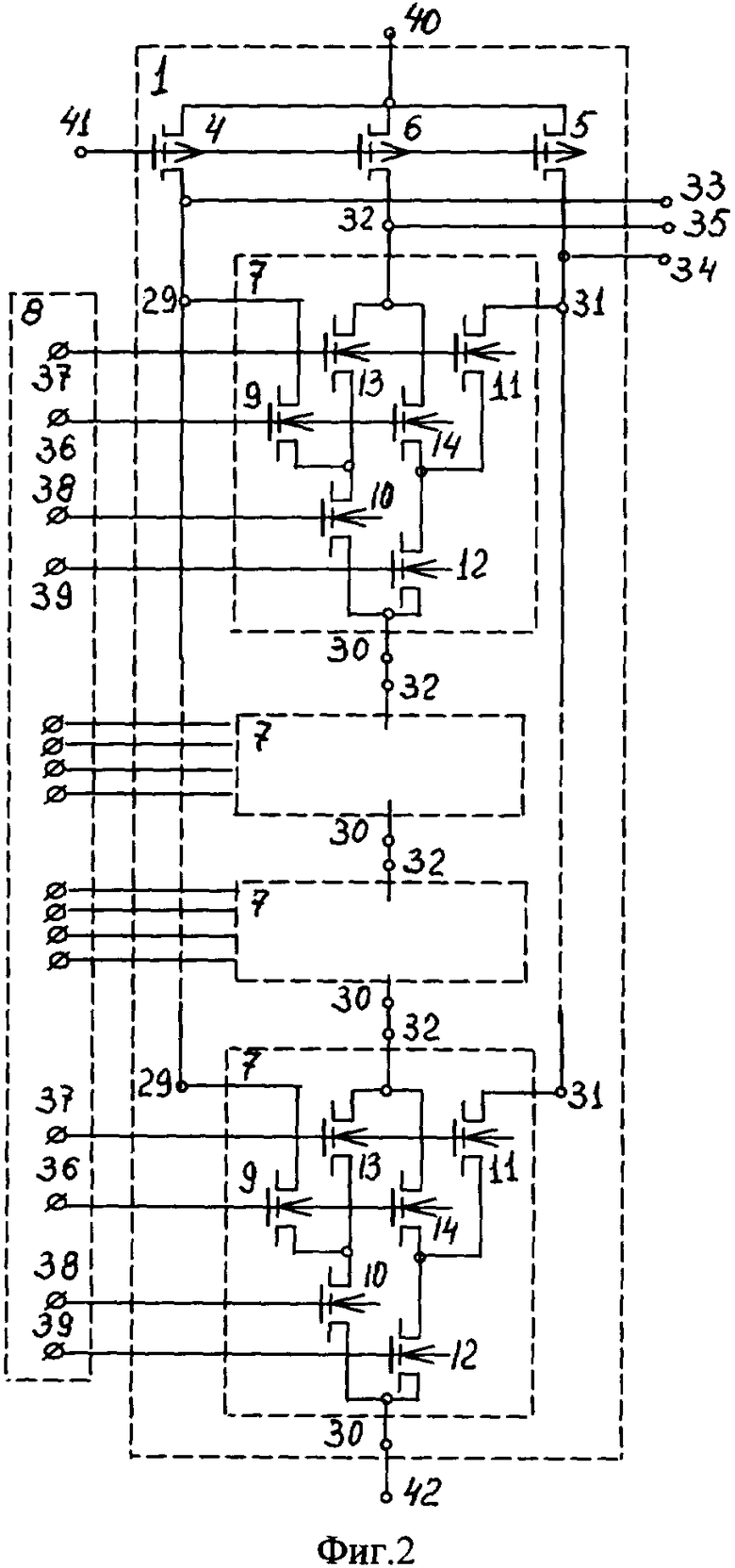

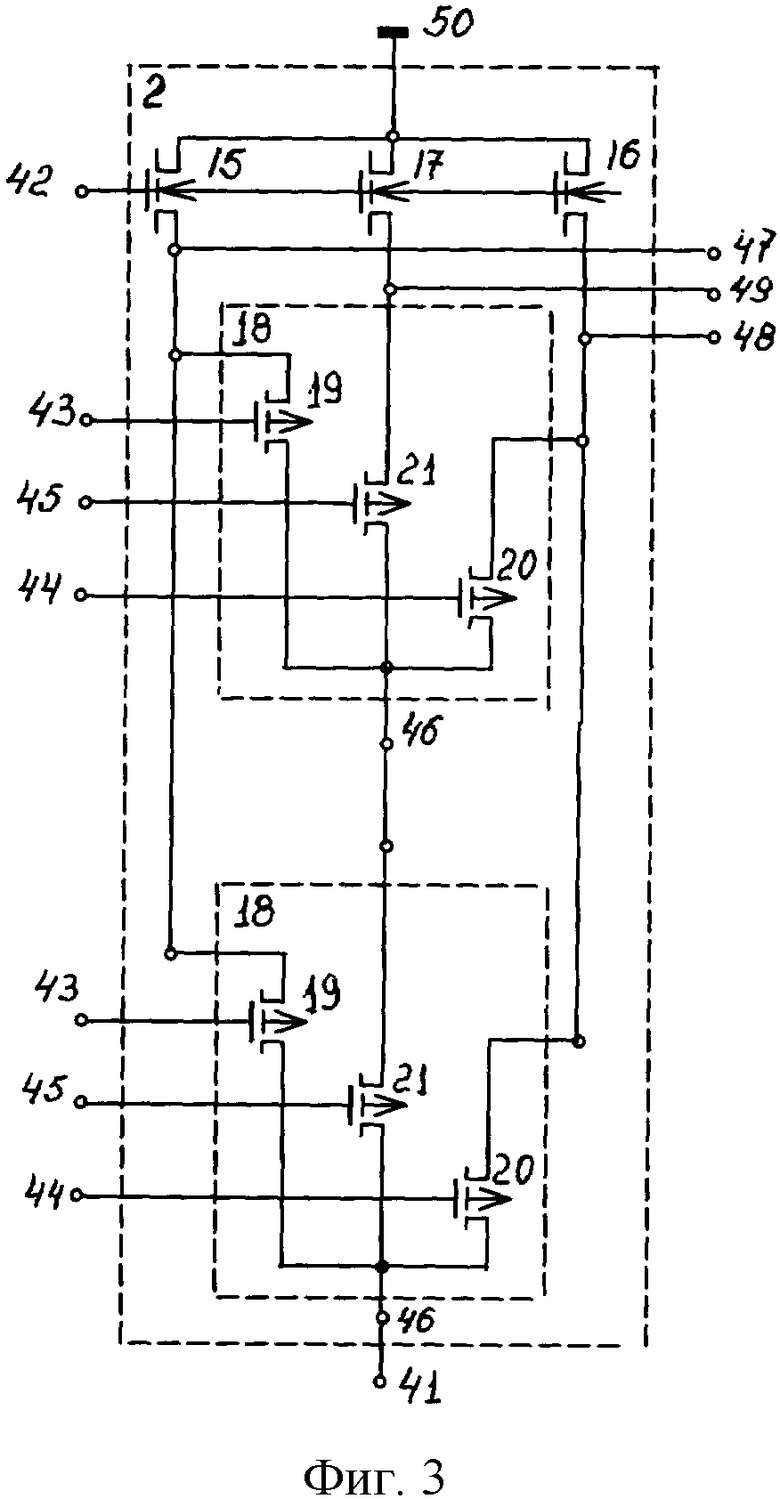

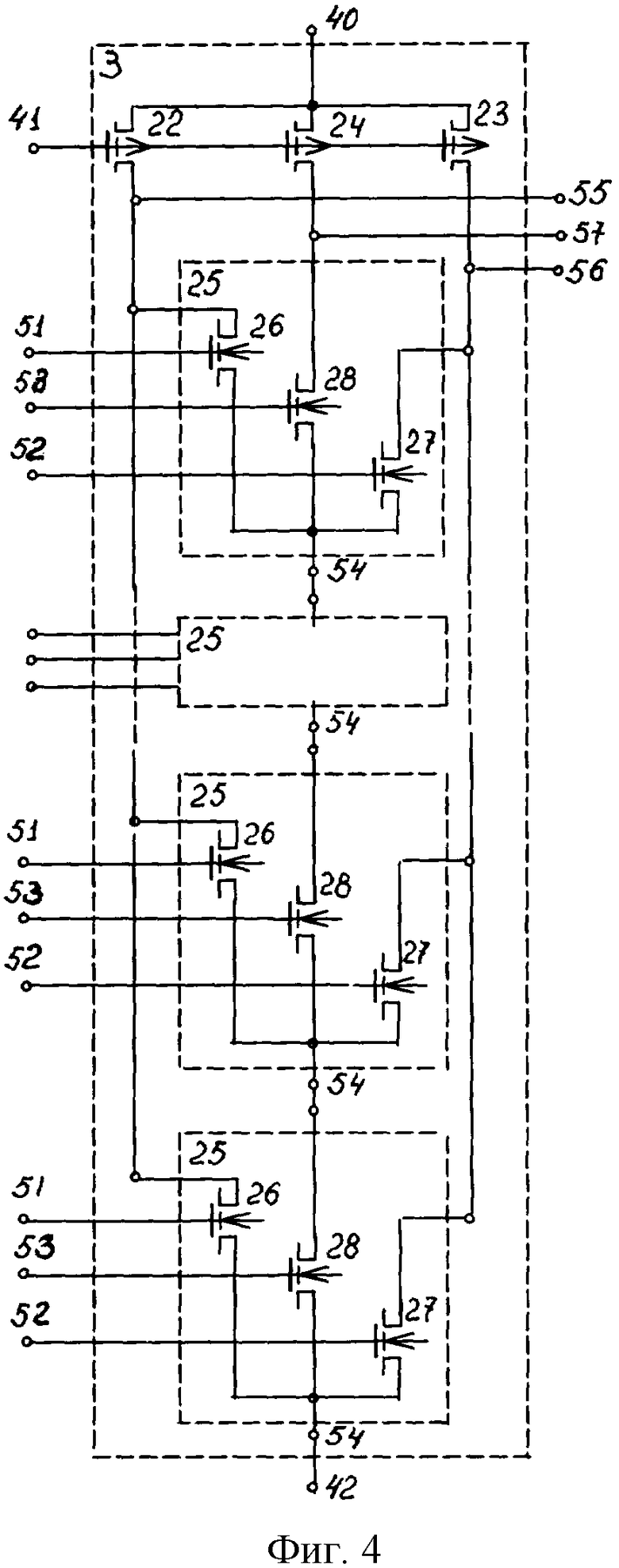

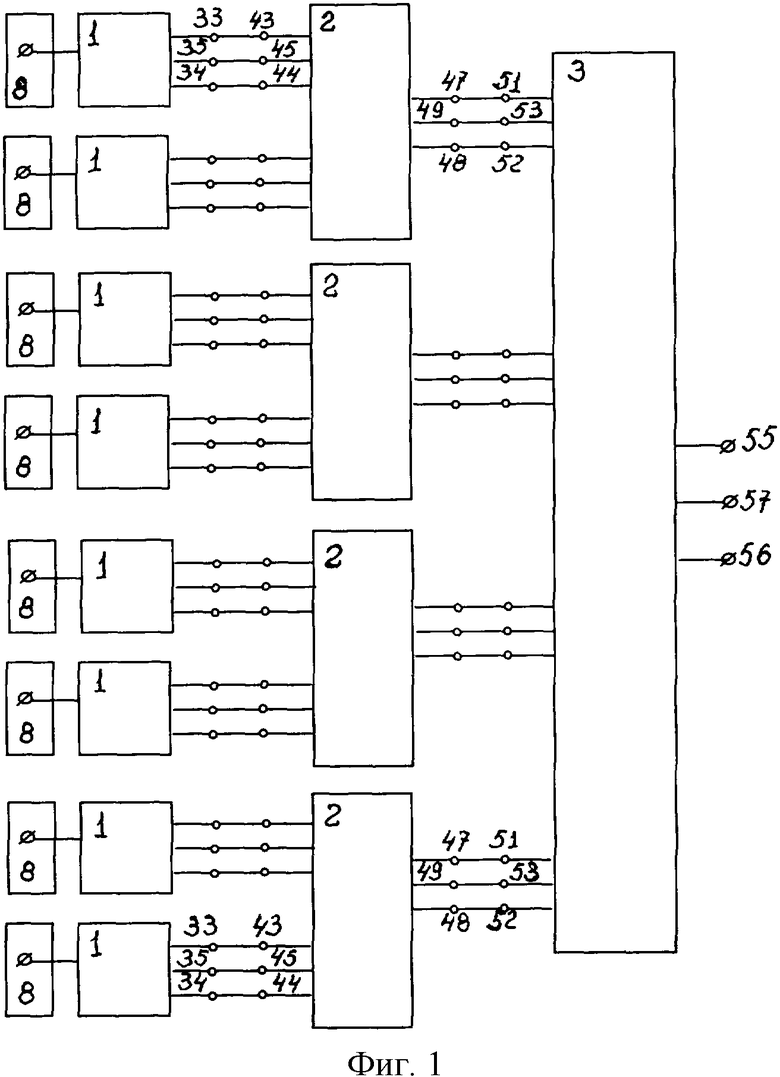

На фиг.1 приведена функциональная схема заявляемого устройства, представленного в виде 32-разрядного устройства логического сравнения при m=4, n=4, k=8. На фиг.2 приведена принципиальная схема блока сравнения, на фиг.3 - принципиальная схема блока свертки и на фиг.4 - принципиальная схема выходного блока

Многоразрядное устройство логического сравнения (фиг.1) содержит восемь (k=8) блоков сравнения 1, четыре (n=4) блока свертки 2 и выходной блок 3.

Блок сравнения 1 (Фиг.2) содержит три предзарядовых транзистора 4-6 p-типа, четыре (m=4) логических элемента 7 с соответствующими входами 8 на группу 4 разрядов операндов. Логический элемент выполнен на шести транзисторах 9-14 n-типа.

Блок свертки 2 (Фиг.3) содержит три предзарядовых транзистора 15-17 n-типа и два (k/m=2) транзисторных звена 18 второго типа, каждое из которых содержит три логических транзистора 19-21 p-типа.

Выходной блок 3 (Фиг.4) содержит три транзистора 22-24 p-типа и четыре (n=4) транзисторных звена 25 первого типа, каждое из которых содержит три выходных транзистора 26-28 n-типа.

В логическом элементе 7 соединенные попарно последовательно первый 9 и второй 10 транзисторы n-типа включены между первым 29 и общим 30 выводами логического элемента, третий 11 и четвертый 12 включены между вторым 31 и общим 30 выводами логического элемента, а пятый 13 и второй 10, шестой 14 и четвертый 12 транзисторы n-типа включены между третьим 32 и общим 30 выводами логического элемента. Первые 29 и вторые 31 выводы логических элементов 7 в каждом блоке сравнения соединены соответственно с первым 33 и вторым 34 выходами данного блока, третий вывод 32 логического элемента 7 соединен с общим выводом 30 последующего логического элемента, причем третий вывод 32 последнего четвертого логического элемента в каждом блоке сравнения соединен с третьим выходом 35 данного блока. Объединенные по два затворы первого 9 и шестого 14, третьего 11 и пятого 13 транзисторов n-типа подключены соответственно к первому 36 и второму 37 входам логического элемента, на которые подаются парафазные сигналы соответствующего разряда первого операнда. Затворы второго 10 и четвертого 12 транзисторов n-типа подключены соответственно к третьему 38 и четвертому 39 входам логического элемента, на которые подаются парафазные сигналы одноименного разряда второго операнда. При этом входы первого логического элемента в каждом блоке сравнения соответствуют старшему разряду из соответствующей 4-х разрядной группы 8 входов, а входы последнего четвертого логического элемента соответствуют младшему разряду той же группы разрядов. Входы 8 первого блока сравнения соответствуют четырем старшим разрядам операндов, а на каждую группу входов 8 последующих блоков сравнения разрядность парафазных сигналов уменьшается на 4. Входы 8 последнего восьмого блока сравнения соответствуют четырем младшим разрядам операндов.

В каждом блоке сравнения 1 первый 4, второй 5 и третий 6 предзарядовые транзисторы p-типа включены между шиной питания 40 и соответственно первым 33, вторым 34 и третьим 35 выходами блока сравнения. Затворы предзарядовых транзисторов 4-5 p-типа блоков сравнения 1 подключены к тактовой шине 41, а общие выводы 30 первых логических элементов всех блоков сравнения 1 подключены к противофазной тактовой шине 42.

В каждом транзисторном звене 18 второго типа блоков свертки 2 затворы первого 19, второго 20 и третьего 21 логических транзисторов p-типа подключены к одноименным входам 43-45 данного транзисторного звена второго типа, первый 19 и второй 20 логические транзисторы p-типа включены между общим выводом 46 своего транзисторного звена и соответственно первым 47 и вторым 48 выходами данного блока свертки. Третий логический транзистор 21 p-типа первого транзисторного звена второго типа включен между общими выводами 46 первого и второго тразисторных звеньев второго типа, а третий логический транзистор 21 p-типа второго тразисторного звена включен между общим выводом 46 своего транзисторного звена и третьим выходом 49 данного блока свертки. Общий вывод 46 первого тразисторного звена второго типа включен к тактовой шине 41. В каждом блоке свертки первый 15, второй 16 и третий 17 предзарядовые транзисторы n-типа включены между шиной земли 50 и соответственно одноименным выходом 47-49 данного блока свертки, а затворы тех же транзисторов подключены к противофазной тактовой шине 42.

В транзисторных звеньях 25 первого типа выходного блока 3 затворы первого 26, второго 27 и третьего 28 выходных транзисторов n-типа подключены соответственно к одноименным входам 51-53 соответствующего транзисторного звена, причем первый 26 и второй 27 выходные транзисторы n-типа включены между общим выводом 54 своего транзисторного звена и соответственно первым 55 и вторым 56 выходами устройства, а третьи выходные транзисторы 28 n-типа включены между общими выводами 54 своего и последующего транзисторных звеньев. Третий выходной транзистор 28 n-типа последнего четвертого транзисторного звена первого типа включен между общим выводом 54 этого транзисторного звена и третьим выходом 57. Общий вывод 54 первого транзисторного звена первого типа подключен к противофазной тактовой шине 42. В выходном блоке 3 первый 22, второй 23 и третий 24 предзарядовые транзисторы n-типа включены между шиной питания 40 и соответственно одноименным выходом 55-57 устройства, а затворы тех же транзисторов подключены к тактовой шине 41.

Выходы 33-35 первого блока сравнения 1 подключены к одноименным входам 43-45 первого транзисторного звена 18 второго типа первого блока свертки 2, а те же выходы второго блока сравнения 1 подключены к одноименным входам 43-45 второго транзисторного звена 18 второго типа первого блока свертки 2. Выходы 33-35 третьего и четвертого блоков сравнения 1 подключены к одноименным входам 43-45 соответственно первого и второго транзисторного звена 18 второго типа второго блока свертки 2. Выходы пятого и шестого блоков сравнения 1 подключены к соответствующим входам 43-45 первого и второго транзисторных звеньев 18 второго типа третьего блока свертки 2, а выходы седьмого и последнего восьмого блоков сравнения 1 подключены к соответствующим входам 43-45 первого и второго транзисторных звеньев 18 второго типа последнего четвертого блока свертки 2.

Выходы 47-49 первого и второго блоков свертки 2 подключены к одноименным входам 51-53 соответственно первого и второго транзисторных звеньев 25 первого типа выходного блока 3, а те же выходы 47-49 третьего и четвертого блоков свертки 2 подключены к одноименным входам 51-53 соответственно третьего и четвертого транзисторных звеньев 25 первого типа выходного блока 3.

Устройство работает следующим образом. Входы 8 первого блока сравнения соответствуют четырем старшим разрядам операндов, а на каждую группу входов 8 последующих блоков сравнения разрядность парафазных сигналов уменьшается на 4. Входы 8 последнего восьмого блока сравнения соответствуют четырем младшим разрядам операндов. При сравнении двух 32-разрядных операндов (двоичных чисел) А=Х32Х31...X2X1 и В=У32У31...У2У1 на первый 36 и второй 37 входы логических элементов 7 блоков сравнения 1 подаются соответственно прямой и логически дополняющий (парафазные) сигналы соответствующего разряда Xi первого операнда А, а на четвертый 39 и третий 38 входы того же логического элемента - прямой и дополняющий сигналы того же разряда Уi второго операнда В.

Двоичному значению логической 1 соответствует высокий уровень напряжения шины питания, а значению логического 0 - низкий уровень напряжения шины земли. Открытому состоянию транзистора n-типа соответствует сигнал логической 1, поданный на затвор транзистора, а транзистора p-типа - сигнал логического 0.

В исходном состоянии - на первом полутакте, при нулевом сигнале на тактовой шине 41 и положительном сигнале на противофазной тактовой шине 42 все предзарядовые транзисторы p-типа 4-6 и n-типа 15-17, а также транзисторы 22-24 p-типа выходного блока 3 открыты. От шины питания 40 через указанные транзисторы p-типа происходит процесс предзаряда узловых емкостей, связанных с выходами 33-35 блоков сравнения 1 и с выходами 55-57 устройства до уровня логической 1. Выходы 47-49 блоков свертки 2 через предзарядовые транзисторы 15-17 n-типа приобретают нулевой потенциал шины земли 50. Поэтому все логические транзисторы 19-21 p-типа транзисторных звеньев 18 второго типа блоков свертки 2 и выходные транзисторы 26-28 n-типа транзисторных звеньев 25 выходного блока 3 закрыты. На первом полутакте на входах 36-39 логических элементов 7 всех блоков сравнения 1 устанавливаются соответствующие операндам парафазные сигналы.

На втором полутакте после подачи положительного сигнала на тактовую шину 41 и нулевого сигнала на противофазную тактовую шину 42 предзарядовые транзисторы p-типа 4-6 и n-типа 15-17, а также транзисторы 22-24 p-типа выходного блока 3 закрываются.

Каждый логический элемент реализует функцию полного одноразрядного логического сравнения. Причем, когда Х>У, в открытом состоянии находятся первый 9 и второй 10 транзисторы n-типа каждого логического элемента и узловая емкость, связанная с первым 33 выходом блока сравнения 1, может разряжаться до уровня логического 0, но лишь в том случае, если на третьем выводе 32 предыдущего логического элемента 7 сформируется нулевой потенциал. Когда Х<У, в открытом состоянии находятся третий 11 и четвертый 12 транзисторы n-типа логического элемента и узловая емкость, связанная с вторым 34 выходом блока сравнения 1, может разряжаться до уровня логического 0. В случае равенства Х=У замыкается цепь между третьим выводом 32 и общим выводом 30 логического элемента 7, поскольку открытыми являются либо пятый 13 и второй 10 транзисторы n-типа логического блока (Х=У=0), либо шестой 14 и четвертый 12 транзисторы n-типа (Х=У=1). При этом формируется проводящая цепь между третьим 32 и общим 30 выводами логического элемента блока.

Если первая или вторая логические ситуации характерны уже для старшего разряда операндов и реализуются соответственно в первом логическом элементе 7 первого блока сравнения 1 (Х32>У32 или Х32<У32), то независимо от состояний других логических элементов на первом 33 или втором 34 выходах первого логического элемента 7 первого блока сравнения формируется логический 0. Этим сигналом открываются первый 19 или второй 20 логические транзисторы p-типа первого транзисторного звена 18 второго типа первого блока свертки 2 и от тактовой шины 41 на первом 47 или втором 48 выходе первого блока свертки 2 формируется сигнал логической 1. Этот сигнал поступает на одноименный вход (51 или 52) первого транзисторного звена 25 первого типа выходного блока 3 и, благодаря открытому первому 26 или второму 27 выходным транзисторам n-типа этого транзисторного звена и нулевому потенциалу на противофазной тактовой шине 42, на первом 55 или втором 56 выходах устройства формируется выходной сигнал логического 0. Таким образом реализуются функции А>В и А<В при несовпадении в старшем разряде операндов. Транзисторные звенья 18 и 25 обоих типов функционируют таким образом, что при любом наборе переменных на входах 8 возможна реализация только одной функции из 3, причем с учетом состояния общего вывода конкретного транзисторного звена.

При равенстве переменных, соответствующих старшим четырем разрядам операндов А и В, первый 33 и второй 34 выходы первого блока сравнения 1 сохраняют состояние логической 1, а на третьем выходе 35 этого блока сравнения 1 формируется сигнал логическоого 0 и третий логический транзистор 21 p-типа первого транзисторного звена 25 первого блока свертки 2 открыт и создает проводящую цепь для функционирования логических транзисторов p-типа второго и последующих транзисторных звеньев блока свертки 2 в зависимости от сигналов, формируемых на выходах 33-35 второго и последующих блоков сравнения 1.

При несовпадении операндов А и В только в каком-либо из младших четырех разрядов на первых 33 и вторых 34 выходах с первого по седьмой включительно блоков сравнения 1 сохраняются состояния логической 1, а на третьих выходах 35 тех же блоков сравнения формируется состояние логического 0. Соответственно этим сигналам на первых 47 и вторых 48 выходах первого, второго и третьего блоков свертки 2 сохраняется состояние логического 0, а на третьих выходах 49 этих блоков свертки формируется состояние логической 1. Причем в четвертом блоке свертки третий логический транзистор 21 первого транзисторного звена 18 второго типа открыт и общий вывод 46 второго транзисторного звена этого блока имеет положительный потенциал тактовой шины 41. Поэтому логическое состояние выходов 47-49 последнего четвертого блока свертки 2 зависит от сигналов на входах 43-45, поступающих с выходов 33-35 последнего восьмого блока сравнения 1. Одновременно в выходном блоке 3 третьи выходные транзисторы 28 n-типа первого, второго и третьего транзисторных звеньев 25 первого типа открываются и общий вывод 54 последнего четвертого транзисторного звена этого блока приобретает нулевой потенциал противофазной тактовой шины 42. Поэтому состояние выходов 55 и 56 устройства зависит от сигналов на входах 51-52 четвертого транзисторного звена этого блока, которые в свою очередь зависят от состояния выходов 47-48 четвертого блока свертки 2 и в итоге от сигналов на выходах 33-34 восьмого блока сравнения 1, которое определяется парафазными сигналами на входах 8, соответствующими логическим значениям четырех младших разрядов операндов.

В случае логического равенства операндов А и В на первых 33 и вторых 34 выходах всех 8 блоков сравнения 1 сохраняются состояния логической 1, а на третьих выходах тех же блоков формируются сигналы логического 0. Третьи логические транзисторы 21 p-типа обоих транзисторных звеньев 18 второго типа всех блоков свертки открыты, на выходах 49 этих блоков формируются сигналы логической 1, третьи выходные транзисторы 28 n-типа транзисторных звеньев 25 первого типа выходного блока 3 открыты и на третьем выходе 57 устройства при этом формируется сигнал логического 0.

Устройство позволяет реализовать функцию полного сравнения операндов (по критериям - «больше», «меньше», «равно»). Подключение в качестве нагрузки к первому 55 и третьему 57 выходам устройства логического элемента 2И-НЕ позволяет получить значение функции сравнения по критерию «больше или равно» - «меньше», а подключение в качестве нагрузки к второму 56 и третьему 57 выходам устройства логического элемента 2И-НЕ позволяет получить значение функции сравнения по критерию «меньше или равно» - «больше». Подключение к выходам 55-57 устройства логического элемента 3И-НЕ позволяет сформировать асинхронный сигнал завершения операции сравнения, который может быть использован для ограничения длительности такта, благодаря чему повышается быстродействие устройства на системном уровне.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СРАВНЕНИЯ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2236696C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2258303C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| МНОГОВХОДОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И НА КМДП ТРАНЗИСТОРАХ | 2006 |

|

RU2319299C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ПЕРЕНОСА В СУММАТОРЕ | 2013 |

|

RU2525111C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в интегральных схемах в качестве устройства логической обработки многоразрядных двоичных данных. Технический результат заключается в повышении быстродействия устройства при сравнении многоразрядных операндов. Устройство содержит k блоков сравнения (1), n блоков свертки (2) и выходной блок (3), причем каждый блок сравнения 1 содержит три предзарядовых транзистора (4-6) р-типа и m логических элементов, выполненных в виде одноразрядного элемента сравнения на шести транзисторах (9-14) n-типа, а каждый блок свертки (2) содержит три предзарядовых транзистора (15-17) n-типа и k/n транзисторных звеньев (18) второго типа, выполненных на трех логических транзисторах (19-21) р-типа, а также содержит выходной блок (3), содержащий три транзистора р-типа (22-24), и соответственно числу блоков свертки n транзисторных звеньев (25) первого типа, выполнененных на трех выходных транзисторах (26-28) n-типа, выходы блоков сравнения (33-34) подключены к одноименным входам (43-45) соответствующих транзисторных звеньев (18) блоков свертки (2), выходы (47-49) которых подключены к одноименным входам (51-53) соответствующих транзисторных звеньев (25) первого типа выходного блока (3). 4 ил.

Многоразрядное устройство логического сравнения, содержащее k блоков сравнения и выходной блок, каждый блок сравнения содержит три предзарядовых транзистора р-типа и m логических элементов, каждый из которых выполнен на шести транзисторах n-типа, которые соединены попарно последовательно, причем первый и второй транзисторы n-типа включены между первым и общим выводами логического элемента, третий и четвертый включены между вторым и общим выводами логического элемента, а пятый и второй, шестой и четвертый включены между третьим и общим выводами логического элемента, первые и вторые выводы логических элементов в каждом блоке сравнения соединены соответственно с первым и вторым выходами данного блока, третий вывод логического элемента соединен с общим выводом последующего логического элемента, причем третий вывод последнего из m логических элементов в каждом блоке сравнения соединен с третьим выходом данного блока, объединенные по два затворы первого и шестого, третьего и пятого транзисторов n-типа подключены соответственно к первому и второму входам логического элемента, на которые подаются парафазные сигналы соответствующего разряда первого операнда, затворы второго и четвертого транзисторов n-типа подключены соответственно к третьему и четвертому входам логического элемента, на которые подаются парафазные сигналы одноименного разряда второго операнда, при этом входы первого логического элемента в каждом блоке сравнения соответствуют старшему разряду из соответствующей m-разрядой группы операндов, а входы последнего m-го логического элемента соответствуют младшему разряду той же группы разрядов операндов, в каждом блоке сравнения соответствующий предзарядовый транзистор р-типа включен между шиной питания и одноименным выходом блока сравнения, затворы всех предзарядовых транзисторов р-типа подключены к тактовой шине, а выходной блок содержит три транзистора р-типа, которые включены между шиной питания и соответственно одноименным выходом устройства, затворы которых подключены к тактовой шине, и транзисторные звенья первого типа, каждое из которых содержит три выходных транзистора n-типа, затворы которых подключены к одноименным входам транзисторного звена, причем первый и второй выходные транзисторы n-типа включены общим выводом своего транзисторного звена и соответственно первым и вторым выходами устройства, а третьи выходные транзисторы n-типа включены между общими выводами своего и последующего транзисторных звеньев, третий выходной транзистор n-типа последнего транзисторного звена первого типа включен между третьим выходом устройства и общим выводом этого транзисторного звена, отличающееся тем, что содержит n блоков свертки, каждый из которых содержит три предзарядовых транзистора n-типа, которые включены между шиной земли и одноименным выходом данного блока свертки, и k/n транзисторных звеньев второго типа, каждое из которых содержит три логических транзистора р-типа, затворы которых подключены к одноименным входам транзисторного звена второго типа, первый и второй логические транзисторы р-типа в каждом транзисторном звене второго типа включены между общим выводом своего транзисторного звена и одноименным выходом данного блока свертки, а третьи логические транзисторы р-типа в каждом блоке свертки включены между общими выводами своего и последующего тразисторных звеньев второго типа, причем третий логический транзистор р-типа последнего k/n тразисторного звена второго типа включен между общим выводом своего транзисторного звена и третьим выходом данного блока свертки, а число транзисторных звеньев первого типа в выходном блоке равно n, общие выводы первых логических элементов всех блоков сравнения, общий вывод первого транзисторного звена выходного блока и затворы предзарядовых транзисторов n-типа всех блоков свертки соединены с противофазной тактовой шиной, общие выводы первых транзисторных звеньев второго типа всех блоков свертки соединены с тактовой шиной, выходы блоков сравнения подключены к одноименным входам соответствующих транзисторных звеньев второго типа, причем выходы первого блока сравнения подключены к входам первого транзисторного звена второго типа первого из n блоков свертки, выходы последнего k-го блока сравнения подключены к входам последнего k/n тразисторного звена второго типа последнего n-го блока свертки, выходы блоков свертки подключены к одноименным входам соответствующего транзисторного звена первого типа выходного блока, причем выходы блоков свертки соответствуют одноименным транзисторным звеньям первого типа выходного блока.

| УСТРОЙСТВО СРАВНЕНИЯ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2236696C1 |

| УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ | 1992 |

|

RU2006912C1 |

| Устройство для сравнения чисел | 1986 |

|

SU1376079A1 |

| US 5281946 A, 25.01.1994. | |||

Авторы

Даты

2008-06-27—Публикация

2007-03-02—Подача