Изобретение относится к средствам контроля, управления и сигнализации сложных технических систем, в частности летательных аппаратов (ЛА), и может быть использовано для повышения качества, надежности и безопасности их функционирования.

Целью изобретения является расширение функциональных возможностей устро йства за счет введения в.р,зможнос; и организации уточняющих директив с посдедующей выдачей на устройство для отображения информации по директивм оператора.

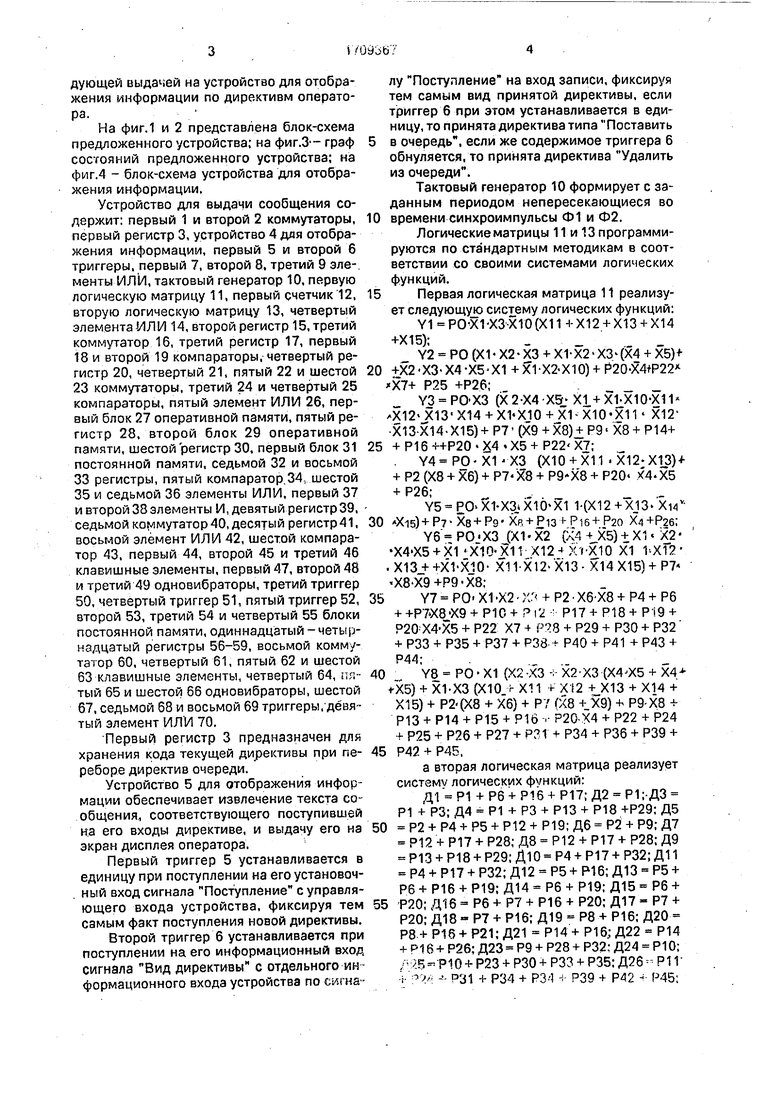

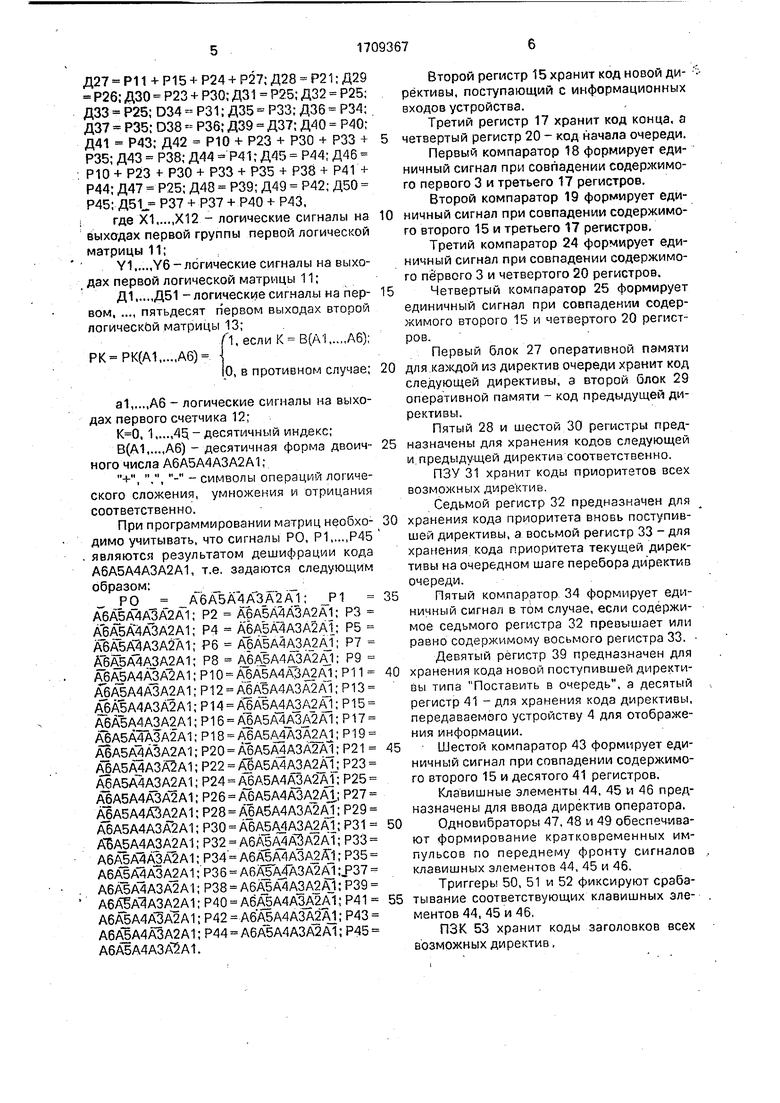

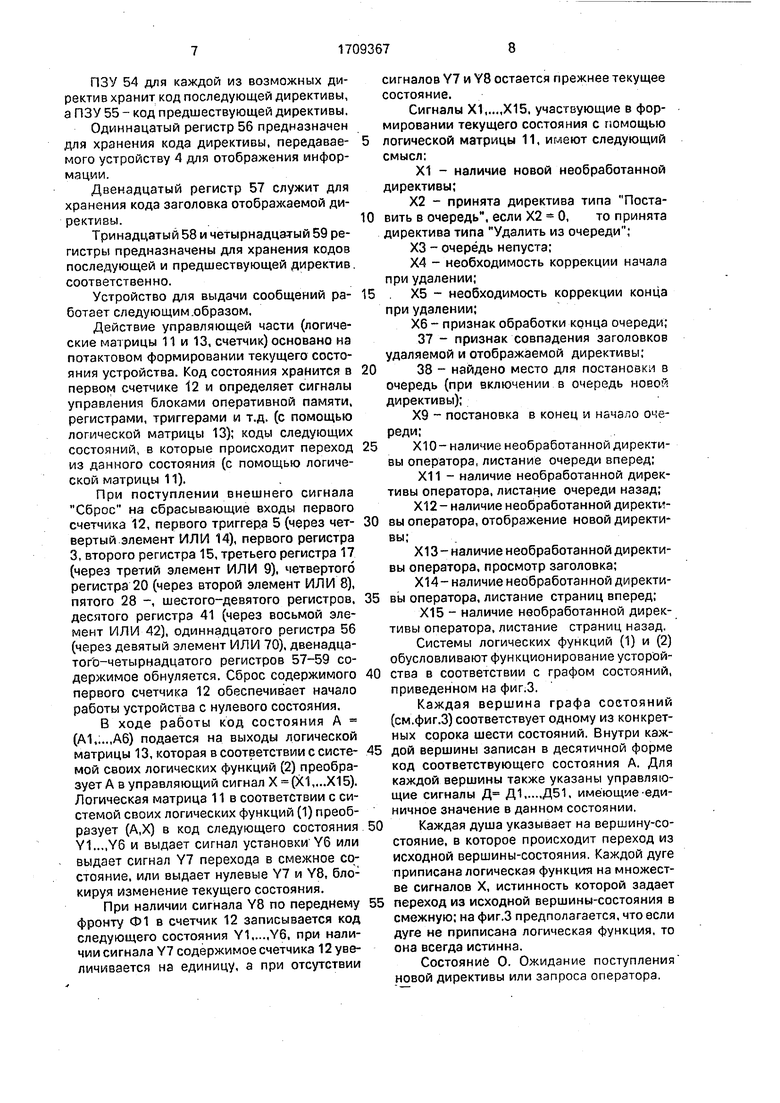

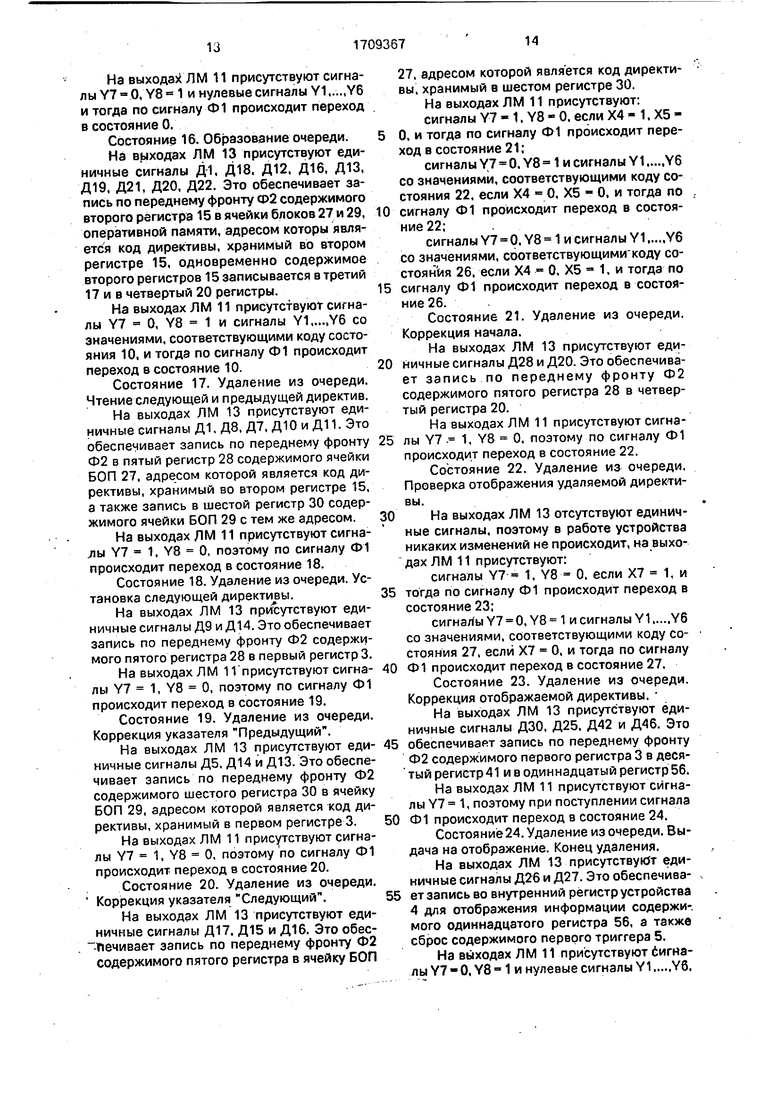

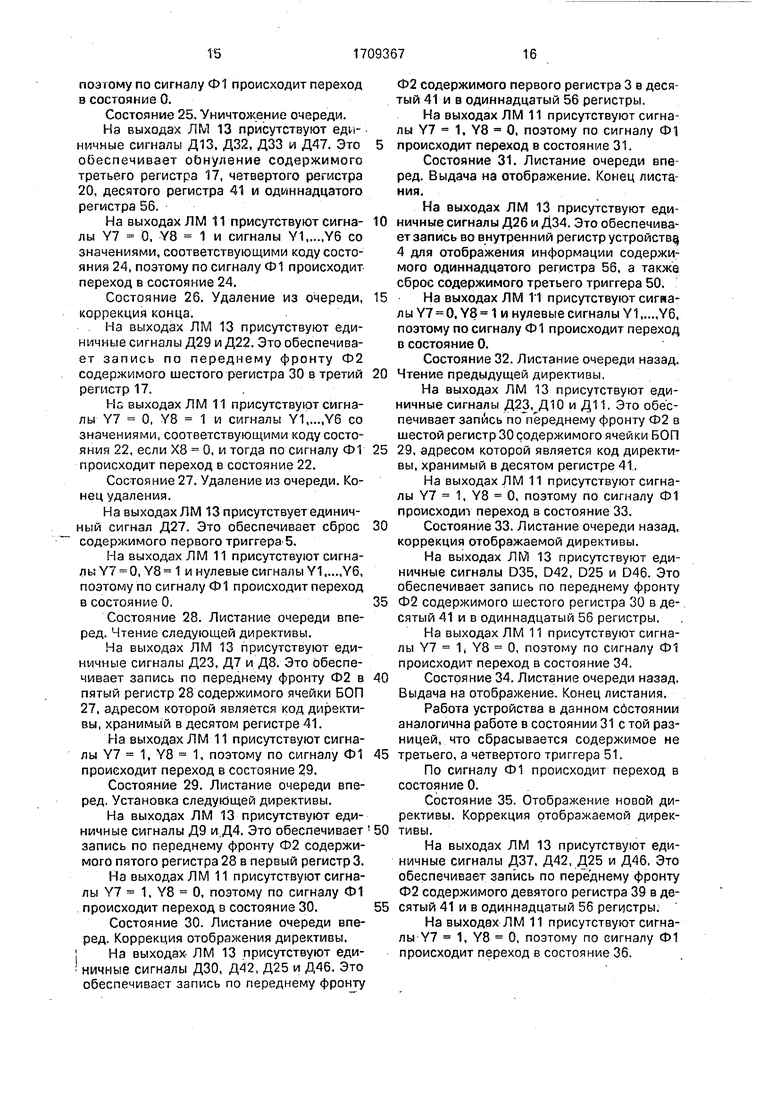

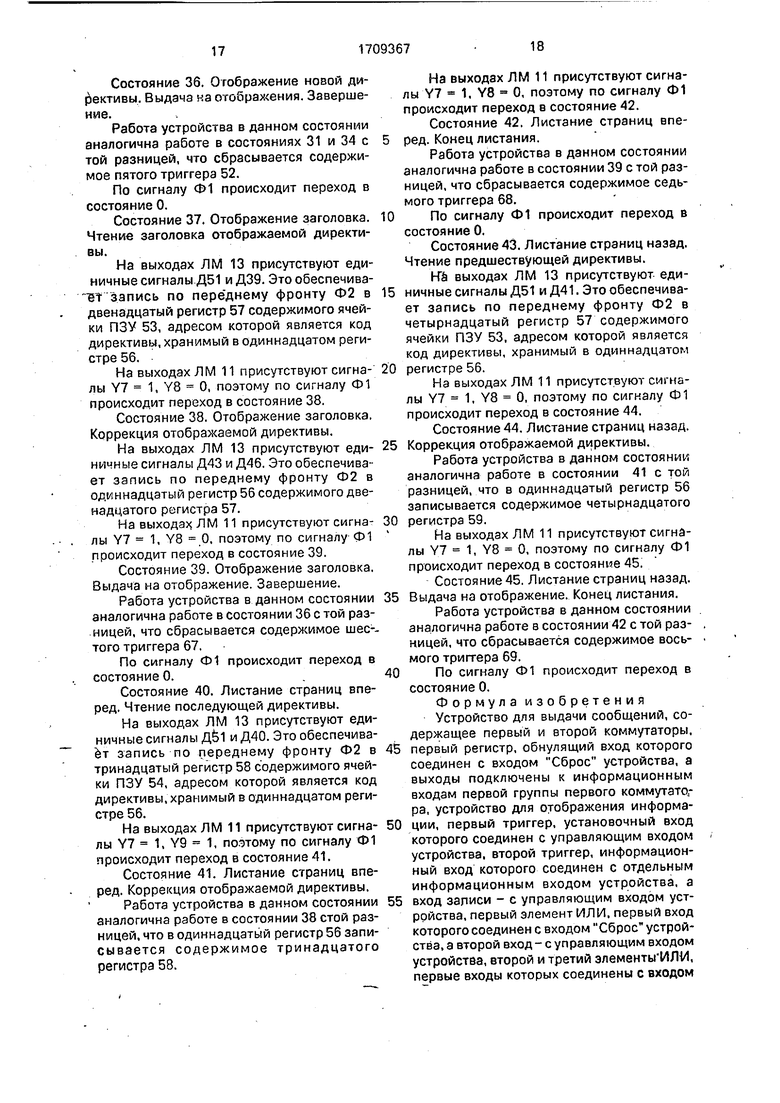

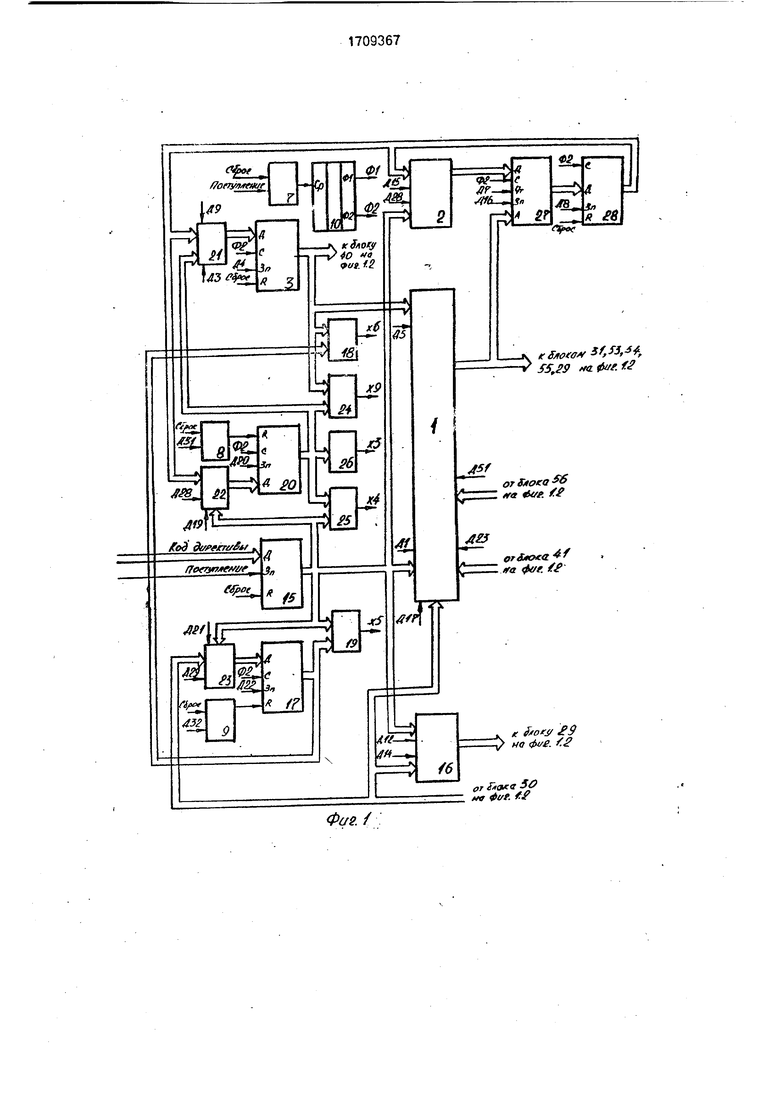

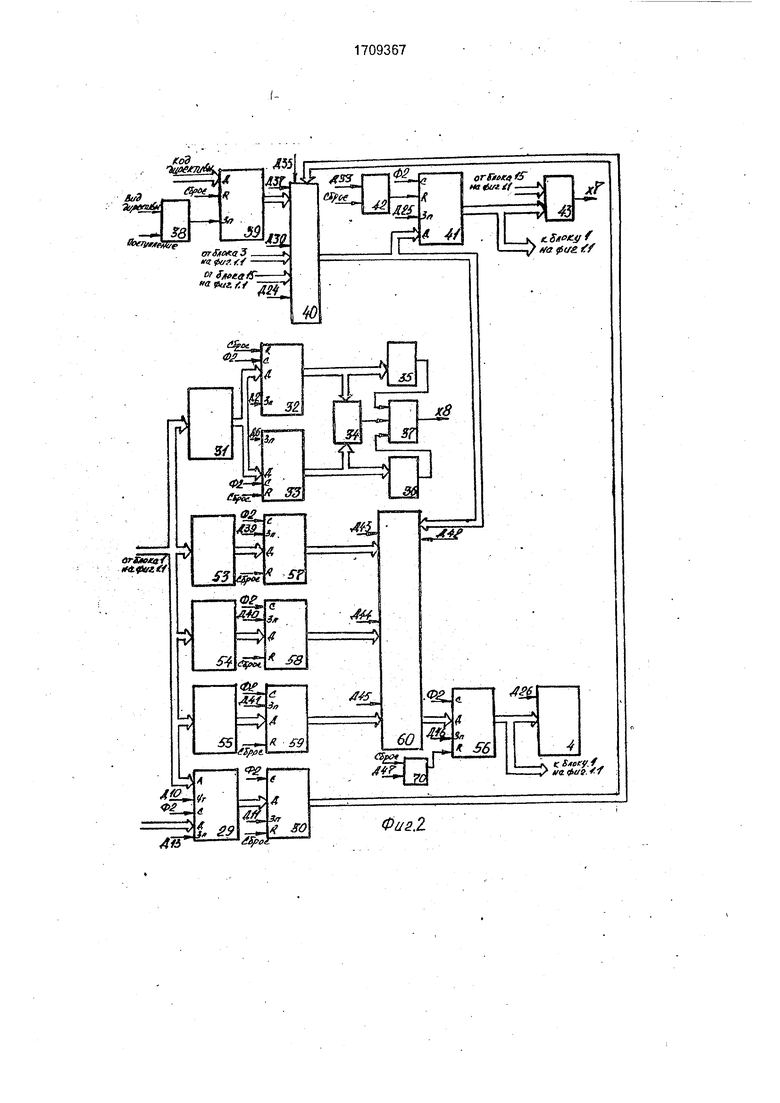

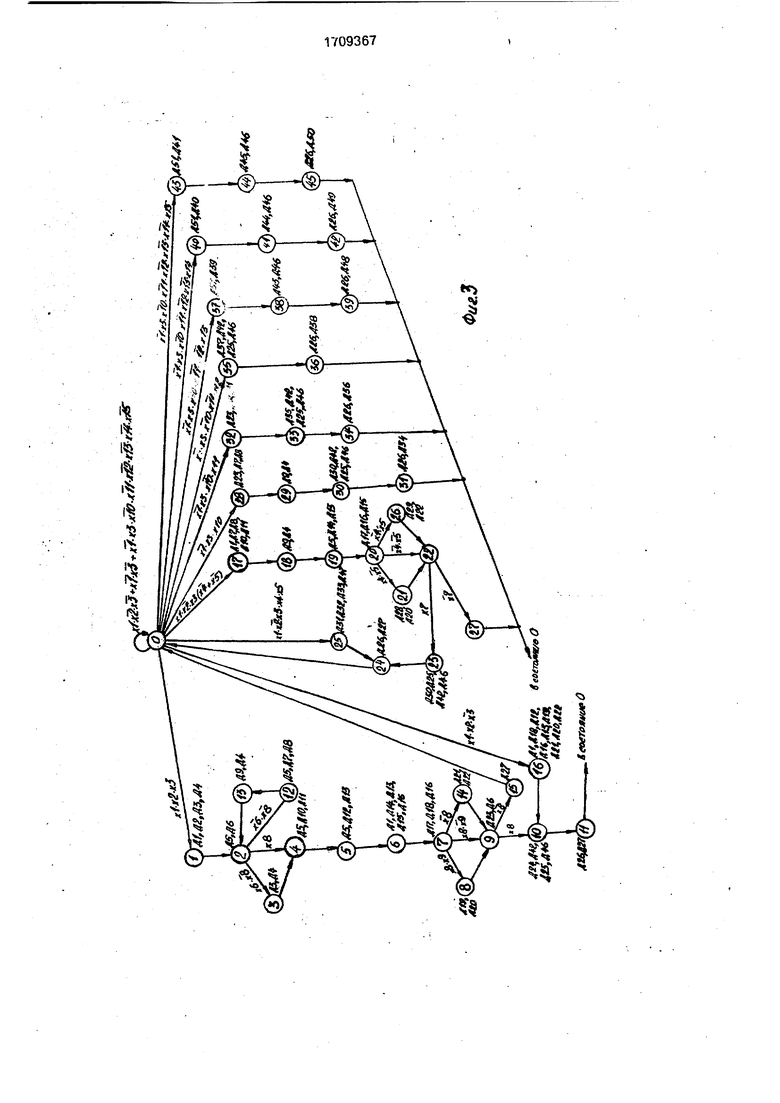

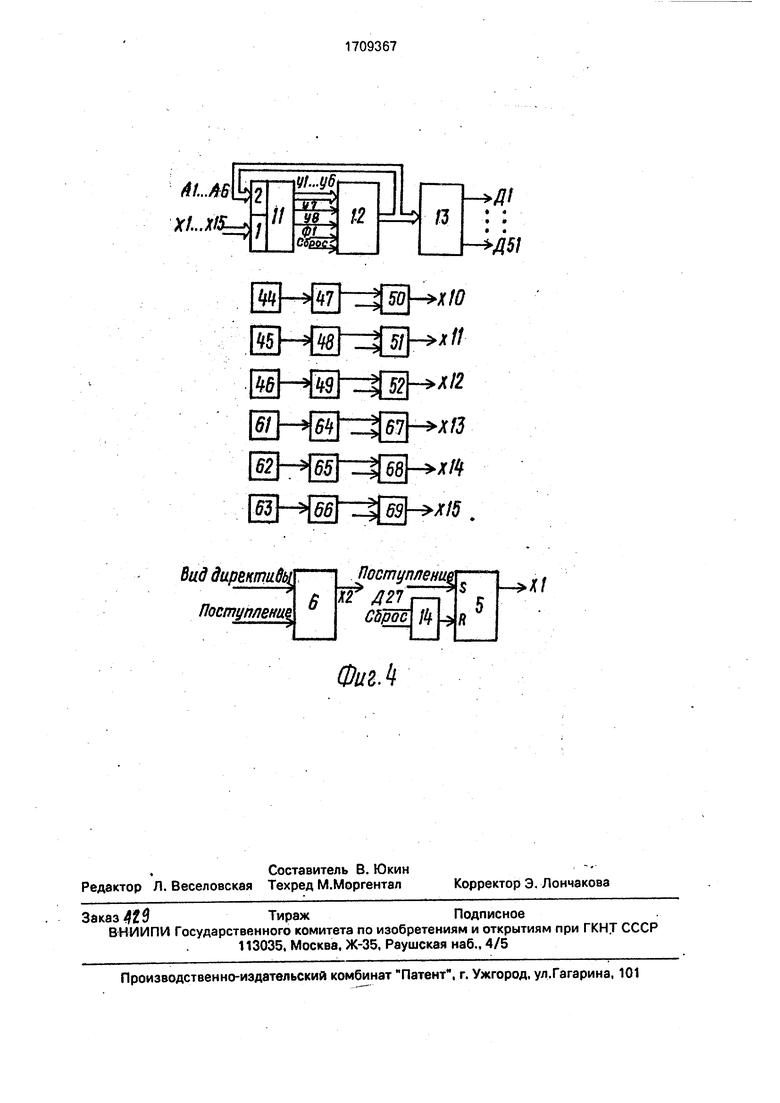

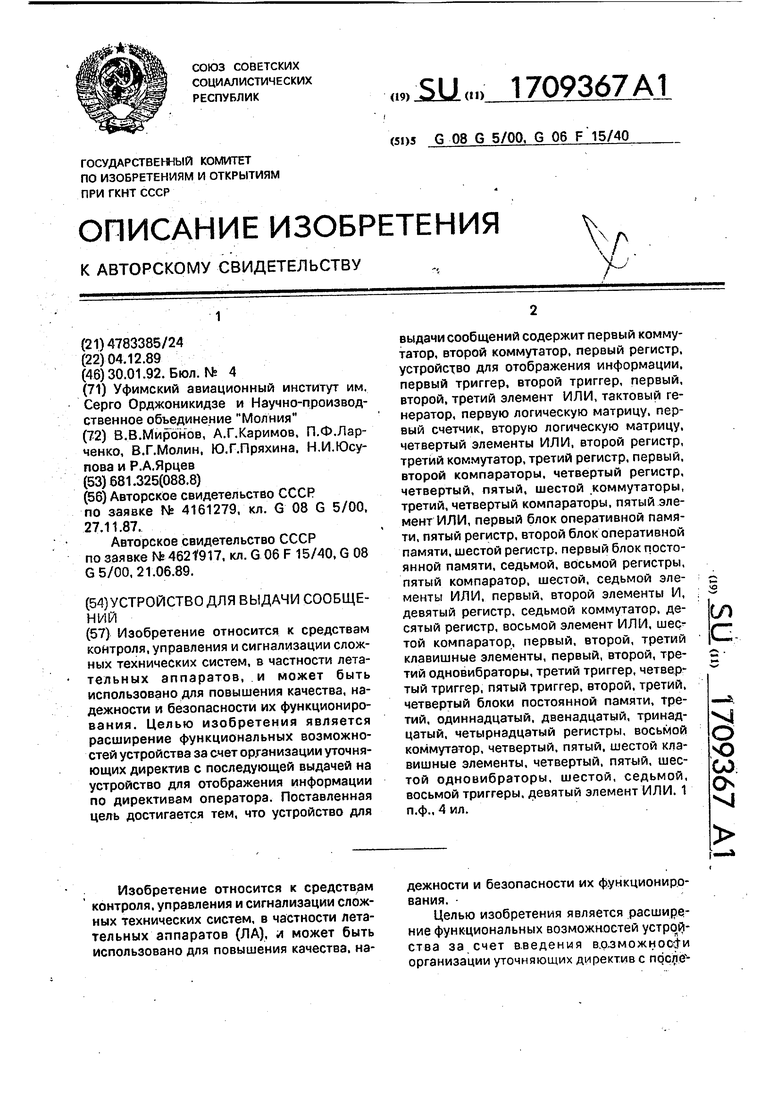

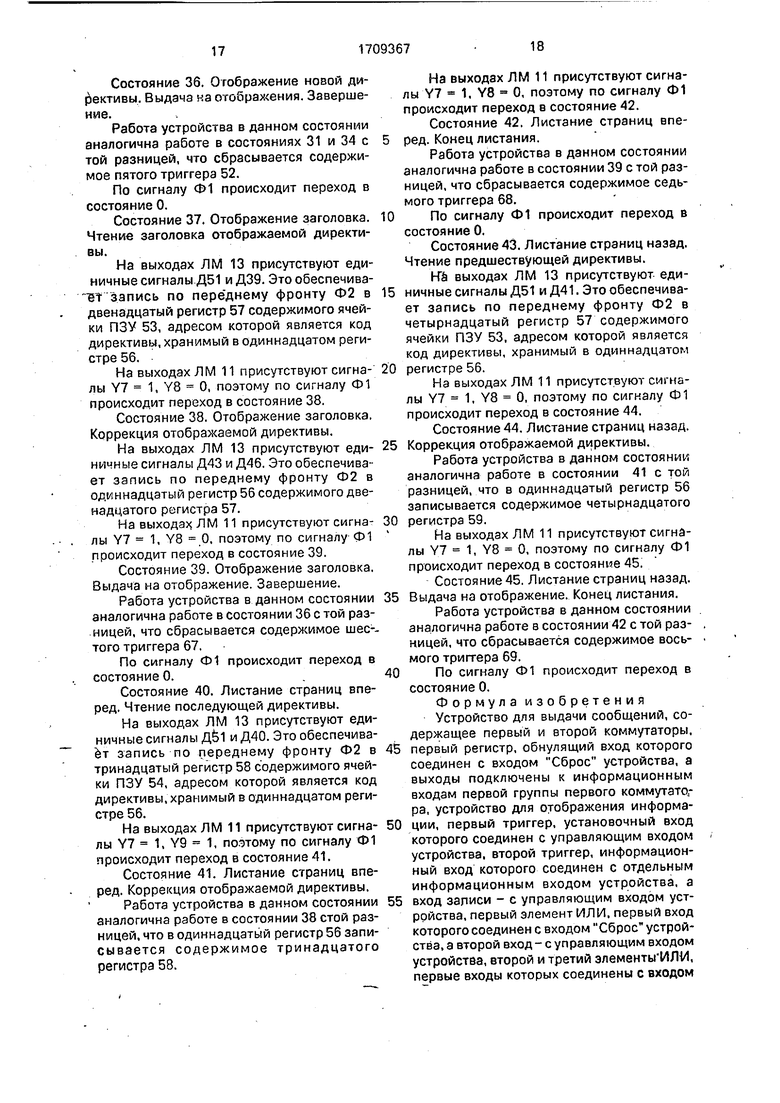

На фиг.1 и 2 представлена блок-схема предложенного устройства; на фиг.З-- граф состояний предложенного устройства; на фиг.4 - блок-схема устройства для отображения информации.

Устройство для выдачи сообщения содержит: первый 1 и второй 2 коммутаторы, первый регистр 3, устройство 4 дня отображения информации, первый 5 и второй б триггеры, первый 7, второй 8. третий 9 эле-, менты ИЛИ, тактовый генератор Ю, первую логическую матрицу 11, первый счетчик 12, вторую логическую матрицу 13, четвертый элемента ИЛИ 14, второй регистр 15, третий коммутатор 16, третий регистр 17, первый 18 и второй 19 компараторы, четвертый регистр 20, четвертый 21, пятый 22 и щестой 23 коммутаторы, третий 24 и четвертый 25 компараторы, пятый элемент ИЛИ 26, первый блок 27 оперативной памяти, пятый регистр 28, второй блок 29 оперативной памяти, шестой регистр 30, первый блок 31 постоянной памяти, седьмой 32 и восьмой 33 регистры, пятый компаратор.34, шестой 35 и седьмой 36 элементы ИЛИ, первый 37 и второй 38элементы И, девятый регистр39, седьмой коммутатор 40, десятый регистр 41, восьмой элемент ИЛИ 42, шестой компаратор 43, первый 44, второй 45 и третий 46 клавишные элементы, первый 47, второй 48 и третий 49 одновибраторы, третий триггер 50, четвертый триггер 51, пятый триггер 52, второй 53, третий 54 и четвертый 55 блоки постоянной памяти, одиннадцатый - четырнадцатый регистры 56-59, восьмой коммутатор 60, четвертый 61, пятый 62 и щестой 63 клавишные элементы, четвертый 64, пятый 65 и шестой 66 одновибраторы, шестой 67, седьмой 68 и восьмой 69 триггерьпдёвятый элемент ИЛИ 70,

Первый регистр 3 предназначен для хранения кода текущей директивы при переборе директив очереди.

Устройство 5 для отображения информации обеспечивает извлечение текста сообщения, соответствующего поступившей на его входы директиве, и выдачу его на экран дисплея оператора.

Первый триггер 5 устанавливается в единицу при поступлении на его установочный вход сигнала Поступление с управляющего входа устройства, фиксируя тем самым факт поступления новой директивы.

Второй триггер 6 устанавливается при поступлении на его информационный вход сигнала Вид директивы с отдельного информационного входа устройства по сигналу Поступление на вход записи, фиксируя тем самым вид принятой директивы, если триггер 6 при этом устанавливается в единицу, то принята директива типа Поставить в очередь, если же содержимое триггера 6 обнуляется, то принята директива Удалить из очереди.

Тактовый генератор 10 формирует с заданным периодом непересекающиеся во 0 времени синхроимпульсы Ф1 и Ф2.

Л огические матрицы 11 и 13 программируются по стандартным методикам в соответствии со своими системами логических функций.

5 Первая логическая матрица 11 реализует следующулр систему логических функций: Y1 РОХ1-ХЗ-Х10 (X11 н- Х12 + Х13 + Х14 +Х15)

Y2 РО (XI«Х2 ХЗ + Х1- Х2 ХЗ (Х4 + Х5) 0 +Х2ХЗ-Х4-Х5Х1 +Х1-Х2-Х10) + P20X4tP22 Х7+ Р25 +Р26;

Y3 POX3 (Х2-Х4 Х5Г-Х1 +Х1-Х10-Х11Х12Х13Х14 + Х1Х10 + ХЬХ10Х11 Х12 -Х13-Х14.Х15)+Р7(Х9 + Х8)+Р9Х8 + Р14+ 5 +Р16++Р20Х4«Х5+Р22 Х7;

. У4 Рр-Х1ХЗ (Х10 + Х11 .Х12-Х13) + Р2 (Х8 + Х6) + Р7Х8 + Р9-Х8 + Р20 Х4.Х5 + Р26;

y5 POX1-X3jXlb X1 1-(X12 + XJ3.Xi40 X15)+P7X8+P9 Xp, + Pl3+Pl6+P20 X4+P26;

У6 РО«ХЗ (X1-X2 (X4-(-X5) + X1. X2X4X5 + XI xlO X11 X12 + 1 1-Xf2 .X13 ++X1-XJO- Xl1-Xl2-X13-Xl4X15) + P7 X8-X9+P9X8;

b У7 PO- X1 X2 X. + P2 X6X8 + P4 + P6 + +P7X8X9 + P10+ Pi2 P17 + P18+P19 + P20 X4X5 + P22 X7 + + P29 + P30 + P32 + P33 + P35 + P37 + P38 f P40 + P41 + P43 + P44:.

0У8 PO X1 (X2 -ХЗ -; X2 X3 ( + X4/fX5) -I- X1-X3 (X10 r XII + Xi2 +.X13 + X14 + X15) + P2(X8 + X6) + P7 (X8 + X9) -ь P9-X8 + P13 + P14 + P15 + P16 - P20.X4 + P22 + P24 + P25 + P26 + P27 + РЗГ + P34 + P36 + P39 + 5 P42 + P45.

a вторая логическая матрица реализует систему логических ф /нкций:

Д1 Р1 +Р6 + Р1Ь + Р17; Д2 Р1;-ДЗ Р1 + РЗ; Д4 Р1 + РЗ + Р13 + Р18 +Р29; Д5 0 Р2 + Р4 + Р5 + Р12 + Р19; Д6 Р2 + Р9; Д7 Р12 + Р17 + Р28; Д8 Р12 + Р17 + Р28; Д9 Р13 + Р18 + Р29;Д10 Р4 + Р17 + Р32;Д11 Р4 + Р17 + Р32; Д12 Р5 + Р16; Д13 Р5 + ре + Р16 + Р19; Д14 Р6 + Р19; Д15 Р6 + 5 Р20; Д16 Р6 + Р7 + Р16 + Р20; Д17 - Р7 + Р20; Д18 - Р7 + Р16; Д19 Р8 + Р16; Д20 Р8.+ Р1б + Р21; Д21 Р14 + Р16.; Д22 Р14 + Р16 + Р26; Д23 Р9 + Р28 + Р32; Д24 Р10; гх5- РЮ-ь Р23 + РЗО + РЗЗ + Р35; Д26 - Р1 Г :;. - Р31 + Р34 + Р34 + Р39 + Р42 -I Р45:

Д27 Р11 + Р15 + Р24 -f- Р27: Д28 Р21; Д29 Р26; ДЗО Р23 + РЗО; Д31 Р25; Д32 Р25; Д33 Р25; 034 Р31; Д35 РЗЗ; Д36 Р34; Д37 Р35; D38 - РЗб; Д39 Д37: Д40 Р40: Д41 Р43; Д42 Р10 + Р23 -I- РЗО + РЗЗ + Р35;Д43 Р38,-Д44-Р41:Д45 Р44;Д46 Р10 + Р23 РЗО + РЗЗ + Р35 + Р38 + Р41 + Р44; Д47 Р25; Д48 Р39; Д49 Р42; Д50 Р45; Д5 Р37 + Р37 + Р40 + Р43,

где XIXI2 - логические сигналы на

быхсдах первой группы первой логической матрицы 11;

Y1,...,Y6-логические сигналы на выходах первой логической матрицы 11;

Д1Д51-логическиесигналы на первом, ..., пятьдесят Нервом выходах второй логический матрицы 13;

р.если К В(А1А6);

(А1А6)

io, в противном случае;

a1,...,A6 - логические сигналы из выходах первого счетчика 12;

. 14Ц-десятичный индекс;

В(А1А6) - десятичная форма двоичного числа А6А5А4АЗА2А1;

+, ,,- - символы операций логического сложения, умножения и отрицания соответственно.

При программировании матриц необходимо учитывать, что сигналы РО, Р1Р45

являются результатом дешифрации кода А6А5А4АЗА2А1, т.е. задаются следующим образом: „

РО А6А5А4А ЗА2А1; Р1 А6А5А4АЗА2А1; Р2 А5А5А4АЗА2А1; РЗ А6 5МАЗА2А1; Р4 А бА5А4АЗА2А1; Р5 А6А5А АЗА2А1; Р6 A 6A5A4A3A 2Aj; Р7 Д6А5А4АЗА 2А1; Р8 А6А5А4АЗА2А1; Р9 А6А5А4АЗА2А1; Р10 А6А5А4АЗА2А1; Р11 А6А5А4АЗА2А1; Р12 AjA 5A4A3А2А1; Р13 А6А5А4АЗА2А1; Р14 AJASAJAJА2 AJ; Р15 А6А5А4АЗА2А1; Р16 А6А5А4АЗА2А1; Р17 А5А 4АЗА2А1; Р18 А6А5,МАЗAMI; Р19 А6А5МАЗА2А1; Р20 АбА5А АЗА2/М; Р21 А6А5А4АЗА2А1; Р22 А6А5А4АЗА2 А1; Р23 AJA5A4A3A2A1; Р24 A6A5A4A3A2AJ; Р25 А6А5А4АЗА2А1; Р26 AJ6A5A4A3A 2A1; Р27 А6А5А4АЗА2А1; Р28 А6А5А4АЗА2А1; Р29 АбА5А4АЗА2А1; РЗО АбА 5А4АЗА А.1; Р31 А БА5А4АЗА2А1; Р32 ,4/ A2Al; РЗЗ А6А5АЗАЗА2А1; Р34 А6А5А4АЗА 2Д1; Р35 А6А 5А 4АЗА2А1; Р36 А6/№А;4АЗА2А1 А6А5А4АЗА2А1; Р38 А6А5А4АЗА2А1; Р39 A6ABAlA3AJA1; Р40 А6А5А4АЗ А2А1; Р41 А6А|А4АЗА2А1; Р42 А6А А4АЗAjA,; Р43 А6А5А4АЗА2А1; Р44 А6А5А4АЗА2А1; Р45 А6А5А4АЗА5А1.

Второй регистр 15 хранит код новой директивы, поступающий с информационных входов устройства.

Третий регистр 17 хранит код конца, а четвертый регистр 20 - код начала очереди.

Первый компаратор 18 формирует единичный сигнал при совпадении содержимого первого 3 и третьего 17 регистров.

Второй компаратор 19 формирует единичный сигнал при совпадении содержимого второго 15 и третьего 17 регистров.

Третий компаратор 24 формирует единичный сигнал при совпадении содержимого первого 3 и четвертого 20 регистров. Четвертый компаратор 25 формирует единичный сигнал при совпадении содержимого второго 15 и четвертого 20 регистров.

Первый блок 27 оперативной памяти для каждой из директив очереди хранит код следующей директивы, а второй блок 29 оперативной памяти - код предыдущей директивы.

Пятый 28 и шестой 30 регистры предназначены для хранения кодов следующей и.предыдущей директив соответственно.

ПЗУ 31 хранит коды приоритетов всех возможных директив,

Седьмой регистр 32 предназначен для хранения кода приоритета вновь поступившей директивы, а восьмой регистр 33 - для хранения кода приоритета текущей директивы на очередном шаге перебора директив очереди.

Пятый компаратор 34 формирует единичный сигнал в том случае, если содержимое седьмого регистра 32 превышает или равно содержимому восьмого регистра 33.

Девятый регистр 39 предназначен для хранения кода новой поступившей директивы типа Поставить в очередь, а десятый регистр 41 - для хранения кода директивы, передаваемого устройству 4 для отображения информации.

Шестой компаратор 43 формирует единичный сигнал при совпадении содержимого второго 15 и десятого 41 регистров.

Клавишные элементы 44, 45 и 46 предназначены для ввода директив оператора. Одновибраторы 47. 48 и 49 обеспечивают формирование кратковременных импульсов по переднему фронту сигналов клавишных элементов 44, 45 и 46.

Триггеры 50, 51 и 52 фиксируют срабатывание соответствующих клавишных элементов 44, 45 и 46,

ПЗК 53 хранит коды заголовков всех возможных директив, ПЗУ 54 для каждой из возможных директив хранит код последующей директивы, а ПЗУ 55 - код предшествующей директивы. Одиинацатый регистр 56 предназначен для хранения кода директивы, передаваемого устройству 4 для отображения информации. Двенадцатый регистр 57 служит для хранения кода заголовка отобрах аемой директивы. Тринадцатый 58 и чetыpнaдцaтый 59 регистры предназначены для хранения кодов последующей и предшествующей директив, соответственно. Устройство для выдачи сообщений работает следующим.образом. Действие управляющей части (логические матрицы 11 и 13, счетчик) основано на потактовом формировании текущего состояния устройства. Код состояния хранится в первом счетчике 12 м определяет сигналы управления блоками оперативной памяти, регистрами, триггерами и т,д. (с помощью логической матрицы 13); коды следующих состояний, в которые происходит переход из данного состояния (с помощью логической матрицы 11). При поступлении внешнего сигнала Сброс на сбрасывающие входы первого счетчика 12, первого триггера 5 (через четвертый элемент ИЛИ 14), первого регистра 3, второго регистра 15, третьего регистра 17 (через третий элемент ИЛИ 9). четвертого регистра 20 (через второй элемент ИЛИ 8), пятого 28 -, шестого-девятого регистров, десятого регистра 41 (через восьмой элемент ИЛИ 42), одиннадцатого регистра 56 (через девятый элемент ИЛИ 70), двенадцатого-четырнадцатого регистров 57-59 содержимое обнуляется. Сброс содержимого первого счетчика 12 обеспечивает начало работы устройства с нулевого состояния. В ходе работы код состояния А (А1,;..,А6) подается на выходы логической матрицы 13, которая в соответствии с системой своих логических функций (2) преобразует А в управляющий сигнал X (Х1 ,.,.Х15). Логическая матрица 11 в соответствии с системой своих логических функций (1) преобразует (А,Х) в код следующего состояния Y1...,Y6 и выдает сигнал установкиY6 или выдает сигнал Y7 перехода в смежное состояние, или выдает нулевые Y7 и Y8, блокируя изменение текущего состояния. При наличии сигнала Y8 по переднему фронту Ф1 в счетчик 12 записывается код следующего состояния Y1Y6, при наличии сигнала Y7 содержимое счетчика 12 увеличивается на единицу, а при отсутствии сигналов Y7 и Y8 остается прежнее текущее состояние. Сигналы Х1,...,Х15, участвующие в формировании текущего состояния с помощью логической матрицы 11, имеют следующий смысл: XI- наличие новой необработанной директивы; Х2 - принята директива типа Поставить в очередь, если Х2 О, то принята директива типа Удалить из очереди ; ХЗ - очередь непуста: Х4 - необходимость коррекции начала при удалении; . Х5 - необходимость коррекции конца при удалении; Х6 - признак обработки конца очереди; 37 - признак совпадения заголовков удаляемой и отображаемой директивы; 38 - найдено место для постановки в очередь (при включении в очередь новой директивы); Х9 - постановка в конец и начало очереди;Х10-наличие необработанной директивы оператора, листание очереди вперед; XII- наличие необработанной директивы оператора, листание очереди назад; Х12-наличие необработанной директивы оператора, отображение новой директивы;XI3 - наличие необработанной директивы оператора, просмотр заголовка; Х14- наличие необработанной директивы оператора, листание страниц вперед; Х15 - наличие необработанной директивы оператора, листание страниц назад, Системы логических функций (1) и (2) обусловливают функционирование усторойства в соответствии с графом состояний, приведенном на фиг.З. Каждая вершина графа состояний (см.фиг.З) соответствует одному из конкретных сорока шести состояний. Внутри каждои вершины записан в десятичной форме код соответствующего состояния А. Для каждой вершины также указаны управляющие сигналы Д Д1ДБ1, имеющие-единичное значение в данном состоянии. Каждая душа указывает на вершину-состояние, в которое происходит переход из исходной вершины-состояния. Каждой дуге приписана логическая функция на множестве сигналов X, истинность которой задает переход из исходной вершины-состояния в смежную; на фиг.З предполагается, что если дуге не приписана логическая функция, то она всегда истинна. Состояние о. Ожидание поступления новой директивы или запроса оператора.

На выходах логической матрицы 13 отсутствуют единичные сигналы, поэтому в работе устройства никаких изменений не происходит.

На выходах ЛК/1 11 присутствуют:

сигналы Y7 1, Y8 О, если XI Х2 ХЗ 1, и тогдапо сигналу Ф1 происходит переход в состояние 1;

сигналы Y7 О, иcигнaлыY1Y6

со значениями, соответствующими коду состояния 16, если Х1 Х2 1, ХЗ О, м тогда по сигналу Ф1 происходит переход в состояние 16;

сигналы Y7 О, иcигнaлыY1Y6

со значениями, соответствующими коду состояния 25, если Х1 ХЗ - Х4 Х5 1. Х2 О, и тогда по сигналу Ф1 происходит переход в состояние 25;

сигналы .Y8 1 и сигналы Y1,,..,Y6 со значениями, соответствующими коду состояния 17, если Х1 ХЗ 1 : Х2 Х4 О или

XI ХЗ 1, Х2 Х5 О, и тогда пс сигналу Ф1 происходит переход в состояние 17;

сигналы Y7 О, Y8 1 и сигналы Y1,..,,Y6 со значениями, соответствующимм коду состояния 28, если 1 :Х1 0,11 тогда по сигналу Ф1 происходит переход в состояние 28;

сигналы , Y8 1 и сигналы Y1,...,Y6 со значениями, соответствующими коду состояния 32, если.Х3 XII 1, Х1 Х10 О, И тогда по сигналу Ф1 происходит переход в состояние 32;

сигналы Y7 О, Y8 1 и сигналы Y1/6

со значениями, соответствующими коду состояния 35, если ХЗ Х12 Х1, Х1 Х10

XII О, и тогда по сигналу Ф1 происходит переход в состояние 35;

сигналы Y7 О, Y8 О, если Х1 1, Х2 ХЗ ОилиХ1 Х10 Х11 Х12 Х13 Х14 Х15 О, И.ЛИ Х1 ХЗ О, ХЗ 1, и тогда состояние на данном такте не меняется.

Состояние 1. Включение в очередь. Чтение приоритета пришедшей директивы. Установка начала для перебора очереди.

На выходах ЛМ 13 присутствуют единичные сигналы Д1 ,Д2, ДЗ, Д4. Это обеспечивает запись по переднему фронту сигнал Ф2 содержимого ячейки ПЗУ 31, адресом которой является код пришедшей директивы, хранимый во втором регистре 15, в седьмой регистр 32, а также запись содержимого четвертого регистра 20 в первый регистр 3.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 2.

Состояние 2: Включение в очередь. Чтение приоритета директивы, обрабатываемой на очередном шаге перебора очереди.

На выходах ЛМ 13 присутствуют единичные сигналы Д5 и Д6. Это обеспечивает запись по переднему фронту Ф2 содержимого ячейки ПЗУ 31, адресом которой является код директивы, хранимый в первом регистре 3, в восьмой регистр 33.

На выходах ЛМ 11 присутствуют;

сигналы Y7 О, Y8 О, если Х5 1. Х8 О, и тогда по сигналу Ф1 происходит переход в состояние 3;

сигналы Y7 0,Y8 1 и сигналы Y1Y6

со значениями, соответствующими коду состояния 4, еслиХ8 1, и тогда по сигналу Ф1 происходит переход в состояние 4;

5 сигналы Y7 0, и сигналы Y1Y6

со значениями, соответствующими коду состояния 12, если Х6 Х8 О, и тогда по сигналу Ф1 происходит переход в состояние 12.

0 Состояние 3: Включение в очередь. Установка начала для включения в конец очереди.

На выходах ЛМ 13 присутствуют единичные сигналы ДЗ и Д4. Это обеспечивает 5 запись, по переднему фронту Ф2 содержимого четвертого регистра 20 в первый регистр 3.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 0 происходит переход в состояние 4.

Состояние 4. Включение в очередь. Чтение предыдущей директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Д5,Д10, Д11 . Это обеспечивает запись по переднему фронту Ф2 содержимого ячейки блока 29 оперативной памяти, адресом которой является код директивы, хранимый в первом perviCTpe 3, в шестой регистр 30.

0На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 5.

Состояние 5; Включение в очередь. Коррекция указателя Предыдущий. 5 На выходах ЛМ 13 присутствуют единичные сигналы Д5,Д 12 и Д13,. Это обеспечивает запись по переднему фронту Ф2 содержимого ячейки, адресом которой является код директивы, хранимый в первом ре0 гистреЗ.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 6.

Состояние 6. Включение в очередь. Кор5 рекция.указателя Следующий и предыдущий.

На выходах ЛМ 13 присутствуют единичные сигналы Д1,Д3-Д16. Это обеспечивает запись по переднему фронту Ф2 содержимого пятого регистра 28 и ячейку

блока оперативной памяти 29. адресом которой является код директивы, хранимый во втором регистре 15, и запись содержимого шестого регистра 30 в ячейку блока 29 оперативной памяти с тем же адресом,

На выходах Л М 11 присутствуют сигналы Y7 1, поэтому по сигналу Ф1 происходит переход в состояние 7.

Состояние 7. Включение в очередь. Коррекция указателя Следующий.

На выходах ЛМ 13 присутствуют единичные сигналы Д17, Д18 и jfl16. Это обеспечивает запись по переднему фронту Ф2 содержимого второго регистра 15 в ячейку блока 27 оперативной памяти, адресом которой является код директивы, хранимый в шестом регистре 30,

На выходах ЛМ 11 присутствуют:

сигналы Y7- 1, , еслиХ8 Х9 1, и тогда по сигналу Ф1 происходит переход в состояние 8;

сигналы Y7 О, У8 1 и сигналы Y1 ,,..,Y6 со значениями, соответствующими коду состояния 9, если Х8 1, Х9 О, и тогда по сигналу Ф1 происходит переход в состояние 9;

сигналы Y7 О, Y8 1 и сигналы Y1Y6

со значениями, соответствующими коду состояния 14, если Х8 О, и тогда по сигналу Ф1 происходит переход в состояние 14.

Состояние 8. Включение в очередь. Коррекция начала.

На выходах ЛМ 13 присутствуют единичные сигналы Д19 и Д20. Это обеспечивает запись по переднему фронту Ф2 содержимого второго регистра 15 в четвертый регистр 20.

На выходах ЛМ 11 присутствуют сигна-лы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 9.

Состояние 9. Включение в очередь. ЧтеЛие приоритета, отображаемой директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Д23 и Дб. Это обеспечивает запись по переднему фронту Ф2 в восьмой регистр 33 содержимго ячейки ПУЗ 31. адресом которой является код директивы, хранимый в десятом регистре 41,

На выходах ЛМ 11 присутствуют:

сигналы Y7 1. Y8 0. если Х8 1. и тогда по сигналу Ф1 происходит переход в состояние 10;

сигналы Y7 О, Y8 1 и сигналы Y1.,.,.Y5 со значениями, соответствующими коду состояния 15, если Х8 О, и тогда по сигналу Ф1 происходит переход в состояние 15,

Состояние 10, Включение в очередь. Коррекция отображаемой директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Д24, Д42, Д25 и Д46. Это

обеспечивает запись по переднему фронту Ф2 в десятый регистр 41 и одиннадцатый регистр 56 содержимого второго регистра 15.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 0. поэтому по сигналу Ф1 происходит переход в состояние 11,

Состояние 11. Включение в очередь. Выдача на отображение. Конец включения.

На выходах Л М 13 присутствуют едиичные сигнады Д26 и Д27, Это обеспечивает запись во внутренний регистр устройства 4 для отображения информации содержимого одиннадцатого регистра 56. а также

сброс содержимого Первого триггера 5,

На выходах ЛМ 11 присутствуют сигналы Y7 0. Y8 1, и нулевые сигналы Y1 ,,,,,Y6, поэтому по сигналу Ф1 происходит переход в состояние О,

Состояние 12, Включение в очередь. Чтение следующей директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Д5, Д7 и Д8, Это обеспечивает запись по переднему фронту Ф2 в

пятый регистр 28 содержимого ячейки блока 27 оперативной памяти, адресом которой является код директивы, хранимый в первом регистре 3,

На выходах ЛМ 11 присутствуют сигналы Y7 1. Y8 0. поэтому по сигналу Ф1 происходит переход в состояние 13,

Состояние 13, Включение в очередь. Установка следующего для перебора очереди. На выходах ЛМ 13 присутствуют единичные сигналы Д9 и Д4, Это обеспечивает запись по переднему фронту Ф2 в первый, регистр 3 содержимого пятого регистра 28. На выходах ЛМ 11 присутствуют сигналы Y7 Oi Y8 1 и сигналы Y1Y6 со

значениями, соответствующими коду состояния 2, и тогда по сигналу Ф1 происходит переход в состояние 2.

Состояние 14, Включение в очередь, Коррекция конца,

На выходах ЛМ 13 присутствуют еди- ничные сигналы Д21 иД22. Это обеспечива- ет запись по переднему фронту Ф2 в третий регистр 17 содержимого второго регистра 15,

На выходах ЛМ 11 присутствуют сигналы Y7 0. Y8 1 и сигналы Y1Y6 со

значениями, соответствующими коду состояния 9, и тогда по сигналу Ф1 происходит переход в состояние 9.

Состояние 15, Включение в очередь, Конец включения,

На выходах Л М13 присутствует единичный сигнал Д27, Это обеспечивает сброс содержимого первого триггера 5.

На выхода ЛМ 11 присутствуют сигналы Y7 О, 8 1 и нулевые сигналы Y1....,Y6 и тогда по сигналу Ф1 происходит переход . в состояние 0.

Состояние 16. Образование очереди. 5

На вь|ходах ЛМ 13 присутствуют единичные сигналы Д1, Д18. Д12, Д16. Д13, 19. Д21, Д20, Д22. Это обеспечивает запись по переднему фронту Ф2 содержимого второго регистра 15 в ячейки блоков 27 и 29, 10 оперативной памяти, адресом которы является код директивы, хранимый во втором регистре 15, одновременно содержимое второго регистров 15 записывается в третий 17 и в четвертый 20 регистры.15

На выходах ЛМ 11 присутствуют сигналы Y7 О, Y8 1 и сигналы Y1,...,Y6 со значениями, соответствующими коду состояния 10, и тогда по сигналу Ф1 происходит переход в состояние 10.20

Состояние 17. Удаление из очереди. Чтение следующей и предыдущей директив.

На выходах ЛМ 13 присутствуют единичные сигналы Д1. Д8. Д7, Д10 и Д11. Это обеспечивает запись по переднему фронту 25 Ф2 в пятый регистр 28 содержимого ячейки БОП 27, адресом которой является код директивы, хранимый во втором регистре 15, а также запись в шестой регистр 30 содержимого ячейки БОП 29 с тем же адресом. 30

На выходах ЛМ 11 присутствуют сигнаы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 18.

Состояние 18. Удаление из очереди. Установка следующей директивы.35

На выходах ЛМ 13 присутствуют единичные сигналь Д9 и Д14. Это обеспечивает запись по переднему фронту Ф2 содержимого пятого регистра 28 в первый регистр 3.

На выходах ЛМ 11 присутствуют сигна- 40 лы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 19.

Состояние 19. Удаление из очереди. Коррекция указателя Предыдущий.

На выходах ЛМ 13 присутствуют еди- 45 ничные сигналы Д5. Д14 и Д13. Это обеспечивает запись по переднему фронту Ф2 содержимого шестого регистра 30 в ячейку БОП 29, адресом которой является код директивы, хранимый в первом регистре 3. 50

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 20.

Состояние 20. Удаление из очереди. Коррекция указателя Следующий.55

На выходах ЛМ 13 присутствуют единичные сигналы Д17, Д15 и Д16. Это обесПечивает запись по переднему фронту Ф2 содержимого пятого регистра в ячейку БОП

27, адресом которой является код директивы, хранимый в шестом регистре 30.

На выходах ЛМ 11 присутствуют:

сигналы Y7 - 1, Y8 - О, если Х4 - 1, Х5 О, и тогда по сигналу Ф1 происходит переход в состояние 21;

сигналы Y7 0, и сигналы Y1Y6

со значениями, соответствующими коду состояния 22, если Х4 О, Х5 - О, и тогда по сигналу Ф1 происходит переход в состояние 22;.

сигналы Y7 О, Y8 1 и сигналы Y1 ,...,Y6 со значениями, соответствующимикоду состояния 26, если Х4 О, Х5 1, и тогда по сигналу Ф1 происходит переход в состояние 26.Состояние 21. Удаление из очереди. Коррекция начала.

На выходах ЛМ 13 присутствуют единичные сигналы Д28 и Д20. Это обеспечивает запись по переднему фронту Ф2 содержимого пятого регистра 28 в четвертый регистра 20.

На выходах ЛМ 11 присутствуют сигналы Y7 - 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 22.

Состояние 22. Удаление из очереди. Проверка отображения удаляемой директивы.

На выходах ЛМ 13 отсутствуют единичные сигналы, поэтому в работе устройства никаких изменений не происходит, на выходах ЛМ 11 присутствуют:

сигналы 1, Y8 О, если Х7 1, и тогда по сигналу Ф1 происходит переход в состояние 23;

сигналы Y7 О, Y8 1 и сигналы Y1Y6

со значениями, соответствующими коду состояния 27, если Х7 О, и тогда по сигналу Ф1 происходит переход в состояние 27.

Состояние 23. Удаление из очереди. Коррекция отображаемой директивы.

На выходах ЛМ 13 присутствуют единичные сигналы ДЗО, Д25, Д42 и Д46. Это обеспечивайт запись по переднему фронту Ф2 содержимого первого регистра 3 в десятый регистр 41 и в одиннадцатый регистр 56.

На выходах ЛМ 11 присутствуют сигналы Y7 1, поэтому при поступлении сигнала Ф1 происходит переход в состояние 24.

Состояние 24. Удаление из очереди. Выдача на отображение. Конец удаления.

На выходах ЛМ 13 присутству1бт единичные сигналы Д26 и Д27. Это обеспечивает запись во внутренний регистр устройства 4 для отображения информации содержи-, мого одиннадцатого регистра 56, а также сброс содержимого первого триггера 5.

На выходах ЛМ 11 присутствуют бигналы Y7 - О, Y8 1 и нулевые сигналы Y1Y6,

поэтому по сигналу Ф1 происходит переход в состояние 0.

Состояние 25. Уничтожение очереди.

На выходах ЛМ 13 присутствуют единичные сигналы Д13, Д32, ДЭЗ и Д47. Это обеспечивает обнуление содержимого третьего регистра 17, четвертого регистра 20, десятого регистра 41 и одиннадцатого регистра 56.

На выходах ЛМ 11 присутствуют сигналы Y7 О, V8 1 и сигналы Y1Y6 со

значениями, соответствующими коду состояния 24, поэтому по сигналу Ф1 происходит переход в состояние 24.

Состояние 26. Удаление из очереди, коррекция конца.

. На выходах ЛМ 13 присутствуют единичные сигналы Д29 и Д22. Это обеспечивает запись по переднему фронту Ф2 содержимого шестого регистра 30 в третий регистр 17.

Hs выходах ЛМ 11 присутствуют сигналы Y7 О, Y8 1 и сигналы Y1,....Y6 со значениями, соответствующими коду состояния 22, если Х8 О, и тогда по сигналу Ф1 происходит переход в состояние 22.

Состояние 27. Удаление из очереди. Конец удаления.

На выходах Л М 13 присутствует единичный сигнал Д27. Это обеспечивает сброс содержимого первого триггера 5.

На выходах ЛМ 11 присутствуют сигналы Y7 О, Y8 1 и нулевые сигналы Y1,...,Y6, поэтому по сигналу Ф1 происходит переход в состояние О,

Состояние 28. Листание очереди вперед. Чтение следующей директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Д23, Д7 и Д8. Это обеспечивает запись по переднему фронту Ф2 в пятый регистр 28 содержимого ячейки БОП 27, адресом которой является код директивы, хранимый в десятом регистре 41.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 1, поэтому по сигналу Ф1 происходит переход в состояние 29.

Состояние 29. Листание очереди вперед. Установка следующей директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Д9 и,Д4. Это обеспечивает запись по переднему фронту Ф2 содержимого пятого регистра 28 в первый регистр 3.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 30.

Состояние 30. Листание очереди вперед. Коррекция отображения директивы. На выходах- ЛМ 13 присутствуют еди: ничные сигналы ДЗО, Д42, Д25 и Д46. Это обеспечивает запись по переднему фронту

Ф2 содержимого первого регистра 3 в десятый 41 и в одиннадцатый 56 регистры.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 31.

Состояние 31. Листание очереди вперед. Выдача на отображение. Конец листания.

На выходах ЛМ 13 присутствуют единичные сигналы Д26 и Д34. Это обеспечивает запись во внутренний регистр устройству 4 для отображения информации содержимого одиннадцатого регистра 56, а также сброс содержимого третьего триггера 50.

На выходах Л М Т1 присутствуют сигналы Y7 0, Y8 1 и нулевые сигналы Y1 ,...,Y6, поэтому по сигналу Ф1 происходит переход в состояние 0.

Состояние 32. Листание очереди назад. Чтение предыдущей директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Д23,Д10 и Д11. Это обеспечивает запись по переднему фронту Ф2 в шестой регистр 30 одержимого ячейки БОП 29, адресом которой является код директивы, хранимый в десятом регистре 41.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходи переход в состояние 33.

Состояние 33. Листание очереди назад, коррекция отображаемой директивы.

На выходах ЛМ 13 присутствуют единичные сигналы D35, D42, D25 и D46. Это обеспечивает запись по переднему фронту Ф2 содержимого шестого регистра 30 в де-. сятый 41 и в одиннадцатый 56 регистры.

На выходах ЛМ 11 присутствуют сигналы Y7 1( Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 34.

Состояние 34. Листание очереди назад. Выдача на отображение. Конец листания.

Работа устройства в данном сбстоянии аналогична работе в состоянии 31 стой разницей, что сбрасывается содержимое не третьего, а четвертого триггера 51.

По сигналу Ф1 происходит переход в состояние 0.

Состояние 35. Отображение новой директивы. Коррекция отображаемой директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Д37, Д42, Д25 и Д46. Это обеспечивает запись по переднему фронту Ф2 содержимого девятого регистра 39 в десятый 41 ив одиннадцатый 56 регистры.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 36.

Состояние 36. Отображение новой директивы. Выдача на отображения. Завершение.

Работа устройства в данном состоянии аналогична работе в состояниях 31 и 34 с той разницей, что сбрасывается содержимое пятого триггера 52.

По сигналу Ф1 происходит переход в состояние 0.

Состояние 37. Отображение заголовка. Чтение заголовка отображаемой директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Д51 и Д39. Это обеспечива бт запись по переднему фронту Ф2 в двенадцатый регистр 57 содержимого ячейки ПЗУ 53, адресом которой является код директивы, хранимый в одиннадцатом регистре 56.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 38.

Состояние 38. Отображение заголовка. Коррекция отображаемой директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Д43 и Д46. Это обеспечивает запись по переднему фронту Ф2 в од1/ ннадцатый регистр 56 содержимого двенадцатого регистра 57.

Навыхода ЛМ 11 присутствуют сигналы Y7 1, Y8 0, поэтому по сигналу Ф1 происходит переход в состояние 39.

Состояние 39. Отображение заголовка. Выдача на отображение. Завершение.

Работа устройства в данном состоянии аналогична работе в состоянии 36 с той разницей, что сбрасывается содержимое шее-того триггера 67.

По сигналу Ф1 происходит переход в состояние 0.

Состояние 40. Листание страниц вперед. Чтение последующей директивы.

На выходах ЛМ 13 присутствуют единичные сигналы Дё1 и Д40. Это обеспечивает запись по переднему фронту Ф2 в тринадцатый регистр 58 содержимого ячейки ПЗУ 54, адресом которой является код директивы, хранимый в одиннадцатом регистре 56.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y9 1, поэтому ПС сигналу Ф1 происходит переход в состояние 41.

Состояние 41. Листание страниц вперед. Коррекция отображаемой директивы.

Работа устройства в данном состоянии аналогична работе в состоянии 38 стой разницей, что в одиннадцать1й регистр 56 записывается содержимое тринадцатого регистра 58.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 42.

Состояние 42. Листание страниц вперед. Конец листания.

Работа устройства в данном состоянии аналогична работе в состоянии 39 с той разницей, что сбрасывается содержимое седьмого триггера 68.

0 По сигналу Ф1 происходит переход в состояние 0.

Состояние 43. Листание страниц назад. Чтение предшествующей директивы.

Кй выходах ЛМ 13 присутствуют еди5 ничные сигналы Д51 и Д41. Это обеспечивает запись по переднему фронту Ф2 в четырнадцатый регистр 57 содержимого ячейки ПЗУ 53, адресом которой является код директивы, хранимый в одиннадцатом 0 регистре 56.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 44.

Состояние 44. Листание страниц назад. 5 Коррекция отображаемой директивы.

Работа устройства в данном состоянии

аналогична работе в состоянии 41 с той

разницей, что в одиннадцатый регистр 56

записывается содержимое четырнадцатого

0 регистра 59.

На выходах ЛМ 11 присутствуют сигналы Y7 1, Y8 О, поэтому по сигналу Ф1 происходит переход в состояние 45.

Состояние 45. Листание страниц назад. 5 Выдача на отображение. Конец листания.

Работа устройства в данном состоянии аналогична работе в состоянии 42 с той разницей, что сбрасывается содержимое восьмого триггера 69.

0 По сигналу Ф1 происходит переход в состояние 0.

Формула изобретения Устройство для выдачи сообщений, содержащее первый и второй коммутаторы, 5 первый регистр, обнулящий вход которого соединен с входом Сброс устройства, а выходы подключены к информационным входам первой группы первого коммутатог ра, устройство для отображения информа0 ции, первый триггер, установочный вход которого соединен с управляющим входом устройства, второй триггер, информационный вход которого соединен с отдельным информационным входом устройства, а 5 вход записи - с управляющим входом устройства, первый элемент ИЛИ, первый вход которого соединен с входом Сброс устройства, а второй вход - с управляющим входом устройства, второй и третий злементыИЛМ, первые входы которых соединены с входом

Сброс устройства, тактовый генератор, вход которого соединен с выходом первого элемента ИЛИ, авторой синхровыход - с синхровходом первого регистра, первую логическую матрицу, первый и второй входы первой группы входов которой соединены с соответствующими выходами первого и второго триггеров, первый счетчик, входы данных которого соединены с первым-шестым выходами первой логической матрицы, п эибавляющий вход - с седьмым выходом первой логической матрицы, установочный вход подключен к восьмому выходу первой логической матрицы, синхровход соединен с первым синхровыходом тактового генератора, обнуляющий вход - с входом Сброс устройства, а выходы - с входами второй группы первой логической матрицы, вторую логическую матрицу, входы которой соединены с выходами первого счетчика, четвертый выход с входом записи первого регистра, а пятый, первый, семнадцатый, двадцать третий, восемнадцатый, пятнадцатый, четвертый, двадцать шестой, тридцать первый, тридцать второй выходы подключены соответственно к первым, вторым, третьим и четвертым адресным входам первого коммутатора, первому и второму адресным входам второго .коммутатора, входу записи первого регистра, управляющему входу устройства для отображения информации, вторым входам второго и третьего элементов ИЛИ, четвертый элемент ИЛИ, первый вход которого соединен с входом Сброс устройства, второй вход - с двадцать седьмым выходом второй логической матрицы, а выход - со сбрасывающим входом первого триггера, второй регистр, входы данных которого являются информационными входами устройства, вход записи соединен с управляющим входом устройства, обнуляющий вход подключен к входу Сброс устройства, а выходы соединены с информационными входами второй группы первого коммутатора и с информационнь1ми входами первой группы второго коммутатора, третий коммутатор, информационные входы первой группы которого подключены к выходам второго регистра, а первый и второй адресные входы соединены соответственно с двенадцатым и четырнадцатым выходами второй логической матрицы; третий регистр, синхровход которого соединен с вторым синхровыходом тактового генератора, вход записи подключен к двадцать второму выходу второй логической матрицы, а обнуляющий вход - к выходу третьего элемента ИЛИ, первый компаратор, входы первой группы которого соединены с выходами первого регистра, входь) второй группы - с выходами

третьего регистра, а выход подключен к шестому входу первой группы входов первой логической матрицы, второй компаратор, входы первой группы которого соединены с

выходами второго регистра, входы второй группы - с выходами третьего регистра, а выход подключен к пятому входу первой группы входов первой логической матрицы, четвертый регистр, синхровход которого соединен с вторым синхровыходом тактового генератора, вход записи подключен к двадцатому выходу второй логической матрицы, а обнуляющий вход - к выходу второго элемента ИЛИ, четвертый коммутатор, инфор.мационные входы первой группы которого соединены с выходами четвертого регистра, первый и второй адресные входы соединены соответственно с третьим и девятым выходами второй логической матрицы, а

выходы-с информационными входами первого регистра, пятый коммутатор, информационные входы первой группы которого соединен с выходами второго регистра, первый и второй адресные входы соединены

соответственно с девятнадцатым и двадцать восьмым выходами второй логической матрицы, а выходы - с информационными входами четвертого.регистра, шестой коммутатор, информационные входы первой

группы которого соединены с выходами второго регистра, первый и второй адресные входы - соответственно с двадцать первым и двадцать девятым выходами второй логической матрицы, а выходы - с информационными входами третьего регистра, третий компаратор, входы первой группы которого соединены с выходами первого регистра, входы второй группы - с выходами четвертого регистра, а выход подключен к девятому входу первой группы входов первой логической матрицы, четвертый компаратор, входы первой группы которогосоединены с выходами второго регистра, входы второй группы - с выходами четвертого регистра, а выход подключен к четвертому входу первой группы входов первой логической матрицы, пятый элемент ИЛИ, входы которого соединены с выходами четвертого регистра, а выход подключен к третьему входу

(Первой группы входов первой,логической матрицы, первый блок оперативной памяти, адресные входы которого соединены с выходами первого коммутатбра; входы данных подключены к выходам второго коммутатора, синхроЬход соединен с вторым синхровыходом тактового генератора, а входы чтения и записи - соответственно с седьмым и шестнадцатым выходами второй логической матрицы; пятый регистр, входь данных которого соединены с выходами

первого блока оперативной памяти, синхровход - вторым синхровыходом тактового генератора, о.бнулящий вход подключен к входу Сброс устройства, вход записи соединен с восьмым выходом второй логической матрицы, . а выходы - с информационными входами вторых групп второго, четвертого и пятого коммутаторов, второй блок оперативной памяти, адресные входы которого соединены с выходами первого коммутатора, входы данных подключены к выходам третьего коммутатора, синхровход соединен с вторым синхровыходом тактового генератора, а входы чтения и записи - соответственно с десятым и тринадцатым выходами второй логической матрицы, шестой регистр, входы данных которого соединены с выходами второго блока оперативной памяти, синхровход - с вторым синхровыходом тактового генератора, обну;1ящий вход подключен к входу Сброс устройства, вход записи соединен с одиннадцатым выходом второй логической матрицы, а выходы подключены к информационным входам вторых групп третьего и шестого коммутаторов и к информационным входам третьей группы первого коммутатора, первое постоянное запоминающее устройство (ПЗУ), информационные входы которого соединены с выходами первого коммутатора, седьмой регистр, входы данных которого соединены с выходами первого ПЗУ, синхровход - с вторым синхровыходом тактового генератора, обнулящий вход подключен к входу Сброс устройства, вход записи соединен с вторым выходом второй логической матрицы, вось-, мой регистр, входы данных которого соединены с выходами первого ПЗУ, синхровход - с вторым синхровыходом тактового генератора, обнулящий вход подключен к входу Сброс устройства, а вход записи соединен с шестым выходом второй логической матрицы, пятый компаратор, входы первой и второй групп которого соединены с выходами седьмого и восьмого регистров соответственно, шестой и седьмой элементы ИЛИ. входы которых соединены с выходами седьмого и восьмого регистров соответственно. первый элемент И, первый вход которого соединен с выходом шестого элемента ИЛИ, второй вход - с выходом пятого компаратора, третий вход - с выходом седьмого элемента ИЛИ, а выход подключен к восьмому входу первой группы входов первой логической матрицы, второй элемент И, первый вход которого соединен с управляющим входом устройства, а второй вход - с отдельным информационным входом устройства, девятый регистр, входы данных которого являются информационными входами устройства, вход записи соединен с выходом второго элемента И. а обнулящий вход подключен к входу Сброс устройства, 5 седьмой коммутатор, информационные входы первой - четвертой групп которого соединены с выходами первого, второго, шестого и девятого регистров соответственно, а первый - четвертый адресные входы

0 подключены соответственно к тридцатому, двадцать четвертому, тридцать пятому и тридцать седьмому выходам второй логической матрицы, десятый регистр, входы данных которого соединены с выходами

5 седьмого коммутатора, синхровход - с вторым синхровыходом тактового генератора, вход записи - с двадцать пятым выходом второй логической матрицы, а выходы - с информационными входами четвертой групQ пы первого коммутатора, восьмой элемент ИЛИ, первый вход которого соединен с входом Сброс устройства, второй вход подключен к тридцать третьему выходу второй логической матрицы, а выход

5 соединен с обнуляющим входом десятого регистра, шестой компаратор, входы первой и второй групп которого соединены с выходами второго и десятого регистров соответственно, а выход

0 подключен к седьмому входу первой группы входов первой логической матрицы, первый, второй и третий клавишные элементы, первый, второй и третий однрвибраторы, третий триггер, установочный вход которого

5 через первый одновибратор соединен с выходом первого клавишного элемента, сбрасывающий вход подключен к тридцать четвертому выходу второй логической матрицы, а выход соединен с десятым входом

0 первой группы вхолоп первой логической матрицы, четвёотый триггер, установочный вход которого через второй одновибратор соединен с выходом второго клавишного элемента, сбрасывающий вход подключен к

5 тридцать шестому выходу второй логической матрицы, а выход соединен с одиннадцатым входом первой группы входов первой логической матрицы, пятый триггер, установочный вход которого через третий одно0 вибратор соединен с выходом третьего клавишного элемента, сбрасывающий вход

подключен к тридцать восьмому выходу второй логической матрицы, а выход соединен с двенадцатым входом первой группы входов первой логической матрицы, отличающееся тем, что, с целью расширения функциональных возможностей за счет вве%

дения возможности организации уточняющих директив с последующей выдачей на устройство для отобрлжсния информации

по директивам оператора, дополнительно введены пятьдесят первый вход второй логической матрицы, соединенный с пятым управляющим входом первого коммутатора, второе - четвертое ПЗУ, информационные входы которых соединены с выходами первого коммутатора, одиннадцатый регистр, вход записи которого соединен с сорок ше- стым выходом второй логической матрицы, синхровход .подключен к второму выходу тактового генератора, а выход соединен с устройством для отображения информации/ и с первым коммутатором, двенадцатый четырнадцатый регистры, синхровходы которых соединены с вторым выходом тактового генератора, обнуляющие входы - с входом Сброс устройства, информационные входы подключены соответственно к выходам второго, третьего и четвертого ПЗУ, а входы записи соединены с тридцать девятым - сорок первым выходами второй логической мatpйцы-cboтвeтcтвeннo, восьмой коммутатор, информационные входы первой-четвертой групп которого соединены соответственно с вы-ходами седьмого коммутатора, двенадцатого, тринадцатого и четырнадцатого регистров, первый - четвертый адресные входы подключены к сорок второму - сорок пятому выходам второй логической матрицы соответственно, а выход соединен с информационным бходом одиннадцатого регистра, четвертый - шестой клавишные элементы, четвертый - шестой дновибраторы, шестой триггер, установочный вход которого через четвертый одновибратор соединен с выходом четвертого клавишного элемента, обнулящий вход подключен к сорок восьмому выходу второй логической матрицы, а выход - к тринадцатому входу первой группы входов первой логической матрицы, седьмой триггер, установочный вход которого через пятый одновибратор соединен с выходом пятого клавишного элемента, сбрасывающий вход подключен к сорок де1вятому выходу второй

логической матрицы, а выход соединен с четырнадцатым входом первой группы входов первой логической матрицы, восьмой триггер, установочный вход которого через шестой одновибратор соединен с выходом

шестого клавишного элемента, сбрасывающий вход подключен к пятнадцатому выходу второй логической матрицы, а выход соединен с пятнадцатым вхсдом первой группы входов первой логической матрицы, девять1й элемент ИЛИ, первый вход которого соединен с сорок седьмым выходом второй логической матрицы, второй вход- с входом Сброс устройства, авыход подключен г обнуляющее входу одиннадцатого регистра.

Фае. /

JV fffjKffff A,

V (Л« f

a i fofs/ 9

no tu/e. .2

or 5f) tfo фег. f

or Лели У. кч vf. / fjn eaff- г / ;

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫДАЧИ СООБЩЕНИЙ | 1992 |

|

RU2032936C1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Устройство для формирования кода текущего состояния критической ситуации технического объекта | 1990 |

|

SU1797098A1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2146064C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

Изобретение относится к средствам контроля, управления и сигнализации сложных технических систем, в частности летательных аппаратов, и может быть использовано для повышения качества, надежности и безопасности их функционирования. Целью изобретения является расширение функциональных возможностей устройства за счет организации уточняющих директив с последующей выдачей на устройство для отображения информации по директивам оператора. Поставленная цель достигается тем, что устройство длявыдачи сообщений содержит первый коммутатор, второй коммутатор, первый регистр, устройство для отображения информации, первый триггер, второй триггер, первый, второй, третий элемент ИЛИ, тактовый генератор, первую логическую матрицу, первый счетчик, вторую логическую матрицу, четвертый элементы ИЛИ, второй регистр, третий коммутатор, третий регистр, первый, второй компараторы, четвертый регистр, четвертый, пятый, шестой коммутаторы, третий, четвертый компараторы, пятый элемент ИЛИ, первый блок оперативной памяти, пятый регистр, второй блоКоперативной памяти, шестой регистр, первый блок постоянной памяти, седьмой, восьмой регистры, пятый компаратор, шестой, седьмой элементы ИЛИ, первый, второй элементы И, девятый регистр, седьмой коммутатор, десятый регистр, восьмой элемент ИЛИ, шестой компаратор, первый, второй, третий клавишные элементы, первый, второй, третий одновибраторы, третий триггер, четвертый триггер, пятый триггер, второй, третий, четвертый блоки постоянной памяти, третий, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый регистры, восьмой коммутатор, четвертый, пятый, шестой клавишные элементы, четвертый, пятый, шестой одновибраторы, шестой, седьмой, восьмой триггеры, девятый элемент ИЛИ. 1 П.Ф., 4 ил.слG-VI ОюСА>&;о VI

Фг-Иа «5b«rtL

А1&

Л/

4

-КЮ .л// Л/2

65

. xf 427

6

Фиг. 4

Поступление

Х/

Ш

CSpoc

| Авторское свидетельство СССРпо заявке ^ 4161279, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1989-12-04—Подача