Изобретение относится к области вычислительной техники и может быть использовано для реализации каскадных логических устройств конвейерного типа.

Известен тактируемый логический элемент с функцией И-ИЛИ на КМДП транзисторах (патент РФ №2275737, МКИ Н03К 19/01 от 06.12.2004). В нем используются тактируемый элемент И-ИЛИ-НЕ с предзарядом, выход которого подключен к входу тактируемого в противофазе инвертирующего элемента. Недостатком элемента является избыточное потребление мощности за счет сквозного тока в цепи инвертирующего элемента при восстановлении исходного состояния. Наиболее близким техническим решением к предлагаемому является тактируемый логический элемент И-ИЛИ на КМДП транзисторах (Патент РФ №2368072, от 24.03.2008, МКИ Н03К 19/01 (2006.01). Это устройство, принятое за прототип, содержит содержит логический блок в виде ключевых цепей на транзисторах n-типа, предзарядовые транзисторы p- и n-типов, тактовые транзисторы p- и n-типов и логический транзистор p-типа. Недостаток этого устройства - избыточная потребляемая мощность при переключении элемента в состояние логической 1 вследствие тока, протекающего через открытый предзарядовый транзистор p-типа.

Технической задачей, решаемой в изобретении, является снижение потребляемой мощности.

Поставленная цель достигается тем, что тактируемый логический элемент И-ИЛИ, содержащий предзарядовый транзистор p-типа, тактовые транзисторы n-типа и p-типа, логический транзистор p-типа и логический блок, содержащий ключевые цепи, включенные параллельно между выходом логического блока и тактовой шиной, каждая ключевая цепь состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к логическим входам элемента, тактовый транзистор n-типа, затвор которого подключен к тактовой шине, включен между выходом элемента и шиной земли, затворы логического транзистора p-типа и предзарядового транзистора p-типа подключены соответственно к выходу логического блока и выходу элемента, логический транзистор p-типа включен между выходом элемента и противофазной тактовой шиной, тактовый транзистор p-типа, затвор которого соединен с противофазной тактовой шиной, и предзарядовый транзистор p-типа включены последовательно между шиной питания и выходом логического блока.

Существенными отличительными признаками в указанной совокупности признаков является наличие противофазной тактовой шины с соответствующими новыми связями транзисторов p-типа - логический транзистор p-типа включен между выходом элемента и противофазной тактовой шиной, тактовый транзистор p-типа, затвор которого соединен с противофазной тактовой шиной, и предзарядовый транзистор p-типа включены последовательно между шиной питания и выходом логического блока. Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - уменьшение потребляемой мщности.

В устройстве-прототипе при формировании на выходе элемента сигнала логической 1 (при поступлении нулевого сигнала на тактовую шину) предзарядовый транзистор p-типа открыт, в результате чего через данный транзистор и проводящую ключевую цепь протекает сквозной ток от шины питания на тактовую шину, с чем связано избыточное потребление мощности, не связанное с перезарядом узловых емкостей. При этом возрастает время перезаряда емкости выхода логического блока, что также ведет к избыточному энергопотреблению

В заявленном устройстве в том же процессе переключения цепь питания предзарядового транзистора p-типа прерывается за счет закрывающегося тактового транзистора p-типа по сигналу на противофазной тактовой шине. В результате сквозной ток отсутствует и снижается потребляемая мощность. Благодаря парафазному тактированию потребляемая мощность расходуется только на перезаряд узловых емкостей. При этом устройство содержит на один транзистор меньше, чем устройство-прототип, что также служит уменьшению емкостных нагрузок и в итоге уменьшению потребляемой мощности.

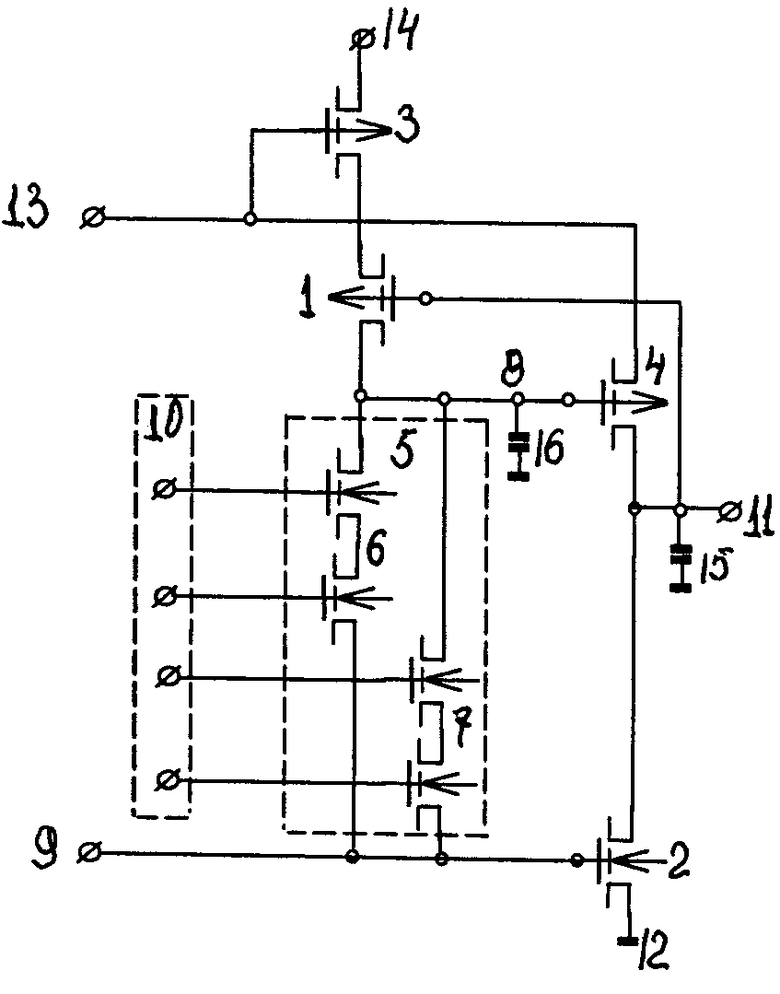

На чертеже приведена принципиальная схема заявленного устройства на примере двух двухвховых элементов И (элемента 2И-2ИЛИ).

Тактируемый логический элемент И-ИЛИ содержит предзарядовый транзистор 1 p-типа, тактовый транзистор 2 n-типа, тактовый транзистор 3 p-типа, логический транзистор 4 p-типа и логический блок 5, содержащий ключевые цепи 6-7, включенные параллельно между выходом 8 логического блока 5 и тактовой шиной 9. Каждая ключевая цепь состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к логическим входам 10 элемента. Тактовый транзистор 2 n-типа, затвор которого подключен к тактовой шине 9, включен между выходом 11 элемента и шиной земли 12, а логический транзистор 4 p-типа, затвор которого соединен с выходом 8 логического блока 5, включен между противофазной тактовой шиной 13 и выходом 11. Тактовый транзистор 3 p-типа, затвор которого соединен с противофазной тактовой шиной 13, и предзарядовый транзистор 1 p-типа, затвор которого соединен с выходом 11 элемента, включены последовательно между шиной питания 14 и выходом 8 логического блока 5.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при положительном сигнале на тактовой шине 9 тактовый транзистор 2 n-типа открыт, логический транзистор 4 p-типа работает в инверсионном режиме (на противофазной тактовой шине 13 нулевой сигнал) и конденсатор 15, представляющий собой узловую нагрузку, разряжается до 0. Ключевые цепи 6 и 7 либо закрыты, либо работают в инверсионном режиме. Тактовый транзистор 3 p-типа открывается и конденсатор 16, являющийся узловой емкостью, через открытый предзарядовый транзистор 1 p-типа заряжается до напряжения пмтания. Логический транзистор 4 p-типа при этом закрывается. На первом полутакте на логических входах 10 устанавливаются сигналы, соответствующие выполняемой функции.

На втором полутакте на тактовую шину 9 поступает нулевой, а на противотактовую шину 13 положительный сигналы. Тактовый транзистор 2 при этом закрывается и подготавливает выход 11 устройства к формированию логического сигнала. При выполняемой функции по И, равной 0, ключевые цепи 6 и 7 не проводят, и состояние выхода выхода 8 логического блока 5 и выхода 11 устройства 11 устройства не изменяется и соответствует исходному - нулевому. Когда на затворы транзисторов n-типа хотя бы одной из ключевых цепей 6-7 поданы сигналы логической 1, что соответствует функции И, равной 1, соответствующая ключевая цепь оказывается в проводящем состоянии и узловая емкость (конденсатор 16) выхода 8 логического блока 5 разряжается до нулевого уровня напряжения на тактовой шине 9. Логический транзистор 4 p-типа при этом открывается и поскольку на противофазной тактовой шине 13 напряжение питания на выходе 11 элемента формируется сигнал логической 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ НА КМДП ТРАНЗИСТОРАХ | 2008 |

|

RU2368072C1 |

| ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2015 |

|

RU2580095C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2007 |

|

RU2334354C1 |

| ТАКТИРУЕМЫЙ МНОГОВХОДОВЫЙ ЭЛЕМЕНТ И | 2009 |

|

RU2412542C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2258303C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| Многовходовый логический элемент И | 2015 |

|

RU2613853C2 |

| МНОГОВХОДОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И НА КМДП ТРАНЗИСТОРАХ | 2006 |

|

RU2319299C1 |

Изобретение относится к области вычислительной техники и может быть использовано для реализации каскадных логических устройств конвейерного типа. Техническим результатом является уменьшение потребляемой мощности. Тактируемый логический элемент И-ИЛИ содержит предзарядовый транзистор 1 p-типа, тактовый транзистор 2 n-типа, тактовый транзистор 3 p-типа, логический транзистор 4 p-типа и логический блок 5, содержащий ключевые цепи 6-7, включенные параллельно между выходом 8 логического блока 5 и тактовой шиной 9. Каждая ключевая цепь состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к логическим входам 10 элемента. 1 ил.

Тактируемый логический элемент И-ИЛИ, содержащий предзарядовый транзистор p-типа, тактовые транзисторы n-типа и p-типа, логический транзистор p-типа и логический блок, содержащий ключевые цепи, включенные параллельно между выходом логического блока и тактовой шиной, каждая ключевая цепь состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к логическим входам элемента, тактовый транзистор n-типа, затвор которого подключен к тактовой шине, включен между выходом элемента и шиной земли, затворы логического транзистора p-типа и предзарядового транзистора p-типа подключены соответственно к выходу логического блока и выходу элемента, отличающийся тем, что логический транзистор p-типа включен между выходом элемента и противофазной тактовой шиной, тактовый транзистор p-типа, затвор которого соединен с противофазной тактовой шиной, и предзарядовый транзистор p-типа включены последовательно между шиной питания и выходом логического блока.

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ НА КМДП ТРАНЗИСТОРАХ | 2008 |

|

RU2368072C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

Авторы

Даты

2014-05-20—Публикация

2012-10-15—Подача