Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации.

Известен преобразователь кода (см. А.С. СССР №1495998 от 14.12.87, МКИ Н 03 М 5/12, "Преобразователь кода", А.А.Гаришин, опубл. 23.07.89, Бюл. №27), содержащий первый элемент задержки, вход которого является входом преобразователя, а первый выход соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является первым выходом преобразователя, инверсный выход триггера соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Прямой выход триггера является вторым выходом преобразователя. Выход элемента РАВНОЗНАЧНОСТЬ соединен непосредственно с первым входом элемента И, через второй элемент задержки с вторым входом элемента И, выход которого соединен с входом синхронизации триггера, информационный вход которого объединен с первым входом элемента РАВНОЗНАЧНОСТЬ и с входом первого элемента задержки, второй выход которого соединен с вторым входом элемента РАВНОЗНАЧНОСТЬ.

Недостатком известного преобразователя кода является сложность схемы, обусловленная наличием большого количества соединений между элементами.

Наиболее близким по совокупности существенных признаков к заявляемому изобретению является преобразователь кода (см. книгу: Микропроцессорные структуры. Инженерные решения: Справочник / Шевкопляс Б.В. - М.: Радио и связь, 1990, с.99, рис.3.10а), содержащий формирователь импульсов, вход которого соединен с информационным входом преобразователя кода и с информационным входом D-триггера, выход которого соединен с информационным выходом преобразователя кода, тактовый вход - с выходом счетного триггера. Инверсный выход счетного триггера является тактовым выходом преобразователя кода. Первый и второй выходы формирователя импульсов соединены, соответственно, с тактовым входом и инверсным S-входом счетного триггера.

Недостатками известного преобразователя кода являются:

- необходимость формирования признака начала информационной посылки, обеспечивающего взаимную синхронизацию приемника и передатчика и достоверную передачу сообщений вследствие использования фазоманипулированного кода в качестве входного кода преобразователя;

- отсутствие возможности формирования на выходе преобразователя кода сигнала стробирования слова вследствие отсутствия в преобразователе кода функции выдачи сигнала стробирования слова при наличии полезной информации на входе преобразователя.

Задачей, на решение которой направлено заявляемое изобретение, является создание преобразователя кода, обладающего расширенными функциональными возможностями, а именно: преобразование входной самосинхронизирующейся последовательности импульсов, не требующей дополнительного формирования признака начала информационной посылки, формирование преобразователем кода сигнала стробирования слова.

Технический результат, заключающийся в расширении функциональных возможностей, достигается тем, что в преобразователь кода, содержащий информационный вход, D-триггер, выход которого является информационным выходом устройства, и тактовый выход, введены первый и второй счетчики, тактовые входы которых объединены и являются тактовым входом устройства, элемент задержки, выход которого соединен с R-входом первого счетчика и является тактовым выходом устройства, инвертор, вход которого соединен с информационный входом устройства и R-входом второго счетчика, а выход инвертора соединен с входом элемента задержки и тактовым входом D-триггера, информационный вход которого соединен с выходом первого счетчика, выход второго счетчика соединен с управляющим входом второго счетчика и является выходом стробирования устройства.

Указанная совокупность признаков позволяет расширить функциональные возможности преобразователя кода, а именно:

- обеспечить преобразование входной самосинхронизирующейся последовательности импульсов, не требующей дополнительного формирования признака начала информационной посылки, за счет использования широтно-манипулированного кода, формируемого путем манипуляции шириной импульсов внутри постоянных битовых интервалов, в качестве входного кода преобразователя;

- обеспечить формирование на выходе преобразователя кода сигнала стробирования слова за счет определения наличия полезной информации на входе преобразователя и последующей выдачи сигнала стробирования слова.

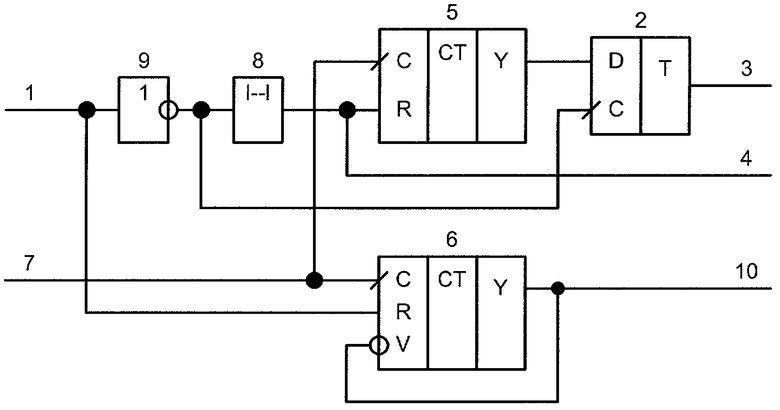

На чертеже приведена принципиальная электрическая схема преобразователя кода.

Преобразователь кода содержит информационный вход 1, D-триггер 2, информационный выход 3, тактовый выход 4, первый 5 и второй 6 счетчики, тактовый вход 7, элемент 8 задержки, инвертор 9 и выход 10 стробирования. Выход D-триггера 2 является информационным выходом 3 устройства. Тактовые входы первого 5 и второго 6 счетчиков объединены и являются тактовым входом 7 устройства. Выход элемента 8 задержки соединен с R-входом первого счетчика 5 и является тактовым выходом 4 устройства. Вход инвертора 9 соединен с информационный входом 1 устройства и R-входом второго счетчика 6, а выход инвертора 9 соединен с входом элемента 8 задержки и тактовым входом D-триггера 2, информационный вход которого соединен с выходом первого счетчика 5. Выход второго счетчика 6 соединен с управляющим входом второго счетчика 6 и является выходом 10 стробирования устройства.

Преобразователь кода работает следующим образом.

В исходном состоянии (см. фиг.) на информационном входе 1, информационном выходе 3, тактовом выходе 4, тактовом входе 7, на выходе 10 стробирования присутствует уровень логического "0". D-триггер 2, счетчики 5 и 6 находятся в состоянии логического "0".

На тактовый вход 7 поступают тактовые импульсы. По фронту четвертого импульса, поступающего на тактовый вход 7, на выходе счетчика 6 и, соответственно, на выходе 10 стробирования устанавливается уровень логической "1", который поступает на управляющий вход счетчика 6, блокируя его дальнейшее переключение. Преобразователь готов к преобразованию широтно-манипулированного кода в бинарный код.

На информационный вход 1 поступает информация в широтно-манипулированном коде, причем на один битовый интервал приходится четыре импульса на тактовом входе 7. По приходу первого бита информационной посылки на информационном входе 1 устанавливается уровень логической "1", который поступает на R-вход счетчика 6, устанавливая его в нулевое состояние. На выходе счетчика 6 и, соответственно, на выходе 10 стробирования устанавливается уровень логического "0", который поступает на вход управления счетчика 6 и снимает запрещающий переключение потенциал. На выходе инвертора 9 устанавливается уровень логического "0", который через элемент 8 задержки поступает на тактовый выход 4 и на R-вход счетчика 5, снимая удерживающий в нулевом состоянии потенциал и разрешая его переключение. По фронтам импульсов, поступающих на тактовый вход 7, происходит переключение счетчика 5. Если текущий преобразуемый бит информационной посылки соответствует логической "1", то до прихода отрицательного перепада преобразуемого бита информационной посылки на выходе счетчика 5 устанавливается уровень логической "1". По приходу отрицательного перепада преобразуемого бита информационной посылки на выходе инвертора 9 формируется положительный перепад, который поступает на тактовый вход D-триггера 2, на выходе которого устанавливается логический уровень выхода счетчика 5. Уровень логической "1" с выхода инвертора 9 через элемент 8 задержки поступает на тактовый выход 4 и на R-вход счетчика 5, устанавливая его в нулевое состояние. После прихода отрицательного перепада преобразуемого бита информационной посылки по фронтам импульсов, поступающих на тактовый вход 7, до прихода следующего бита информационной посылки происходит переключение счетчика 6, но логический уровень выхода счетчика 6 и, соответственно, выхода 10 стробирования не изменяется. Преобразование последующих битов информационной посылки осуществляется аналогично.

После прихода отрицательного перепада последнего бита информационной посылки по фронтам импульсов, поступающих на тактовый вход 7, происходит переключение счетчика 6. По фронту четвертого импульса, поступающего на тактовый вход 7, на выходе счетчика 6 и, соответственно, на выходе 10 стробирования устанавливается уровень логической "1", который поступает на управляющий вход счетчика 6, блокируя его дальнейшее переключение.

Для преобразования следующей информационной посылки необходимо подать информацию в широтно-манипулированном коде на информационный вход 1.

Изготовлен лабораторный макет преобразователя кода, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2002 |

|

RU2249911C2 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2259010C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИИМПУЛЬСНОГО КОДА В БИНАРНЫЙ КОД | 2004 |

|

RU2258305C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2002 |

|

RU2253944C2 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2259009C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ШИРОТНО-МАНИПУЛИРОВАННЫЙ КОД | 2003 |

|

RU2250562C2 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2003 |

|

RU2260907C2 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2262191C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2258304C1 |

Изобретение относится к вычислительной технике. Техническим результатом является расширение функциональных возможностей. Устройство содержит D-триггер, первый и второй счетчики, элемент задержки, инвертор. 1 ил.

Преобразователь широтно-манипулированного кода в бинарный код, содержащий информационный вход, D-триггер, выход которого является информационным выходом устройства, и тактовый выход, отличающийся тем, что введены первый и второй счетчики, тактовые входы которых объединены и являются тактовым входом устройства, элемент задержки, выход которого соединен с R-входом первого счетчика и является тактовым выходом устройства, инвертор, вход которого соединен с информационный входом устройства и R-входом второго счетчика, а выход инвертора соединен с входом элемента задержки и тактовым входом D-триггера, информационный вход которого соединен с выходом первого счетчика, выход второго счетчика соединен с управляющим входом второго счетчика и является выходом стробирования устройства.

| ШЕВКОПЛЯС Б.В | |||

| Микропроцессорные структуры | |||

| Инженерные решения | |||

| Справочник | |||

| - М.: Радио и связь, 1990, с.99, рис.3.10а | |||

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 1999 |

|

RU2163418C1 |

| Преобразователь биимпульсного кода в бинарный | 1989 |

|

SU1626384A1 |

| Преобразователь кода | 1987 |

|

SU1495998A1 |

| US 4884074 A, 28.11.1989 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

2006-04-20—Публикация

2004-06-15—Подача