Изобретение относится к области цифровой вычислительной техники и автоматики. Известен счетчик импульсов (далее - объект), построенный на основе триггеров со счетным входом (См. И.Н.Букреев, Б.М.Мансуров и В.И.Горячев. Микроэлектронные схемы цифровых устройств. "Сов. Радио", 1973, стр.137, рис.5.1) Недостатком этого объекта являются счетный триггер, который включает в себя элементы временной задержки счетных импульсов, что снижает быстродействие его работы, усложняет технологию изготовления триггера и повышает требования к формированию параметров счетных импульсов (крутизна фронта, длительность и другие параметры). Известен также объект, выполненный на основе только трех логических элементов (ЛЭ) И, ИЛИ, НЕ, который устраняет недостатки приведенного выше устройства (см. там же, стр.135-150, рис.5.7). В названном объекте триггеры собраны на основе элементов И-НЕ, ИЛИ-НЕ. Каждый разряд объекта содержит основной и вспомогательный регистры на основе RS-триггеров, логические элементы И, ИЛИ, НЕ и шину счетных импульсов, подключенную к первым входам первого и второго элементов И самого младшего разряда объекта. Его недостатками являются относительно низкое быстродействие, определяемое суммарным временем распространения максимального сквозного переноса и переключением двух RS-триггеров, значительным объемом оборудования, определяемым суммарным числом входов логических элементов (Цена Квайна), сравнительно высоким потреблением электроэнергии и выполнением только одной операции счета импульсов. Наиболее близким, принятым за прототип является объект, приведенный в книге А.Г.Шигина, Цифровые вычислительные машины, М., "Энергия", 1971 г., стр.255, рис. 10-9. Указанный объект превосходит по быстродействию другие аналоги, т.к. в нем формирование переноса осуществляется до прихода счетного импульса. Его недостатком является сравнительный большой состав оборудования (два RS-триггера). И минимальный перечень выполняемых операций (счет импульсов). Это сужает область применения счетчика. Целью изобретения является упрощение устройства, расширение перечня выполняемых операций и повышение быстродействия вычислении. Для этого предложен объект, выполненный на логических элементах И, ИЛИ, НЕ, отличающийся тем, что каждый разряд устройства содержит один RS-триггер, пять элементов И, два элемента ИЛИ, три элемента НЕ, первую и вторую шины управления и информационную шину, при этом первая и вторая шины подключены к первым входам первого и второго элементов И, третья шина соединена с первым входом первого элемента ИЛИ, его выход подключен к вторым входам первого и второго элементов И, выходы этих элементов через первый и второй элементы НЕ соединены с R- и S-входами триггера, единичный выход триггера подключен к первому входу второго элемента ИЛИ, второй вход этого элемента связан с выходом первого элемента И, выход второго элемента ИЛИ связан с первым входом третьего элемента И, второй вход которого соединен с выходом второго элемента НЕ, выход третьего элемента И связан с вторым входом четвертого элемента И, третьим входом первого элемента И и входом третьего элемента НЕ, его выход подключен к третьему входу второго элемента И и к первому входу пятого элемента И, вторые входы четвертого и пятого элементов И соединены с выходами четвертого и пятого элементов И младшего разряда соответственно и с вторым и третьим входами первого элемента ИЛИ i-того разряда, кроме того в первый (самый младший) разряд введены четвертая и пятая шины, соединенные с вторыми входами четвертого и пятого элементов И и с вторыми входами четвертого и пятого элементов И и с вторым и третьим входами первого элемента ИЛИ соответственно, а также введена шестая шина, подключенная в каждом разряде к третьему входу второго элемента ИЛИ. Отметим основные отличительные признаки объекта и покажем, что обеспечивает каждый признак:

1. Последовательное включение четвертых и пятых элементов И каждого разряда обеспечивает формирование потенциалов переноса при выполнении операций счета и вычитания импульсов.

2. Управление с выхода первого элемента И через второй элемент ИЛИ первым входом третьего элемента И обеспечивает задержку переключения третьего элемента НЕ при установке триггера в "нуль", а управление с выхода второго элемента НЕ вторым входом третьего элемента И обеспечивает задержку переключения третьего элемента НЕ при установке триггера в "единицу", что позволяет исключить из каждого разряда объекта второй триггер.

3. Подключение информационной шины к первому входу первого элемента ИЛИ обеспечивает прием кода в объект и выполнение операции сложения по модулю два, логического сложения и логического умножения;

4. Подключение первой шины к первому входу первого элемента И обеспечивает выполнение операции логического умножения.

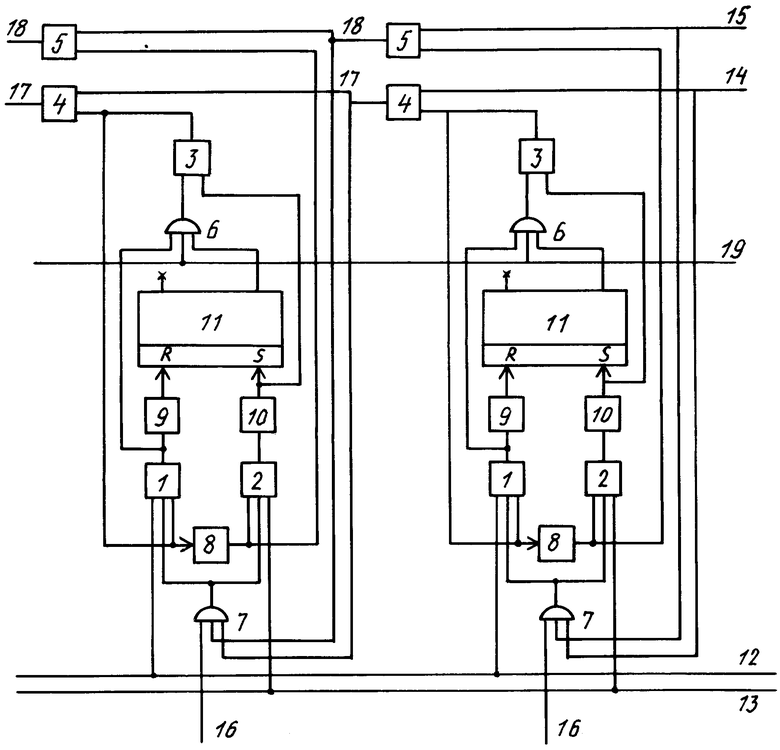

5. Подключение второй шины управления к первому входу второго элемента И обеспечивает выполнение операции логического сложения. В целом предлагаемый объект позволяет построить его каждый разряд на основе одного RS-триггера, пяти элементов И, двух элементов ИЛИ и трех элементов НЕ, при этом выполняется шесть операций (сложение импульсов, вычитание импульсов, прием кода, сложение по модулю два, логическое сложение и логическое умножение). Отметим еще одну важную характеристику, присущую предлагаемому объекту, такую как суммарное число входов логических элементов, на основе которых построен каждый разряд, равное 28, это означает, что для выполнения одной операции в среднем требуется около четырех входов, что значительно меньше, чем в прототипе и в известных объектах. Предлагаемый объект также обеспечивает повышение быстродействия вычислительной системы за счет исключения необходимых пересылок информации в другие устройства и блоки для выполнения тех операций, которые не выполняются прототипом. Для пояснения работы на чертеже приведены первый и второй разряды объекта. На чертеже применяется следующее обозначения: логические элементы И 1-5, элементы ИЛИ 6, 7, элементы НЕ 8-10, RS-триггер 11, первая шина счетных импульсов 12, вторая шина счетных импульсов 13, шина управления сложением 14, шина управления вычитанием 15, информационная шина 16, вход переноса при сложении 17, вход переноса при вычитании 18, шина логического умножения 19.

Предлагаемый объект осуществляется следующим образом. В каждом разряде информационная шина 16 соединена с первым входам ИЛИ 7, его выход по цепи И 1, НЕ 9 соединен с R-входом триггера 11, а по цепи И 2, НЕ11 выход ИЛИ 7 связан с S-выходом триггера 11. Выход ИЛИ 6 соединен с входом И З, второй вход этого элемента соединен с выходом НЕ 10. Выход И З связан с входами И 4, И 1 и НЕ 8. Вторые входы ИЛИ 7, И 4 i-того разряда связаны с выходом И 4 i-1-го разряда. Выход НЕ 8 соединен с входами И 2, И 5. Второй вход И 5 соединен с входом ИЛИ 7 i-того разряда и с выходом И 5 i-1-го разряда. Шины 12 и 13 подключены к входам И 1, 2 соответственно. Шина 14 связана с входом И 4, ИЛИ 7 первого разряда. Шина 15 связана с входами И 5, ИЛИ 7 первого разряда. Шина 19 соединена с входом ИЛИ 6. В статике с выходов элементов НЕ 8-10 поступают высокие потенциалы. На шинах 12-16, 19 отсутствуют высокие потенциалы, на "единичном" выходе триггеров 11 также отсутствуют высокие потенциалы.

Рассмотрим работу объекта при выполнении всех операций.

Операция счета импульсов: операция выполняется за два временных такта (Под тактом понимается длительность счетного импульса или паузы между импульсами, полагая, что они равны между собой). По первому такту на шину 14 подается потенциал операции и распространяется возможный, максимальный по времени перенос, который проходит последовательно через разряды, хранящие код "единицы". Потенциал переноса по цепи И 4 i-того разряда поступит на входы И 1, 2 i+1-го разряда. По второму временному такту, на шины 12 и 13 одновременно поступает счетный импульс, который проинвертирует триггеры, хранящие код последовательных единиц и еще один триггер, который хранил код нуля. Операция счета импульсов будет продолжатся до тех пор, пока на шине 12, 13 поступают счетные импульсы.

Операция вычитания импульсов. Эта операция выполняется аналогично операции сложения. Отличие состоит в том, что потенциал операции поступает по шине 15. Распространяется перенос через элементы И 5, ИЛИ 7.

Операция сложения по модулю два. Выполняется за один временной такт. Код первого слагаемого хранится в триггере 11, код второго слагаемого поступает по цепи шина 16, ИЛИ 7, входы И 1, 2. Одновременно по шинам 12 и 13 поступают исполнительные импульсы, которые по цепи И 2, НЕ 10 или по цепи И 1, НЕ 9 поступают на единичный или на нулевой входы триггера 11. На этом операция завершается.

Операция логического сложения. Выполняется за один такт. Код второго слагаемого поступает по шине 16. Одновременно на шину 13 поступает исполнительный импульс, который по цепи И 2, НЕ 10 поступает на единичный вход триггера11. Операция выполнена.

Операция логического умножения. Выполняется за один временной такт. Инверсивное значение кода второго сложения поступает по шине 16. Одновременно на шины 19 и 12 поступают исполнительные импульсы, которые по цепи И 1, НЕ 9 поступают на нулевой вход триггера и установят его в нуль, если на шине 16 присутствует высокий потенциал, соответствующий коду нуля второго сомножителя в i-том разряде. Операция завершена.

Операция прием кода. Выполняется за два временных такта. По первому такту триггер 11 устанавливается в нуль. По второму такту по шине 13 поступает исполнительный импульс. Если по шине 16 приходит высокий потенциал, соответствующий коду единице, то сигнал по цепи ИЛИ 7, И 2, НЕ 10 поступает на единичный вход триггера и устанавливает его в единицу. Операция завершена.

Таким образом, предлагаемый объект позволяет расширить перечень выполняемых операций по сравнению с прототипом в 6 раз при минимальных затратах оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧИК ИМПУЛЬСОВ | 2005 |

|

RU2284654C2 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2004 |

|

RU2284653C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2264646C2 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2006 |

|

RU2308801C1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| СЧЕТЧИК ИМПУЛЬСОВ (СИ) | 2015 |

|

RU2579524C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

Изобретение может быть использовано в цифровой вычислительной технике и в устройствах автоматики. Технический результат - расширение фунциональных возможностей при минимальных затратах оборудования и повышение быстродействия вычислений. Счетчик выполняет операции счета и вычитания импульсов, инвертирования кода, сложения по модулю два, логического сложения, логического умножения и параллельного приема кода в триггеры. Каждый разряд счетчика содержит один RS-триггер, пять элементов И, два элемента ИЛИ, три элемента НЕ, пять шин управления и информационную шину. Особенностью счетчика является формирование потенциала переноса до прихода счетного импульса и построение каждого разряда только на основе одного RS-триггера. Суммарное число входов логических элементов одного разряда равно 28, в среднем на одну выполняемую операцию требуется около четырех входов (цена Квайна). 1 з.п. ф-пы, 1 ил.

| ШИГИН А.Г., Цифровые вычислительные машины, Москва, Энергия, 1971, стр.255, рис.10-9 | |||

| РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1992 |

|

RU2047272C1 |

| Реверсивный счетчик | 1986 |

|

SU1338068A1 |

| Устройство для счета импульсов | 1985 |

|

SU1275760A1 |

| Реверсивный формирователь двоичного кода | 1984 |

|

SU1257844A1 |

| Реверсивное счетное устройство | 1990 |

|

SU1818689A1 |

| Реверсивный формирователь двоичного кода | 1987 |

|

SU1480123A2 |

Авторы

Даты

2006-04-10—Публикация

2004-12-10—Подача