Заявляемое изобретение относится к области вычислительной техники и может быть использовано в системах связи и обработки информации, функционирующих в системе остаточных классов.

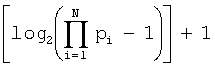

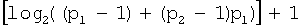

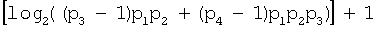

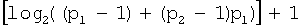

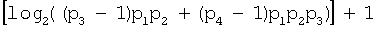

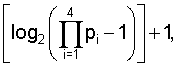

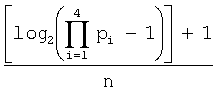

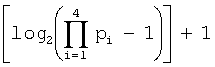

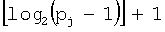

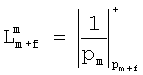

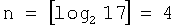

Известны преобразователи чисел из системы остаточных классов (СОК) в позиционную двоичную систему счисления на основе промежуточного перехода через полиадический код (Модулярные параллельные вычислительные структуры нейропроцессорных систем /Н.И.Червяков, П.А.Сахнюк, А.В.Шапошников, С.А.Ряднов; Под ред. Н.И.Червякова. - М.: ФИЗМАТЛИТ, 2003. - 288 с.), (Патент США №4281391), (Патент США №5008668), использования ортогональных базисов (Модулярные параллельные вычислительные структуры нейропроцессорных систем /Н.И.Червяков, П.А.Сахнюк, А.В.Шапошников, С.А.Ряднов; Под ред. Н.И.Червякова. - М.: ФИЗМАТЛИТ, 2003. - 288 с.), позиционных характеристик числа в классах вычетов (Модулярные параллельные вычислительные структуры нейропроцессорных систем /Н.И.Червяков, П.А.Сахнюк, А.В.Шапошников, С.А.Ряднов; Под ред. Н.И.Червякова. - М.: ФИЗМАТЛИТ, 2003. - 288 с.), (А.С. СССР №1267625). Недостатком известных схемных решений являются большие аппаратурные затраты, вследствие использования сумматора разрядности  (во всех трех типах устройства), где [·] - оператор извлечения целой части числа, (N-1) умножителей (при использовании полиадической системы счисления) разрядности

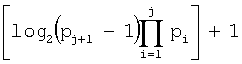

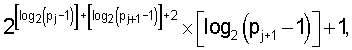

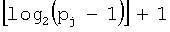

(во всех трех типах устройства), где [·] - оператор извлечения целой части числа, (N-1) умножителей (при использовании полиадической системы счисления) разрядности  , j=1÷N-1, которые необходимы для вычисления за один такт работы устройства всех цифр числа. Вычисление за один такт работы устройства всех цифр числа лежит в основе функционирования обозначенных аналогов.

, j=1÷N-1, которые необходимы для вычисления за один такт работы устройства всех цифр числа. Вычисление за один такт работы устройства всех цифр числа лежит в основе функционирования обозначенных аналогов.

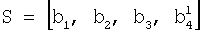

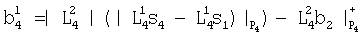

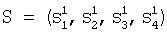

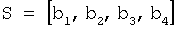

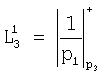

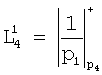

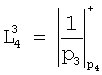

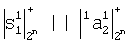

Наиболее близким аналогом, принятым за прототип, является устройство (Патент США № 5008668), содержащее пять постоянных запоминающих устройств (ПЗУ) организации  j=1÷4, для преобразования числа из системы остаточных классов S=(s1,s 2, s3, s4) в полиадическую систему счисления

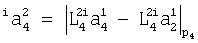

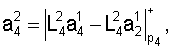

j=1÷4, для преобразования числа из системы остаточных классов S=(s1,s 2, s3, s4) в полиадическую систему счисления  , где

, где  ,

, ,

,  , ПЗУ с организацией

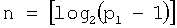

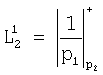

, ПЗУ с организацией  для вычисления суммы B1=b1+b2p1, ПЗУ с организацией

для вычисления суммы B1=b1+b2p1, ПЗУ с организацией  для вычисления суммы

для вычисления суммы  , сумматор для вычисления S=B1+B2, где

, сумматор для вычисления S=B1+B2, где  , десять

, десять  - разрядных регистров-«защелок», два

- разрядных регистров-«защелок», два  - разрядных регистра-«защелки», один

- разрядных регистра-«защелки», один  - разрядный регистр-«защелка».

- разрядный регистр-«защелка».

Основными недостатками прототипа являются большие аппаратурные затраты вследствие использования позиционного сумматора, рассчитанного на сложение операндов разрядности  и

и  , двух ПЗУ увеличенной емкости для вычисления операндов В1 и В2, неоднородности структуры (в схемном решении присутствуют табличные вычислители различной емкости, регистры, комбинационный сумматор).

, двух ПЗУ увеличенной емкости для вычисления операндов В1 и В2, неоднородности структуры (в схемном решении присутствуют табличные вычислители различной емкости, регистры, комбинационный сумматор).

Основной задачей, на которую направлено изобретение, является снижение аппаратурных затрат преобразователя чисел из системы остаточных классов в позиционную двоичную систему счисления.

Техническим результатом, достигаемым при осуществлении изобретения, являются снижение аппаратурных затрат вследствие сокращения общего объема ПЗУ, отсутствие сумматора разрядности  структуры (в устройстве присутствуют табличные вычислители и регистры).

структуры (в устройстве присутствуют табличные вычислители и регистры).

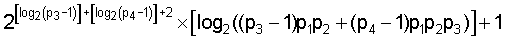

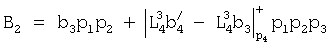

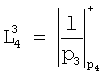

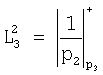

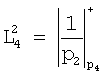

Указанный технический результат достигается тем, что добавлены четыре ПЗУ для операций взвешенного вычитания по каждому основанию, адресные входы которых связаны с выходами входных регистров и добавленного выходного регистра устройства, причем выходы подключены к добавленным четырем регистрам, данные с которых поступают на входные регистры, емкость двух ПЗУ сокращены за счет хранения редуцированных по модулю 2n данных, выходы которых соединены с ПЗУ организации 22n×n. Согласно изобретению ПЗУ, предназначенное для вычисления В1, и выходной сумматор заменяются на два 22n×n ПЗУ, а ПЗУ, предназначенное для вычисления B2, заменяется на ПЗУ организации  , где

, где  , для вычисления

, для вычисления  ,

,  ,

,  , а также добавляются четыре ПЗУ с организацией

, а также добавляются четыре ПЗУ с организацией  для вычисления

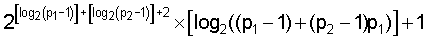

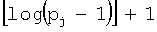

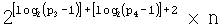

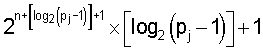

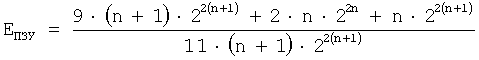

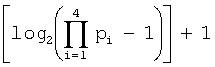

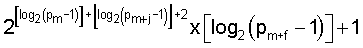

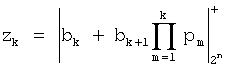

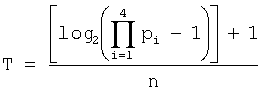

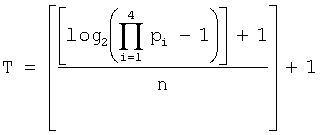

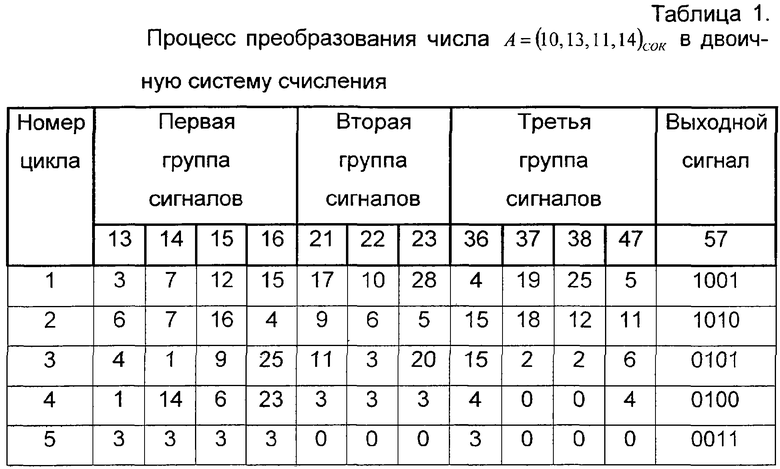

для вычисления  , j=1÷4, где i - номер цикла преобразования, а число 2n является взаимно простым с основаниями системы остаточных классов. Получаемая экономия аппаратурных затрат представлена на фиг.1 в виде зависимости отношения объема памяти заявляемого устройства к объему памяти прототипа от разрядности оснований (при основаниях равной разрядности) без учета затрат на выходной сумматор аналога:

, j=1÷4, где i - номер цикла преобразования, а число 2n является взаимно простым с основаниями системы остаточных классов. Получаемая экономия аппаратурных затрат представлена на фиг.1 в виде зависимости отношения объема памяти заявляемого устройства к объему памяти прототипа от разрядности оснований (при основаниях равной разрядности) без учета затрат на выходной сумматор аналога:

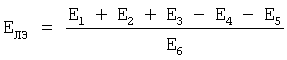

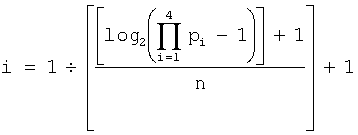

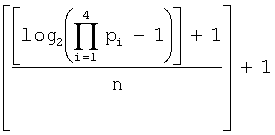

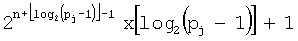

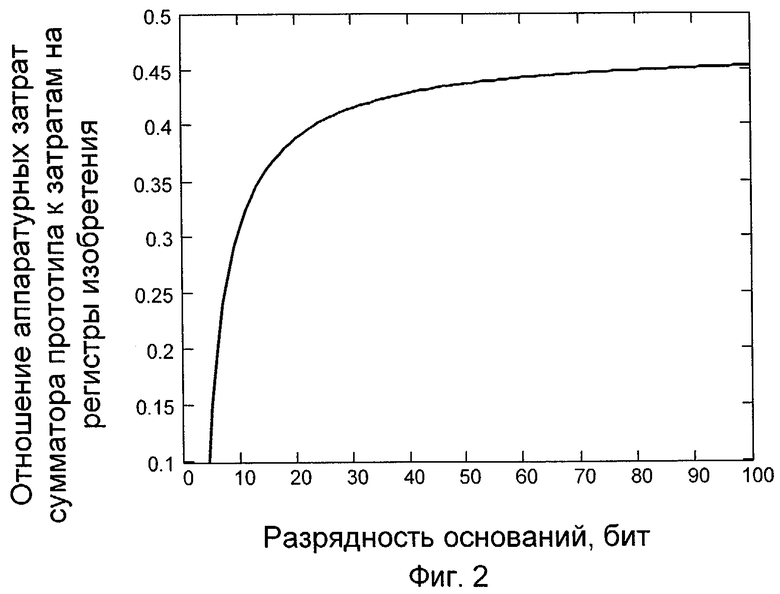

. На фиг.2 представлена зависимость отношения аппаратурных затрат (логических элементов) на дополнительные регистры заявляемого устройства к затратам на комбинационный сумматор прототипа от разрядности оснований (с учетом того, что на один D-триггер затрачивается десять логических элементов, а на один комбинационный одноразрядный сумматор на три входа затрачивается восемь логических элементов):

. На фиг.2 представлена зависимость отношения аппаратурных затрат (логических элементов) на дополнительные регистры заявляемого устройства к затратам на комбинационный сумматор прототипа от разрядности оснований (с учетом того, что на один D-триггер затрачивается десять логических элементов, а на один комбинационный одноразрядный сумматор на три входа затрачивается восемь логических элементов):  , где Е1=4·10·n, E2=10·n+n, Е3=4·10·(n+1)+4·(n+1) - затраты на дополнительные регистры заявляемого устройства, Е4=4·10·(n+1), Е5=4·10·(n+1) - затраты на регистры прототипа повышенной разрядности, Е6=4·8·(n+1) - затраты на комбинационный сумматор прототипа. Преобразование основано на переводе числа из системы остаточных классов

, где Е1=4·10·n, E2=10·n+n, Е3=4·10·(n+1)+4·(n+1) - затраты на дополнительные регистры заявляемого устройства, Е4=4·10·(n+1), Е5=4·10·(n+1) - затраты на регистры прототипа повышенной разрядности, Е6=4·8·(n+1) - затраты на комбинационный сумматор прототипа. Преобразование основано на переводе числа из системы остаточных классов  в полиадическую систему счисления

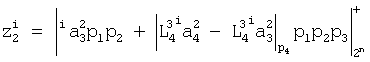

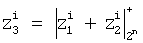

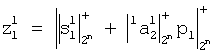

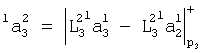

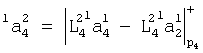

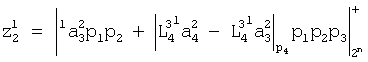

в полиадическую систему счисления  с последовательным вычислением цифр позиционного двоичного представления числа S (Ноден П., Ките К. Алгебраическая алгоритмика (с упражнениями и решениями): Пер. с франц. - М.: Мир, 1999. - 720 с.): на первом шаге i-го цикла вычисляются

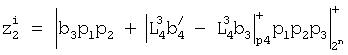

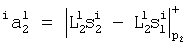

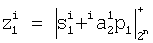

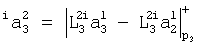

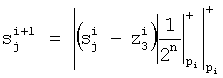

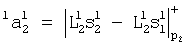

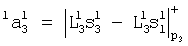

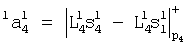

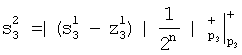

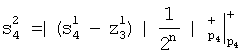

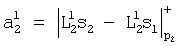

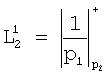

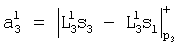

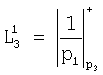

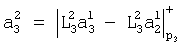

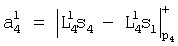

с последовательным вычислением цифр позиционного двоичного представления числа S (Ноден П., Ките К. Алгебраическая алгоритмика (с упражнениями и решениями): Пер. с франц. - М.: Мир, 1999. - 720 с.): на первом шаге i-го цикла вычисляются  ,

,  ,

,  , где

, где  ,

,  ,

,  ; на втором шаге i-го цикла вычисляются

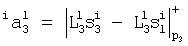

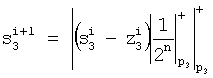

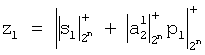

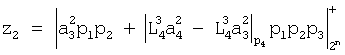

; на втором шаге i-го цикла вычисляются  ,

,  ,

,  , где

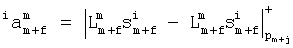

, где  ,

,  ; на третьем шаге i-го цикла вычисляется

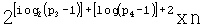

; на третьем шаге i-го цикла вычисляется  , где

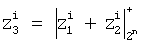

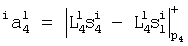

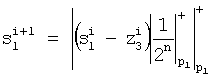

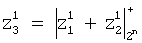

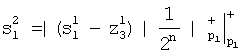

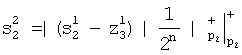

, где  ; на четвертом шаге i-го цикла вычисляются i-ые n разрядов искомого двоичного представления числа

; на четвертом шаге i-го цикла вычисляются i-ые n разрядов искомого двоичного представления числа  ; на пятом шаге i-го цикла вычисляются

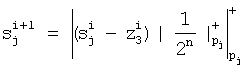

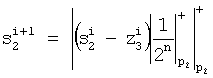

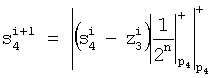

; на пятом шаге i-го цикла вычисляются  ,

,  ,

,  ,

,  ; номер цикла

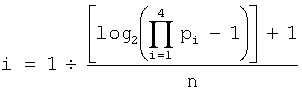

; номер цикла  , если

, если  кратно n (на

кратно n (на  цикле пятый шаг отсутствует), и

цикле пятый шаг отсутствует), и  , если

, если  не кратно n (на

не кратно n (на  цикле пятый шаг отсутствует).

цикле пятый шаг отсутствует).

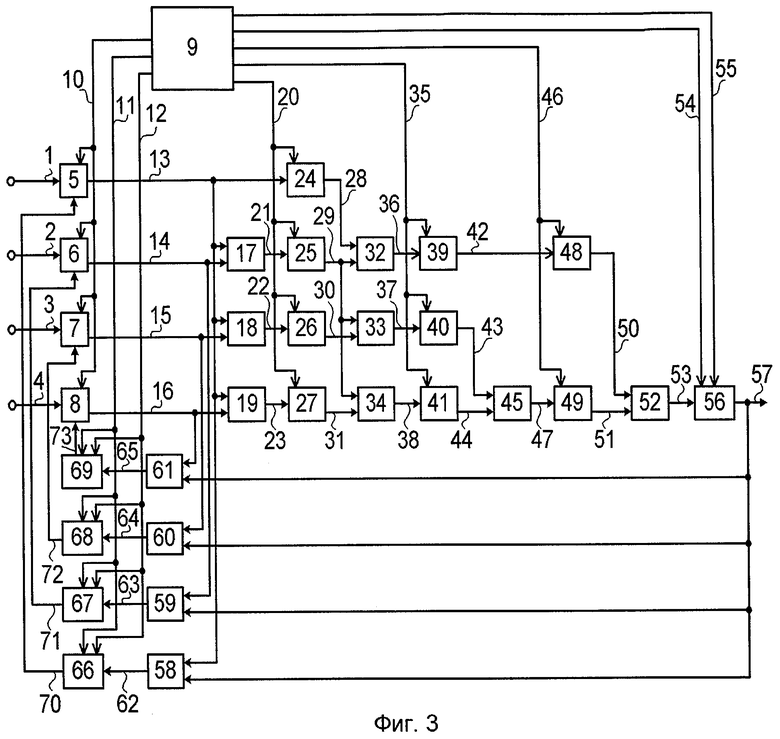

На фиг.3 представлена блок-схема заявляемого устройства для преобразования чисел из системы остаточных классов в позиционную двоичную систему счисления.

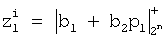

Устройство содержит  - разрядные регистры-«защелки» 5, 6, 7, 8 для j=1-4, соответственно, 25, 26, 27 для j=2-4, соответственно, 40, 41 для j=3, j=4, соответственно;

- разрядные регистры-«защелки» 5, 6, 7, 8 для j=1-4, соответственно, 25, 26, 27 для j=2-4, соответственно, 40, 41 для j=3, j=4, соответственно;  - разрядные синхронные регистры хранения информации 66, 67, 68, 69, j=1-4; n-разрядные регистры-«защелки» 24, 39, 48, 49 и синхронный регистр 56; ПЗУ 17, 18, 19, 33, 34 организации

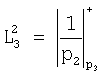

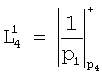

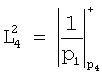

- разрядные синхронные регистры хранения информации 66, 67, 68, 69, j=1-4; n-разрядные регистры-«защелки» 24, 39, 48, 49 и синхронный регистр 56; ПЗУ 17, 18, 19, 33, 34 организации  для вычисления

для вычисления  ,

,  , где f=1-3 при m=1, и f=1-2 при m=2; ПЗУ 45 организации

, где f=1-3 при m=1, и f=1-2 при m=2; ПЗУ 45 организации  и 32, 52 организации 22nxn для вычисления

и 32, 52 организации 22nxn для вычисления  , k=1-4; ПЗУ 58, 59, 60, 61 организации

, k=1-4; ПЗУ 58, 59, 60, 61 организации  для вычисления

для вычисления  , j=1-4; блок управления 9.

, j=1-4; блок управления 9.

Устройство работает следующим образом.

Первоначальное состояние устройства: на регистры 66, 67, 68, 69 подан с блока управления 9 сигнал 11, запрещающий передачу сохраненных данных; на регистр 56 подан запрещающий передачу сигнал 55. Первый и последний циклы функционирования устройства отличаются от внутренних циклов. Первый цикл заключается в следующем. По шинам 1, 2, 3, 4 на вход устройства подаются остатки искомого числа  ,

, ,

, ,

, по основаниям p1,p2,p3,p4 соответственно. На регистры 5, 6, 7, 8 подается сигнал 10, переводящий регистры в режим хранения. С шин 1, 2, 3, 4 сигналы снимаются. Записанная в регистрах 5, 6, 7, 8 информация по шинам 13, 14, 15, 16, соответственно, поступает на адресные входы ПЗУ 17, 18, 19. В ПЗУ 17, 18, 19 по адресам

по основаниям p1,p2,p3,p4 соответственно. На регистры 5, 6, 7, 8 подается сигнал 10, переводящий регистры в режим хранения. С шин 1, 2, 3, 4 сигналы снимаются. Записанная в регистрах 5, 6, 7, 8 информация по шинам 13, 14, 15, 16, соответственно, поступает на адресные входы ПЗУ 17, 18, 19. В ПЗУ 17, 18, 19 по адресам  ,

,  ,

,  , соответственно, где || - оператор конкатенации, записаны константы

, соответственно, где || - оператор конкатенации, записаны константы  ,

,  ,

,  соответственно. На информационные входы регистра 24 заводятся младшие n разрядов шины 13. Через время, равное времени выборки одного ПЗУ на регистры 24, 25, 26, 27, подается сигнал «защелкивания» 20 передаваемой информации по шинам 13, 21, 22, 23, соответственно. Сохраненная в регистрах 24, 25, 26, 27 информация поступает на адресные входы ПЗУ 32, 33, 34. На адресные входы ПЗУ 32 заводятся младшие n разрядов шины 29. В ПЗУ 32 по адресам

соответственно. На информационные входы регистра 24 заводятся младшие n разрядов шины 13. Через время, равное времени выборки одного ПЗУ на регистры 24, 25, 26, 27, подается сигнал «защелкивания» 20 передаваемой информации по шинам 13, 21, 22, 23, соответственно. Сохраненная в регистрах 24, 25, 26, 27 информация поступает на адресные входы ПЗУ 32, 33, 34. На адресные входы ПЗУ 32 заводятся младшие n разрядов шины 29. В ПЗУ 32 по адресам  записаны константы

записаны константы  . В ПЗУ 33, 34 по адресам

. В ПЗУ 33, 34 по адресам  ,

,  записаны константы

записаны константы  ,

,  соответственно. Информация с ПЗУ 32, 33, 34 по шинам 36, 37, 38 поступает на информационные входы регистров 39, 40, 41, соответственно. На регистры 39, 40, 41 подается стробирующий сигнал 35, переводящий регистры в режим хранения. Сохраненная в регистре 39 информация по шине 42 поступает на входы регистра 48. Сохраненная в регистрах 40, 41 информация 43, 44, соответственно, поступает на адресные входы ПЗУ 45. В ПЗУ 45 по адресам

соответственно. Информация с ПЗУ 32, 33, 34 по шинам 36, 37, 38 поступает на информационные входы регистров 39, 40, 41, соответственно. На регистры 39, 40, 41 подается стробирующий сигнал 35, переводящий регистры в режим хранения. Сохраненная в регистре 39 информация по шине 42 поступает на входы регистра 48. Сохраненная в регистрах 40, 41 информация 43, 44, соответственно, поступает на адресные входы ПЗУ 45. В ПЗУ 45 по адресам  записаны константы

записаны константы  . С выхода ПЗУ 45 поступает информация 47 на входы регистра 49. На регистры 48 и 49 поступает сигнал записи информации 46. С регистров 48, 49 по шинам 50, 51, соответственно, поступает сохраненная в данных регистрах информация на адресные входы ПЗУ 52. В ПЗУ 52 по адресам

. С выхода ПЗУ 45 поступает информация 47 на входы регистра 49. На регистры 48 и 49 поступает сигнал записи информации 46. С регистров 48, 49 по шинам 50, 51, соответственно, поступает сохраненная в данных регистрах информация на адресные входы ПЗУ 52. В ПЗУ 52 по адресам  , хранятся константы

, хранятся константы  . С выхода ПЗУ 52 данные 53 поступают на входы регистра 56. На регистр 56 с блока управления 9 поступает сигнал сохранения информации 54 и снимается сигнал запрета передачи данных 55. С выхода регистра 56 считываются первые (младшие) n бит искомого двоичного представления числа S по шине 57. Сигнал 57 поступает на адресные входы ПЗУ 58, 59, 60, 61. На свободные адресные входы ПЗУ 58, 59, 60, 61 поступают сигналы 13, 14, 15, 16, соответственно. В ПЗУ 58, 59, 60, 61 по адресам

. С выхода ПЗУ 52 данные 53 поступают на входы регистра 56. На регистр 56 с блока управления 9 поступает сигнал сохранения информации 54 и снимается сигнал запрета передачи данных 55. С выхода регистра 56 считываются первые (младшие) n бит искомого двоичного представления числа S по шине 57. Сигнал 57 поступает на адресные входы ПЗУ 58, 59, 60, 61. На свободные адресные входы ПЗУ 58, 59, 60, 61 поступают сигналы 13, 14, 15, 16, соответственно. В ПЗУ 58, 59, 60, 61 по адресам  ,

,  ,

,  ,

,  , соответственно, хранятся константы

, соответственно, хранятся константы  ,

,  ,

,  ,

,  , соответственно. Данные 62, 63, 64, 65 с ПЗУ 58. 59, 60, 61 поступают на информационные входы регистров 66, 67, 68, 69, соответственно. На регистры 66, 67, 68, 69 с блока управления 9 поступает сигнал сохранения информации 12. На регистр 56 подается сигнал 55, запрещающий передачу данных, и снимается сигнал запрета передачи данных 11 с регистров 66, 67, 68, 69. С регистров 5, 6, 7, 8, 24, 25, 26, 27, 39, 40, 41, 48, 49, 56 снимаются сигналы сохранения данных. Первый цикл завершен. Действия в циклах со второго по предпоследний одинаковы. Работа устройства во втором цикле заключается в следующем. На регистры 5, 6, 7, 8 подается сигнал 10 записи информации

, соответственно. Данные 62, 63, 64, 65 с ПЗУ 58. 59, 60, 61 поступают на информационные входы регистров 66, 67, 68, 69, соответственно. На регистры 66, 67, 68, 69 с блока управления 9 поступает сигнал сохранения информации 12. На регистр 56 подается сигнал 55, запрещающий передачу данных, и снимается сигнал запрета передачи данных 11 с регистров 66, 67, 68, 69. С регистров 5, 6, 7, 8, 24, 25, 26, 27, 39, 40, 41, 48, 49, 56 снимаются сигналы сохранения данных. Первый цикл завершен. Действия в циклах со второго по предпоследний одинаковы. Работа устройства во втором цикле заключается в следующем. На регистры 5, 6, 7, 8 подается сигнал 10 записи информации  ,

,  ,

,  ,

,  поступающей с регистров 66, 67, 68, 69 по шинам 70, 71, 72, 73, соответственно. С регистров 66, 67, 68, 69 снимается сигнал-«защелка» 12. Записанная в регистрах 5, 6, 7, 8 информация поступает на адресные входы ПЗУ 17, 18, 19 по шинам 13. 14, 15, 16. С выходов регистра 5 и ПЗУ 17, 18, 19 информация поступает на информационные входы регистров 24, 25, 26, 27 по шинам 13, 21, 22, 23, соответственно. На регистры 24, 25, 26, 27 подается сигнал «защелкивания» информации 20. С выходов регистров 24, 25, 26, 27 записанная информация поступает на адресные входы ПЗУ 32, 33, 34 по шинам 28, 29, 30, 31. Записанные в ПЗУ 32, 33, 34 константы поступают на информационные входы регистров 39, 40, 41 по шинам 36, 37, 38, соответственно. На регистры 39, 40, 41 подается сигнал сохранения информации 35. Информация 43, 44 с регистров 40, 41 поступает на адресные входы ПЗУ 45. С выхода регистра 39 по шине 42 и выхода ПЗУ 45 по шине 47 информация поступает на информационные входы регистров 48, 49, соответственно. На регистры 48, 49 с блока управления 9 подается сигнал записи 46. С регистров 48, 49 по шинам 50, 51, соответственно, информация поступает на адресные входы ПЗУ 52. С выхода ПЗУ 52 по шине 53 поступают данные на информационные входы регистра 56. На регистр 56 поступает сигнал сохранения информации 54 и снимается сигнал запрета передачи данных 55. С выхода регистра 56 считываются вторые n бит искомого двоичного представления числа S по шине 57. Сигнал 57 поступает на адресные входы ПЗУ 58, 59, 60. 61. На свободные адресные входы ПЗУ 58, 59, 60, 61 поступают сигналы 13, 14, 15, 16, соответственно. Данные 62, 63, 64, 65 с ПЗУ 58, 59, 60, 61 поступают на информационные входы регистров 66, 67, 68, 69, соответственно. На регистры 66, 67, 68, 69 с блока управления 9 поступает сигнал сохранения информации 12. На регистр 56 подается сигнал 55, запрещающий передачу данных. С регистров 5, 6, 7, 8, 24, 25, 26, 27, 39, 40, 41, 48, 49, 56 снимаются сигналы сохранения данных. Второй цикл завершен. Последний цикл под номером

поступающей с регистров 66, 67, 68, 69 по шинам 70, 71, 72, 73, соответственно. С регистров 66, 67, 68, 69 снимается сигнал-«защелка» 12. Записанная в регистрах 5, 6, 7, 8 информация поступает на адресные входы ПЗУ 17, 18, 19 по шинам 13. 14, 15, 16. С выходов регистра 5 и ПЗУ 17, 18, 19 информация поступает на информационные входы регистров 24, 25, 26, 27 по шинам 13, 21, 22, 23, соответственно. На регистры 24, 25, 26, 27 подается сигнал «защелкивания» информации 20. С выходов регистров 24, 25, 26, 27 записанная информация поступает на адресные входы ПЗУ 32, 33, 34 по шинам 28, 29, 30, 31. Записанные в ПЗУ 32, 33, 34 константы поступают на информационные входы регистров 39, 40, 41 по шинам 36, 37, 38, соответственно. На регистры 39, 40, 41 подается сигнал сохранения информации 35. Информация 43, 44 с регистров 40, 41 поступает на адресные входы ПЗУ 45. С выхода регистра 39 по шине 42 и выхода ПЗУ 45 по шине 47 информация поступает на информационные входы регистров 48, 49, соответственно. На регистры 48, 49 с блока управления 9 подается сигнал записи 46. С регистров 48, 49 по шинам 50, 51, соответственно, информация поступает на адресные входы ПЗУ 52. С выхода ПЗУ 52 по шине 53 поступают данные на информационные входы регистра 56. На регистр 56 поступает сигнал сохранения информации 54 и снимается сигнал запрета передачи данных 55. С выхода регистра 56 считываются вторые n бит искомого двоичного представления числа S по шине 57. Сигнал 57 поступает на адресные входы ПЗУ 58, 59, 60. 61. На свободные адресные входы ПЗУ 58, 59, 60, 61 поступают сигналы 13, 14, 15, 16, соответственно. Данные 62, 63, 64, 65 с ПЗУ 58, 59, 60, 61 поступают на информационные входы регистров 66, 67, 68, 69, соответственно. На регистры 66, 67, 68, 69 с блока управления 9 поступает сигнал сохранения информации 12. На регистр 56 подается сигнал 55, запрещающий передачу данных. С регистров 5, 6, 7, 8, 24, 25, 26, 27, 39, 40, 41, 48, 49, 56 снимаются сигналы сохранения данных. Второй цикл завершен. Последний цикл под номером  или

или  заключается в следующем. На регистры 5, 6, 7, 8 подается сигнал 10 записи информации

заключается в следующем. На регистры 5, 6, 7, 8 подается сигнал 10 записи информации  ,

,  ,

,  ,

,  поступающей с регистров 66, 67, 68, 69 по шинам 70, 71, 72, 73 соответственно. С регистров 66, 67, 68, 69 снимается сигнал-«защелка» 12 и подается сигнал 11, запрещающий передачу данных. Записанная в регистрах 5, 6, 7, 8 информация поступает на адресные входы ПЗУ 17, 18, 19 по шинам 13, 14, 15, 16. С выходов регистра 5 и ПЗУ 17, 18, 19 информация поступает на информационные входы регистров 24, 25, 26, 27 по шинам 13, 21, 22, 23, соответственно. На регистры 24, 25, 26, 27 подается сигнал «защелкивания» информации 20. С выходов регистров 24, 25, 26, 27 записанная информация поступает на адресные входы ПЗУ 32, 33, 34 по шинам 28, 29, 30, 31. Записанные в ПЗУ 32, 33, 34 константы поступают на информационные входы регистров 39, 40, 41 по шинам 36, 37, 38, соответственно. На регистры 39, 40, 41 подается сигнал сохранения информации 35. Информация 43, 44 с регистров 40, 41 поступает на адресные входы ПЗУ 45. С выхода регистра 39 по шине 42 и выхода ПЗУ 45 по шине 47 информация поступает на информационные входы регистров 48, 49, соответственно. На регистры 48, 49 с блока управления 9 подается сигнал записи 46. С регистров 48, 49 по шинам 50, 51, соответственно, информация поступает на адресные входы ПЗУ 52. С выхода ПЗУ 52 по шине 53 поступают данные на информационные входы регистра 56. На регистр 56 поступает сигнал сохранения информации 54 и снимается сигнал запрета передачи данных 55. С выхода регистра 56 считываются последние (старшие) n бит искомого двоичного представления числа S по шине 57. На регистр 56 подается сигнал запрета передачи данных. С регистров 5, 6, 7, 8, 24, 25, 26, 27, 39, 40, 41, 48, 49, 56 снимаются сигналы сохранения данных. Последний цикл завершен.

поступающей с регистров 66, 67, 68, 69 по шинам 70, 71, 72, 73 соответственно. С регистров 66, 67, 68, 69 снимается сигнал-«защелка» 12 и подается сигнал 11, запрещающий передачу данных. Записанная в регистрах 5, 6, 7, 8 информация поступает на адресные входы ПЗУ 17, 18, 19 по шинам 13, 14, 15, 16. С выходов регистра 5 и ПЗУ 17, 18, 19 информация поступает на информационные входы регистров 24, 25, 26, 27 по шинам 13, 21, 22, 23, соответственно. На регистры 24, 25, 26, 27 подается сигнал «защелкивания» информации 20. С выходов регистров 24, 25, 26, 27 записанная информация поступает на адресные входы ПЗУ 32, 33, 34 по шинам 28, 29, 30, 31. Записанные в ПЗУ 32, 33, 34 константы поступают на информационные входы регистров 39, 40, 41 по шинам 36, 37, 38, соответственно. На регистры 39, 40, 41 подается сигнал сохранения информации 35. Информация 43, 44 с регистров 40, 41 поступает на адресные входы ПЗУ 45. С выхода регистра 39 по шине 42 и выхода ПЗУ 45 по шине 47 информация поступает на информационные входы регистров 48, 49, соответственно. На регистры 48, 49 с блока управления 9 подается сигнал записи 46. С регистров 48, 49 по шинам 50, 51, соответственно, информация поступает на адресные входы ПЗУ 52. С выхода ПЗУ 52 по шине 53 поступают данные на информационные входы регистра 56. На регистр 56 поступает сигнал сохранения информации 54 и снимается сигнал запрета передачи данных 55. С выхода регистра 56 считываются последние (старшие) n бит искомого двоичного представления числа S по шине 57. На регистр 56 подается сигнал запрета передачи данных. С регистров 5, 6, 7, 8, 24, 25, 26, 27, 39, 40, 41, 48, 49, 56 снимаются сигналы сохранения данных. Последний цикл завершен.

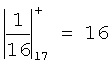

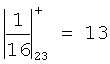

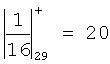

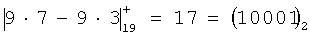

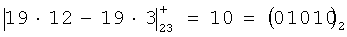

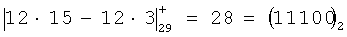

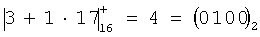

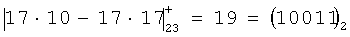

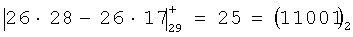

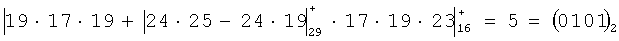

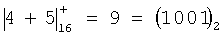

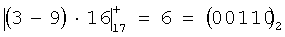

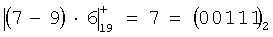

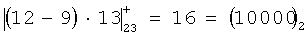

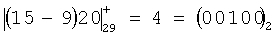

Рассмотрим численный пример. Пусть задана система остаточных классов с основаниями р1=17, р2=19, р3=23, p4=29. Тогда,  , 2n=16, Т=5. Константы L1 2=9, L1 3=19, L1 4=12, L2 3=17, L2 4=26, L3 4=24,

, 2n=16, Т=5. Константы L1 2=9, L1 3=19, L1 4=12, L2 3=17, L2 4=26, L3 4=24,  ,

,  ,

,  ,

,  . Следовательно, устройство содержит пятиразрядные регистры-«защелки» 5, 6, 7, 8, 25, 26, 27, 40, 41; пятиразрядные синхронные регистры хранения информации 66, 67, 68, 69; четырехразрядные регистры-«защелки» 24, 39, 48, 49 и синхронный регистр 56; ПЗУ 17, 18, 19, 33, 34 организации 210×5; ПЗУ 45 организации 210×4; ПЗУ 32, 52 организации 28×4; ПЗУ 58, 59, 60, 61 организации 29×5. Рассмотрим процесс преобразования числа A=(214441)10=(3,7,12,15)СОК= =(110100010110101001)2 из СОК в двоичную систему счисления. Рассмотрим первый цикл. Через регистры 5, 6, 7, 8 на адресные входы ПЗУ 17, 18, 19 поступают адреса 0001100111, 0001101100, 0001101111, соответственно, полученные в результате конкатенации остатков в двоичном представлении: 3||7, 3||12, 3||15, соответственно. С выходов ПЗУ 17, 18, 19 по шинам 21, 22, 23 на информационные входы регистров 25, 26, 27 поступают константы

. Следовательно, устройство содержит пятиразрядные регистры-«защелки» 5, 6, 7, 8, 25, 26, 27, 40, 41; пятиразрядные синхронные регистры хранения информации 66, 67, 68, 69; четырехразрядные регистры-«защелки» 24, 39, 48, 49 и синхронный регистр 56; ПЗУ 17, 18, 19, 33, 34 организации 210×5; ПЗУ 45 организации 210×4; ПЗУ 32, 52 организации 28×4; ПЗУ 58, 59, 60, 61 организации 29×5. Рассмотрим процесс преобразования числа A=(214441)10=(3,7,12,15)СОК= =(110100010110101001)2 из СОК в двоичную систему счисления. Рассмотрим первый цикл. Через регистры 5, 6, 7, 8 на адресные входы ПЗУ 17, 18, 19 поступают адреса 0001100111, 0001101100, 0001101111, соответственно, полученные в результате конкатенации остатков в двоичном представлении: 3||7, 3||12, 3||15, соответственно. С выходов ПЗУ 17, 18, 19 по шинам 21, 22, 23 на информационные входы регистров 25, 26, 27 поступают константы  ,

,  ,

,  , соответственно. На вход регистра 24 поступают 4 младших разряда шины 13, по которым передается число 0011. На адресные входы ПЗУ 32, 33, 34 поступают числа 00110001, 1000101010, 1000111100, соответственно. С выходов ПЗУ 32, 33, 34 константы

, соответственно. На вход регистра 24 поступают 4 младших разряда шины 13, по которым передается число 0011. На адресные входы ПЗУ 32, 33, 34 поступают числа 00110001, 1000101010, 1000111100, соответственно. С выходов ПЗУ 32, 33, 34 константы  ,

,  ,

,  , соответственно, поступают на информационные входы регистров 39, 40, 41. С регистров 40, 41 на адресные входы ПЗУ 45 поступает по шинам 43, 44 число 1001111001. С выхода ПЗУ 45 по шине 47 на вход регистра 49 поступает число

, соответственно, поступают на информационные входы регистров 39, 40, 41. С регистров 40, 41 на адресные входы ПЗУ 45 поступает по шинам 43, 44 число 1001111001. С выхода ПЗУ 45 по шине 47 на вход регистра 49 поступает число  . С регистров 48, 49 по шинам 50, 51 на адресные входы ПЗУ 52 поступает адрес 01000101. С выхода ПЗУ 52 по шине 53 на вход регистра 56 поступает число

. С регистров 48, 49 по шинам 50, 51 на адресные входы ПЗУ 52 поступает адрес 01000101. С выхода ПЗУ 52 по шине 53 на вход регистра 56 поступает число  . После подачи сигнала записи 54 и снятия сигнала запрета передачи сохраненной информации с шины 57 считываются первые (младшие) 4 бита искомого двоичного представления числа А. На адресные входы ПЗУ 58, 59, 60, 61 поступают адреса 000111001, 001111001, 011001001, 011111001, соответственно. С выходов ПЗУ 58, 59, 60, 61 на входы регистров 66, 67, 68, 69 по шинам 62, 63, 64, 65 соответственно, поступают константы

. После подачи сигнала записи 54 и снятия сигнала запрета передачи сохраненной информации с шины 57 считываются первые (младшие) 4 бита искомого двоичного представления числа А. На адресные входы ПЗУ 58, 59, 60, 61 поступают адреса 000111001, 001111001, 011001001, 011111001, соответственно. С выходов ПЗУ 58, 59, 60, 61 на входы регистров 66, 67, 68, 69 по шинам 62, 63, 64, 65 соответственно, поступают константы  ,

,  ,

,  ,

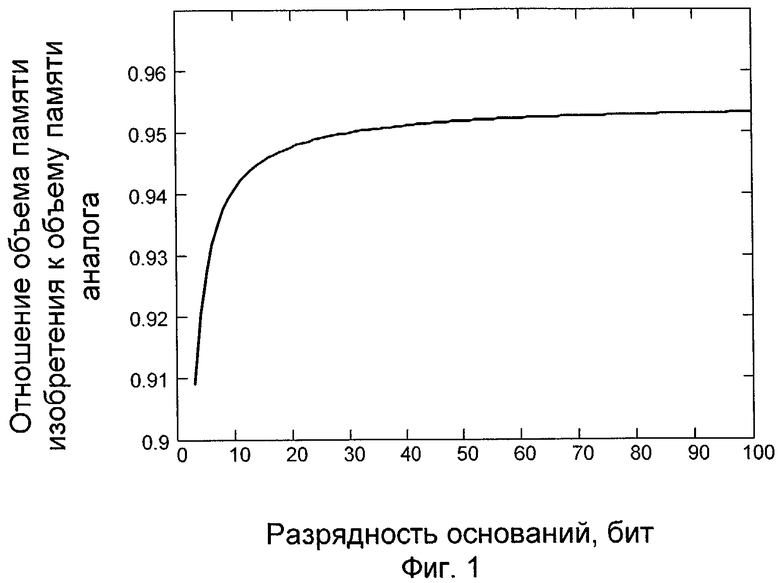

,  В таблице 1 представлены пять циклов функционирования заявляемого устройства, через сигналы на соответствующих шинах. Объединяя числа из последнего столбца таблицы 1 («Выходной сигнал») получим искомое представление числа А=(3,7,12,15)СОК=(110100010110101001)2.

В таблице 1 представлены пять циклов функционирования заявляемого устройства, через сигналы на соответствующих шинах. Объединяя числа из последнего столбца таблицы 1 («Выходной сигнал») получим искомое представление числа А=(3,7,12,15)СОК=(110100010110101001)2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Табличный процессор | 1982 |

|

SU1108446A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ЖИДКОСТИ | 1991 |

|

RU2012848C1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для входного контроля изделий | 1990 |

|

SU1746388A2 |

| Устройство для обработки видеоинформации | 1988 |

|

SU1640714A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

Изобретение относится к области вычислительной техники и может быть использовано в системах связи и обработки информации, функционирующих в системе остаточных классов. Технический результат заключается в снижении аппаратурных затрат преобразователя чисел из системы остаточных классов в позиционную двоичную систему счисления. Поставленная цель достигается за счет последовательного вычисления всех цифр искомого представления числа, что позволяет сократить общий объем ПЗУ устройства и исключить сумматор большой разрядности. 3 ил., 1 табл.

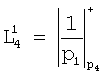

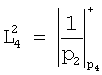

Устройство для преобразования чисел из системы остаточных классов в позиционную систему счисления, содержащее четыре входных регистра, выход s1 первого из которых соединен с адресными входами четырех ПЗУ, выход s2 второго регистра присоединен к свободным адресным входам первого из четырех ПЗУ, в котором по адресу s1||s2 записаны константы  , где || - оператор конкатенации, a

, где || - оператор конкатенации, a  , данные с которого поступают на свободные адресные входы четвертого, пятого и шестого ПЗУ, выход s3 третьего регистра подключен к свободным адресным входам второго ПЗУ, в котором по адресу s1||s3 записаны константы

, данные с которого поступают на свободные адресные входы четвертого, пятого и шестого ПЗУ, выход s3 третьего регистра подключен к свободным адресным входам второго ПЗУ, в котором по адресу s1||s3 записаны константы  , где

, где  , выход которого связан со свободными адресными входами пятого ПЗУ, в котором по адресу

, выход которого связан со свободными адресными входами пятого ПЗУ, в котором по адресу  записаны константы

записаны константы  , где

, где  , а выход s4 четвертого регистра соединен со свободными адресными входами третьего ПЗУ, в котором по адресу s1||s4 записаны константы

, а выход s4 четвертого регистра соединен со свободными адресными входами третьего ПЗУ, в котором по адресу s1||s4 записаны константы  , где

, где  , данные с которого поступают на свободные адресные входы шестого ПЗУ, в котором по адресу

, данные с которого поступают на свободные адресные входы шестого ПЗУ, в котором по адресу  записаны константы

записаны константы  , где

, где  , а p1, p2, p3, р4 - основания системы остаточных классов, данные с выхода которого и выхода пятого ПЗУ поступают на вход седьмого ПЗУ, отличающееся тем, что добавлены четыре ПЗУ для операций взвешенного вычитания по каждому основанию, необходимого для реализации округления в остаточном представлении на каждом цикле работы устройства по числу 2n, адресные входы которых связаны соответственно с выходами четырех входных регистров и с выходом добавленного выходного регистра, причем выходы подключены соответственно к добавленным четырем регистрам, данные с которых поступают соответственно на четыре входных регистра, емкость четвертого и седьмого ПЗУ сокращены за счет хранения по адресам

, а p1, p2, p3, р4 - основания системы остаточных классов, данные с выхода которого и выхода пятого ПЗУ поступают на вход седьмого ПЗУ, отличающееся тем, что добавлены четыре ПЗУ для операций взвешенного вычитания по каждому основанию, необходимого для реализации округления в остаточном представлении на каждом цикле работы устройства по числу 2n, адресные входы которых связаны соответственно с выходами четырех входных регистров и с выходом добавленного выходного регистра, причем выходы подключены соответственно к добавленным четырем регистрам, данные с которых поступают соответственно на четыре входных регистра, емкость четвертого и седьмого ПЗУ сокращены за счет хранения по адресам  и

и  , соответственно, редуцированных по модулю 2n данных

, соответственно, редуцированных по модулю 2n данных  и

и  , выходы которых соединены с адресными входами восьмого ПЗУ организации 22n×n для вычисления за один цикл работы устройства n цифр числа в двоичном счислении, где n=[log2(p1-1)], p1 - младшее основание, [] -оператор извлечения целой части, причем выход восьмого ПЗУ соединен с входом выходного регистра.

, выходы которых соединены с адресными входами восьмого ПЗУ организации 22n×n для вычисления за один цикл работы устройства n цифр числа в двоичном счислении, где n=[log2(p1-1)], p1 - младшее основание, [] -оператор извлечения целой части, причем выход восьмого ПЗУ соединен с входом выходного регистра.

| US 5008668 А, 16.04.1991 | |||

| Модулярные параллельные вычислительные структуры нейропроцессорных систем./Под ред | |||

| Н.И | |||

| Червякова | |||

| М.: ФИЗМАТЛИТ, 2003 | |||

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1985 |

|

SU1267625A1 |

| Преобразователь чисел из кода системы счисления в остаточных классах в двоичный код | 1988 |

|

SU1541783A1 |

| US 4281391 A, 28.07.1981. | |||

Авторы

Даты

2006-04-27—Публикация

2004-06-25—Подача