Изобретение относится к импульсной цифровой технике, предназначено для выполнения с помощью входной непрерывной последовательности тактовых импульсов полной функции тактовой синхронизации входного синхронизируемого цифрового сигнала (формирования синхронизированного сигнала и его тактового синхросигнала) с заградительной фильтрацией входного сигнала как помехи при длительности его нулевой или единичной фазы, не превышающей длительности периода тактовых импульсов, и может быть использовано при построении синхронных устройств (синхронных автоматов с памятью) для помехоустойчивого ввода асинхронных команд или данных и обмена информацией (командами и данными), например, между двумя синхронными устройствами, каждое из которых имеет собственную тактовую частоту синхронизации.

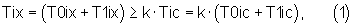

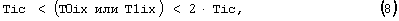

Известно (см., например, [1], [2, с.251, с.252]), что при обмене информацией корректная тактовая синхронизация входного синхронизируемого цифрового сигнала IX с помощью входных тактовых импульсов IC, по отношению к которым сигнал IX асинхронен, возможна при определении частоты 1/Tic тактовых импульсов IC, исходя из условия

при выборе k≥4 с учетом быстродействия элементной базы устройства и реальных допусков на фазовое дрожание переходов (джиттер) сигнала IX,

где Tix - переменный в определенных пределах период входного синхронизируемого цифрового сигнала IX;

T0ix и T1ix - длительность нулевой и единичной фаз синхронизируемого сигнала IX при IX=0 и IX=1 соответственно;

Tic - длительность периода входного тактового сигнала IC;

T0ic и Т1ic - длительность нулевой и единичной фаз тактового сигнала IC при IC=0 и IC=1 соответственно.

Для современной элементной базы и предельном, меньшем величины 0,25·(Tix)min, искажении периода Tix по модулю из-за "джиттера" сигнала IX выберем k согласно ограничению

где (Tix)min - минимальная длительность периода неискаженного входного сигнала IX.

Принимая во внимание (1) и (2), определим длительность нулевой T0ix или единичной T1ix фазы сигнала IX для (Tix)min соотношением

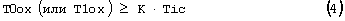

а выполнение полной функции тактовой синхронизации сигнала IX определим как формирование выходного синхронизированного сигнала ОХ=0 (или ОХ=1) длительности

и формирование его выходного тактового синхросигнала (синхронизирующего сигнала) ОСХ длительности

при каждом обнаружении перехода синхронизируемого сигнала IX в противоположное состояние,

где Т0ох или Т1ох - длительность нулевой или единичной фазы сигнала ОХ при ОХ=0 или ОХ=1 соответственно;

К - целое число, не меньшее двух.

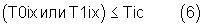

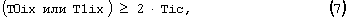

С учетом (1)-(3) в каждом периоде Tix синхронизации сигнал IX определим на временной оси как помеху при

или как корректный информационный сигнал при

или как сигнал с неопределенным (искаженным) временным параметром

который в процессе обработки может быть отнесен к помехе (6) или к корректному сигналу (7).

В общем случае при искажении сигнала IX помехами наличие интервала неопределенности типа (8) длительности Tic неустранимо, так как обусловлено асинхронностью помех и сигнала IX относительно тактовых импульсов IC.

Известно (см., например, [2], [3, с.135-137], [4, с.119, 120], [5, с.205-207]), что при построении любой цифровой системы (как совокупности асинхронных и/или синхронных автоматов с памятью) постоянно возникает необходимость синхронизировать входные асинхронные сигналы системы с работой ее устройств, функционирующих по тактовым импульсам одного или нескольких тактовых генераторов. В этой связи в цифровой технике задача синхронизации асинхронных сигналов является традиционной и известно большое число разнообразных устройств для синхронизации асинхронных цифровых сигналов по тактовым импульсам, например, [2, с.248, рис.8.3], [3, с.135, рис.4.10б], [4, с.120, рис.3.19], [5, с.206, рис.6.26], [6, с.265, рис.14-3], [7], [8] из технической литературы и [9]-[32] по патентной информации, которые работают по входным тактовым импульсам IC и входному асинхронному сигналу IX.

Основным недостатком любого из указанных выше устройств синхронизации является ограниченность функциональных возможностей, поскольку каждое из них не ориентировано явно на выполнение полной функции тактовой синхронизации (формирование ОХ и ОСХ соответственно с длительностями (4) и (5) с учетом определений (6)-(8)) цифрового сигнала IX для помехоустойчивого ввода команд и/или данных в синхронное устройство или для обмена информацией между двумя синхронными устройствами, каждое из которых имеет собственную тактовую частоту синхронизации.

Здесь следует отметить, что при установленных входных информационных сигналах синхронизация (изменение состояния автомата с памятью) в асинхронной системе производится с помощью соответствующих синхроимпульсов (при формировании синхроимпульса с помощью IC, его длительность совпадает с длительностью T0ic нулевой или длительностью T1ic единичной фазы периода Tic тактовых импульсов IC), а в синхронной системе синхронизация осуществляется логически по функции "И", т.е. по фронтам (переходам из "0" в "1") или срезам (переходам из "1" в "0") тактовых импульсов IC и соответствующим синхросигналам, установленным до прихода фронта или среза IC, причем длительность каждого синхросигнала обычно кратна целому числу периодов Tic.

Кроме того, в настоящее время и на длительную перспективу основным методом обработки информации в цифровых системах является синхронный метод тактирования по фронтам или срезам одного или нескольких генераторов тактовых импульсов с помощью синхросигналов - см., например, [4, с.121-123: 3.5. Введение в проблематику и методику проектирования автоматов с памятью].

На основании изложенного выше можно сказать, что для построения синхронных цифровых систем создание простого устройства тактовой синхронизации цифрового сигнала, реализующего полную функцию тактовой синхронизации цифрового сигнала IX, описанную с помощью соотношений (1)-(8), является актуальной технической проблемой.

Рассмотрим два простых технических решения устройств синхронизации, которые можно использовать для выполнения части полной функции тактовой синхронизации асинхронного (синхронизируемого) цифрового сигнала IX с учетом того, что фронтами или срезами любого цифрового сигнала являются его переходы из "0" в "1" или из "1" в "0" соответственно.

Известно устройство [7], содержащее первый и второй триггеры, элемент И, входы асинхронного сигнала IX и Логической "1", соединенные соответственно с тактовым и информационным входами первого триггера, выход синхросигнала ОС1, соединенный с выходом второго триггера, асинхронным входом сброса первого триггера и первым входом элемента И, тактовый вход сигнала IC, соединенный с вторым входом элемента И и тактовым входом второго триггера, информационный вход которого соединен с выходом сигнала Х1 первого триггера, и выход синхроимпульса

ОС2=ОС1&IC,

являющийся выходом элемента И, где "&" - оператор логической операции "И" на языке ABEL.

В исходном состоянии первый и второй триггеры находятся в состояниях Х1=0 и ОС1=0 соответственно. Из исходного состояния по каждому фронту сигнала IX=1 длительности T1ix≥Tmin (где Tmin - минимальная длительность импульса на тактовом входе первого триггера, обеспечивающая бесперебойное функционирование первого триггера) первый триггер переключается в состояние Х1=1. При Х1=1 по ближайшему фронту IC второй триггер переключается в состояние ОС1=1, сбрасывает первый триггер в состояние Х1=0, разрешает элементу И формирование синхроимпульса ОС2=1 по IC=1, а по следующему фронту IC второй триггер сбрасывается в состояние ОС1=0 и устройство [7] возвращается в исходное состояние: Х1=0, ОС1=0.

Таким образом, по каждому фронту асинхронного сигнала IX при T1ix≥Tmin (где параметр Tmin при реализации устройства определяется быстродействием элементной базы) устройство [7] формирует синхросигнал ОС1=1 в течение Tic и синхроимпульс ОС2=1 в течение T1ic единичной фазы IC, причем ОС1 частично подобен синхросигналу ОСХ при выполнении функции полной тактовой синхронизации сигнала IX.

Основным недостатком устройства [7] является ограниченность его функциональных возможностей, поскольку оно предназначено для формирования синхроимпульсов ОС2 как командных, а синхросигнал ОСХ=ОС1 формируется в устройстве попутно только по фронту сигнала IX.

Известно устройство [8], содержащее два триггера, элемент И, вход синхронизируемого сигнала IX, соединенный с информационным входом первого триггера, выход сигнала Х1 которого соединен с первым входом элемента И и информационным входом второго триггера, инверсный выход сигнала NX2 которого соединен с вторым входом элемента И, тактовый вход сигнала IC, соединенный с тактовыми входами первого и второго триггеров, и выход синхросигнала ОС1=(Х1&NX2), являющийся выходом элемента И, где "N=!" - оператор операции "НЕ" на языке ABEL.

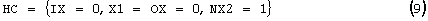

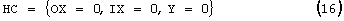

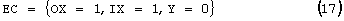

В зависимости от значения сигнала IX работу устройства [8] можно описать как последовательность переходов устройства из нулевого состояния (НС)

в единичное состояние (ЕС)

и наоборот из ЕС (10) в НС(9).

Переход из НС (9) в ЕС (10) происходит регулярно по фронту IX при Т1ix>Tic так, что по ближайшему фронту тактового сигнала IC первый триггер устанавливается в Х1=1, и элемент И формирует сигнал ОС1=1. По следующему фронту сигнала IC второй триггер устанавливается в NX2=0, элемент И формирует сигнал ОС1=0, и устройство переходит в ЕС (10).

Переход из ЕС (10) в НС (9) осуществляется регулярно по срезу IX при T0ix>Tic так, что по ближайшему фронту тактового сигнала IC первый триггер сбрасывается в X1=0, а по следующему фронту сигнала IC второй триггер сбрасывается в NX2=1 и устройство переходит в НС (9).

Таким образом, устройство [8] работает так, что при Т1ix>Tic по каждому фронту синхронизируемого IX формирует синхросигнал ОС1=1 в течение Tic и попутно вырабатывает синхронизированный сигнал Х1=ОХ, причем ОС1 частично подобен синхросигналу ОСХ при выполнении функции полной тактовой синхронизации сигнала IX.

Основным недостатком устройства [8] является ограниченность его функциональных возможностей, поскольку в устройстве синхросигнал ОСХ=ОС1 формируется регулярно по фронту сигнала IX только при Т1ix>Tic, а синхронизированный сигнал Х=ОХ вырабатывается попутно корректно только при (T0ix или Т1ix)>Tic.

На основе рассмотренных выше простейших устройств [7] и [8], с учетом определения (6), можно построить устройство с функцией предлагаемого. Однако такое техническое решение будет сложным (иметь большое число элементов и связей между ними), что обусловлено узкой специализацией его составных частей.

Из известных технических решений наиболее близким к предлагаемому по сложности (количеству составных частей и числу связей между ними) и принципу фильтрации цифрового сигнала IX как помехи, определенной согласно (6), является устройство [24], содержащее три триггера, элемент И-НЕ, вход синхронизируемого сигнала IX, соединенный с входом сброса и информационным входом первого триггера, прямой выход которого соединен с информационным входом второго триггера, прямой выход которого соединен с первым входом элемента И-НЕ и информационным входом, и входом сброса третьего триггера, вход Логической "1", соединенный с входом сброса второго триггера, тактовый вход, соединенный с тактовыми входами первого и второго триггеров и вторым входом элемента И-НЕ, и выход инверсного синхроимпульса NOC1, соединенный с выходом элемента И-НЕ и тактовым входом третьего триггера, инверсный выход которого соединен с третьим входом элемента И-НЕ, причем входы сброса всех триггеров являются асинхронными и инверсными.

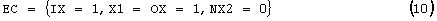

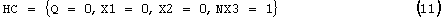

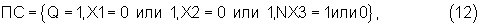

Обозначив сигналы на выходах первого, второго и третьего триггеров соответственно через Х1, Х2 и NX3 (где NX3=!X3 - инверсное значение Х3), функционирование устройства [24] как автомата с памятью можно описать в виде последовательности переходов его из нулевого состояния (НС)

в переходное состояние

из ПС (12) обратно в НС (11) или в единичное состояние (ЕС)

из ЕС (13) в ПС(12) и т.д., причем функция "Q" является признаком переходного состояния устройства [24] и определяется логической формулой

где "!=N", "&", "#" и "$" - здесь и далее на языке ABEL операторы операций "НЕ", "И", "ИЛИ" и "Исключающее ИЛИ" соответственно.

Каждый переход из НС (11) в ПС (12) инициируется переключением IX из "0" в "1", и при IX=1 по ближайшему фронту тактового сигнала IC через время dT первый триггер устанавливается в Х1=1, и дальнейшее функционирование устройства [24], в зависимости от величины (Т1ix - dT), определится одним из двух случаев поведения сигнала IX в течение текущего периода Tic.

В первом случае при (T1ix-dT)>Tic по следующему фронту сигнала IC второй триггер устанавливается в Х2=1, и по текущему значению IC=1 элемент И-НЕ генерирует выходной синхроимпульс NОС1=!IC=0 согласно логической формуле NOC1=!(IC&X2&NX3). Далее по фронту сигнала NОС1=0 третий триггер устанавливается в NX3=0, и устройство переходит в ЕС (13), в котором сигналом NX3=0 запрещена работа элемента И-НЕ по третьему входу.

Во втором случае при (T1ix-dT)<Tic сигнал IX переключится из "1" в "0" и асинхронно сбросит первый триггер в течение текущего периода Tic до первого фронта IC после установки первого триггера в Х1=1, т.е. устройство [24] из ПС (12) асинхронно перейдет в НС (11) и проигнорирует как помеху изменение во времени сигнала IX(t)=0→1→0 при (Т1ix-dT)<Tic.

Каждый переход из ЕС (13) в НС (11) осуществляется по переключению IX из "1" в "0" так, что по IX=0 первый триггер асинхронно сбрасывается в Х1=0. При Х1=0 по ближайшему фронту тактового сигнала IC второй триггер переключается в Х2=0, асинхронно сбрасывает третий триггер в NX3=1 и устройство переходит в НС (11).

Если устройство [24] находится в ЕС (13) и возникает кратковременная помеха IX=0 длительности Tr≥2·Тз«Tic (где Тз - средняя задержка распространения сигнала IX=0 через элемент первого триггера по входу сброса), то первый триггер асинхронно сбрасывается в Х1=0. После исчезновения этой помехи устройство [24] при IX=1 оказывается в помеховом переходном состоянии ПС (12) при IX=1, Х1=0, Х2=1 и NX3=0, и по ближайшему фронту тактового сигнала IC устройство [24] переходит в ПС (12) при IX=1, Х1=1, Х2=0 и NX3=1. Далее при IX=1 по следующему фронту сигнала IC второй триггер устанавливается в Х2=1 и по текущему значению IC=1 элемент И-НЕ генерирует помеховый выходной синхроимпульс NОС1=!IC=0, после окончания которого устройство [24] возвращается в ЕС (13).

Таким образом, по каждому корректному изменению асинхронного сигнала IX(1)=0→1→10 при IX(t)=1 в течение T1ix≥(2·Tic) устройство [24] регулярно генерирует выходной синхроимпульс NОС1=!IC=0 в процессе перехода по графу НС (11) →ПС (12)→ЕС (13), а также попутно формирует синхронизированный сигнал Х2=ОХ.

Кроме того, по каждому даже кратковременному помеховому переключению асинхронного сигнала IX(t) из "1" в "0" при IX(t)=0 в течение T0ix≥Tr в процессе перехода по графу ЕС (13)→ПС (12)→ЕС (13) устройство [24] генерирует помеховый выходной синхроимпульс NОС1=!IC=0.

Легко видеть, что устройство [24] целесообразно применять только в том случае, когда после перехода в ЕС (13) входной сигнал IX=1 устойчив, т.е. во времени отсутствуют помеховые изменения сигнала IX(t) из "1" в "0".

Основными недостатками устройства [24] являются низкая помехоустойчивость в ЕС (13) и ограниченность функциональных возможностей (устройство тактовый синхросигнал ОСХ не формирует, а синхронизированный сигнал ОХ=Х2 вырабатывает попутно), поскольку оно предназначено для помехоустойчивого формирования командного синхроимпульса

NOC1=!(IC&X2&NX3)

с заградительной фильтрацией как помехи цифрового сигнала IX только для единичной фазы сигнала IX при условии Т1ix≤Tic.

Предлагаемым изобретением решается задача повышения помехоустойчивости устройства и комплексного расширения его функциональных возможностей за счет выполнения с помощью входных тактовых импульсов IC полной функции тактовой синхронизации входного синхронизируемого цифрового сигнала IX (формирования на первом и втором выходах устройства синхронизированного сигнала ОХ и его тактового синхросигнала ОСХ соответственно) с заградительной фильтрацией как помехи сигнала IX при длительности его нулевой T0ix или единичной T1ix фазы, не превышающей длительности периода Tic тактовых импульсов IC.

Для достижения этого технического результата в устройство тактовой синхронизации цифрового сигнала, содержащее три триггера, прямой выход первого из которых соединен с информационным входом второго триггера, тактовый вход, соединенный с тактовыми входами первого и второго триггеров, вход синхронизируемого цифрового сигнала, вход Логической "1" и первый выход, дополнительно введены второй выход, элемент ИЛИ-НЕ, выход которого соединен с асинхронным инверсным входом сброса первого триггера, и элемент Исключающее ИЛИ, выход которого соединен с первым входом элемента ИЛИ-НЕ, причем вход Логической "1" устройства соединен с информационным входом и асинхронным инверсным входом установки первого триггера, и асинхронными инверсными входами сброса и установки второго и третьего триггеров, вход синхронизируемого цифрового сигнала устройства является первым входом элемента Исключающее ИЛИ, второй вход которого соединен с информационным входом и инверсным выходом третьего триггера, прямой выход которого является первым выходом устройства и выходом синхронизированного сигнала, а второй выход устройства является выходом тактового синхросигнала и соединен с прямым выходом второго триггера, тактовым входом третьего триггера и вторым входом элемента ИЛИ-НЕ.

Автору неизвестны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение элемента ИЛИ-НЕ, элемента Исключающее ИЛИ и второго выхода) предлагаемого устройства, которые, по сравнению с прототипом [24], повышают помехоустойчивость устройства и комплексно расширяют его функциональные возможности за счет выполнения с помощью входных тактовых импульсов IC полной функции тактовой синхронизации входного синхронизируемого цифрового сигнала IX (формирования на первом и втором выходах устройства синхронизированного сигнала ОХ и его тактового синхросигнала ОСХ соответственно) с заградительной фильтрацией как помехи сигнала IX при длительности его нулевой T0ix или единичной Т1ix фазы, не превышающей длительности периода Tic тактовых импульсов IC.

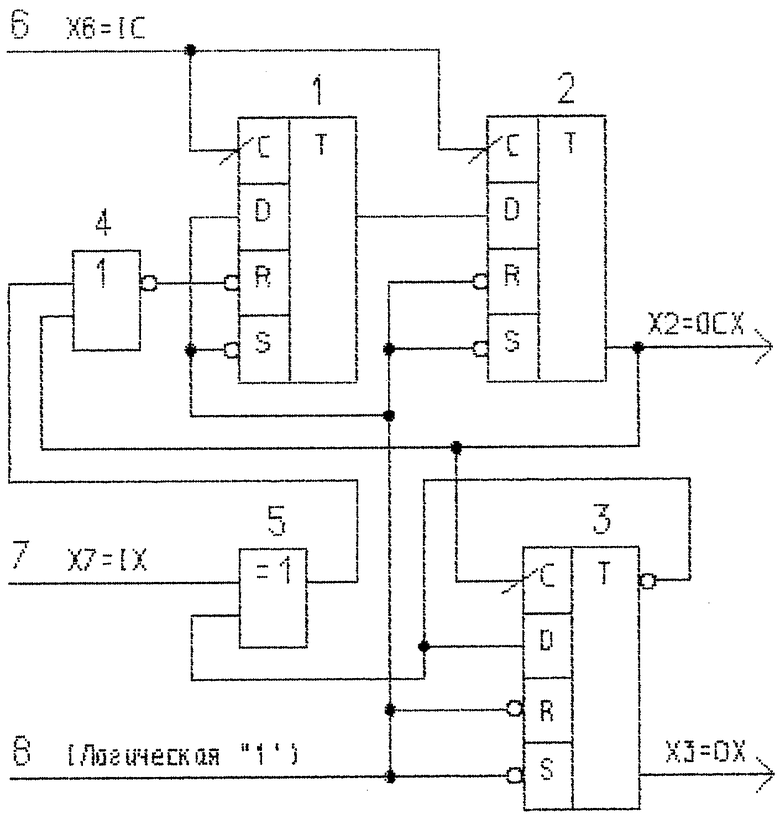

На чертеже приведена функциональная электрическая схема устройства для тактовой синхронизации цифрового сигнала, содержащего триггеры с первого 1 по третий 3, элемент 4 ИЛИ-НЕ, выход которого соединен с асинхронным инверсным входом сброса первого триггера 1, прямой выход которого соединен с информационным входом второго триггера 2, элемент 5 Исключающее ИЛИ, выход которого соединен с первым входом элемента 4 ИЛИ-НЕ, тактовый вход 6, соединенный с тактовыми входами первого 1 и второго 2 триггеров, вход 7 синхронизируемого цифрового сигнала, являющийся первым входом элемента 5 Исключающее ИЛИ, второй вход которого соединен с информационным входом и инверсным выходом третьего триггера 3, вход 8 Логической "1", соединенный с информационным входом и асинхронным инверсным входом установки первого триггера 1 и асинхронными инверсными входами сброса и установки второго 2 и третьего 3 триггеров, первый выход, являющийся выходом синхронизированного сигнала и прямым выходом третьего триггера 3, и второй выход, являющийся выходом тактового синхросигнала и прямым выходом второго триггера 2, который соединен с тактовым входом третьего триггера 3 и вторым входом элемента 4 ИЛИ-НЕ.

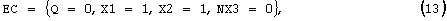

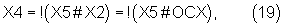

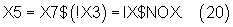

Обозначим через Х1-Х5 и Х6 и Х7 значения сигналов соответственно на выходах составных частей 1-5 устройства и его входах 6 и 7 при Х2=ОСХ, Х3=ОХ, X6=IC, X7=IX и введем обобщенный признак переходного состояния устройства

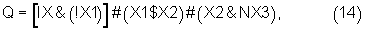

С использованием принятых обозначений функционирование предлагаемого устройства в процессе перехода из нулевого состояния (НС)

или единичного состояния (ЕС)

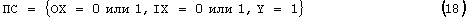

в переходное состояние (ПС)

и из ПС (18) в НС (16) или ЕС (17) опишем с учетом комбинационного функционирования элементов 4 и 5 по следующим логическим формулам:

В исходном состоянии НС (16) (или ЕС (17)) значения сигналов ОХ и IX одинаковы, сигнал Х5=1, признак Y=0, и по Х4=0 триггер 1 зафиксирован в состоянии Х1=0. Каждый переход из НС (16) (или ЕС (17)) в ПС (18) инициируется переходом сигнала IX=Х7 в IX=1 (или IX=0), по которому элементы 4 и 5 согласно (19) и (20) формируют соответственно сигналы Х4=1 и Х5=0, и устройство переходит в ПС (18)при Y=Х4=1.

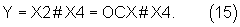

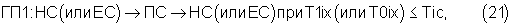

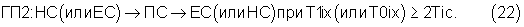

С учетом сказанного выше далее работу устройства логично описать как цепочку переходов из одного состояния в другое в виде последовательности или чередования двух следующих графов переходов (ГП1) и (ГП2):

В каждом случае функционирования по (21) входной сигнал IX=1 (или IX=0) проходит через элементы 5 и 4 как помеха Х4=1, разрешающая установку в Х1=1 триггера 1 по ближайшему фронту тактового сигнала IC.

Если помеха Х4=1 оканчивается раньше ближайшего фронта тактового сигнала IC, то с переходом входного сигнала в IX=0 (или IX=1) устройство из ПС (18) возвращается в НС (16) (или ЕС (17)).

Если помеха Х4=1 попадает в зону тактирования по IC триггера 1, то при Х4=1 по ближайшему фронту IC триггер 1 устанавливается в Х1=1. Затем в течение текущего периода Tic помеха Х4=1 оканчивается раньше появления следующего фронта тактового сигнала IC. Поэтому в течение текущего периода Tic по переходу входного сигнала в IX=0 (или IX=1) сигнал Х4 переключается из "1" в "0" и асинхронно сбрасывает триггер 1 в Х1=0 до прихода очередного фронта тактового сигнала IC, и устройство из ПС (18) возвращается в НС (16) (или ЕС (17)).

В случае функционирования согласно (22) при Х4=1 по ближайшему фронту тактового сигнала IC триггер 1 устанавливается в Х1=1, по следующему фронту тактового сигнала IC триггер 2 устанавливается в Х2=1 и формирует выходной тактовый синхросигнал Х2=ОСХ=1, по фронту которого триггер 3 переключается в противоположное состояние и формирует выходной синхронизированный сигнал Х3=ОХ=1 (или Х3=ОХ=0). При Х2=ОСХ=1 элемент 4 вырабатывает сигнал Х4=0, по которому триггер 1 асинхронно сбрасывается в Х1=0. Далее при Х1=Х4=0 по очередному фронту тактового сигнала IC триггер 2 сбрасывается в Х2=ОСХ=0, и при IX=Х7=1 (или IX=Х7=0) устройство оказывается в ЕС (17) (или НС (16)).

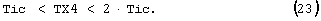

Появление на входе 7 устройства сигнала IX с неопределенным временным параметром (8) вызывает формирование сигнала Х4=1, длительность ТХ4 которого определяется соотношением

В рассматриваемом случае после перехода элемента 4 в Х4=1 через время dT по ближайшему фронту тактового сигнала триггер 1 устанавливается в Х1=1, а дальнейшая работа устройства определится длительностью времени (ТХ4-dT) так, что устройство функционирует при (ТХ4-dT)<Tic согласно ГП (21), а при (ТХ4-dT)>Tic согласно (22), что было описано ранее.

Таким образом, непосредственно из описаний технических решений прототипа [24] и данного устройства тактовой синхронизации цифрового сигнала следует, что благодаря существенным признакам предлагаемое устройство помехоустойчивее прототипа и по сравнению с ним имеет значительно расширенные функциональные возможности за счет выполнения с помощью входных тактовых импульсов IC полной функции тактовой синхронизации входного синхронизируемого цифрового сигнала IX (формирования на первом и втором выходах устройства соответственно синхронизированного сигнала ОХ и его тактового синхросигнала ОСХ) с заградительной фильтрацией как помехи сигнала IX при длительности его нулевой T0ix или единичной T1ix фазы, не превышающей длительности периода Tic тактовых импульсов IC.

При использовании данного устройства для построения синхронной цифровой системы входной асинхронный цифровой сигнал IX при вводе команды является командным, а при вводе данных представляет собой, например, последовательный код любого самосинхронизирующегося двухуровневого кода, например манчестерского, Миллера и т.п.

В первом случае в цифровой системе по аргументам ОХ=Х3 и ОСХ=Х2 формируется командный синхросигнал ОХ&ОСХ (или !ОХ&ОСХ) для ввода требуемой команды по фронту соответствующего тактового импульса IC.

Во втором случае в цифровой системе осуществляется ввод данных в процессе декодирования синхронизированного сигнала ОХ последовательного самосинхронизирующегося двухуровневого кода с помощью тактового синхросигнала ОСХ этого кода и тактовых импульсов IC.

Литература

1. А.с. СССР 1524181, Н 03 М 5/00, 5/14. Устройство для декодирования манчестерского кода. О.Д.Алексеенко, С.И.Алмаев, М.Г.Долгих, Э.П.Ващилин и Т.И.Смоленская. - Опубл. 1989. БИ №43.

2. Потемкин И.С. Функциональные узлы цифровой автоматики. - М.: Энергоатомиздат, 1988. - 320 с. ил, с.244-252: ГЛАВА 8. СХЕМЫ ПРИЕМА ВНЕШНИХ СИГНАЛОВ.

3. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. - М.: Мир, 2001. - 379 с. ил.

4. Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ-Петербург, 2001. - 528 с. ил.

5. Бойко Е.П. и др. Схемотехника электронных систем. Цифровые устройства. Авторы: В.И.Бойко, А.Н.Гуржий, В.Я.Жуйков, А.А.Зорин, В.М.Спивак, В.В.Багрий. - СПб.: БХВ-Петербург, 2004. - 512 с. ил.

6. Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной технике. Л.: Энергоатомиздат. Ленингр. отд-ние. 1986. - 280 с. ил. "Импульсные устройства на микросхемах" - с.202-276.

7. Гутников B.C. Интегральная электроника в измерительных устройствах. - 2-е изд., перераб. и доп. - 1988. - 304 с. ил. "С.177, Рис.6.8. Схема устройства синхронизации".

8. Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник - 2-е изд., перераб. и доп. - 1990. - 512 с. ил. "С.171, Рис.5.27. Вариант построения генератора".

9. А.с. СССР 544114, Н 03 К 5/13. Устройство для синхронизации импульсов. В.И.Ильин и Г.Л.Силин. - Опубл. 1977. БИ №3.

10. А.с. СССР 552687, Н 03 К 5/13. Формирователь одиночных импульсов, синхронизированных тактовой частотой / Г.Л.Силин, В.И.Ильин, С.М.Пахомов и Г.А.Зуев. - Опубл. 1977. БИ №12.

11. А.с. СССР 645249, Н 03 К 5/01. Устройство для выделения импульса из непрерывной импульсной последовательности / И.Л.Абросимов. - Опубл. 1979. БИ №4.

12. А.с. СССР 661753, Н 03 К 5/153. Устройство для синхронизации импульсов. А.С.Чередниченко, Е.А.Евсеев и А.Н.Горбунов. - Опубл. 1979. БИ №17.

13. А.с. СССР 680160, Н 03 К 5/13. Устройство для синхронизации импульсов. В.И.Ильин, Л.П.Князева и Г.Л.Силин. - Опубл. 1979. БИ №30.

14. А.с. СССР 716144, Н 03 К 5/13, Н 03 К 5/01. Синхронизирующее устройство. Е.В.Стриженов и Т.В.Алтунов. - Опубл. 1980. Бюл. №6.

15. А.с. СССР 703900, Н 03 К 5/13. Устройство синхронизации. Н.А. Кукин. - Опубл. 1979. БИ №46.

16. А.с. СССР 739721, Н 03 К 5/13. Устройство для синхронизации импульсов. Н.Н.Макаров и М.Я.Эйнгорин. - Опубл. 1980. БИ №21.

17. А.с. СССР 741440, Н 03 К 5/13. Устройство для синхронизации импульсов. В.Э.Вершков и М.П.Шервуд. - Опубл. 1980. БИ №22.

18. А.с. СССР 744947, Н 03 К 5/13. Устройство для синхронизации импульсов. Л.Н.Герасимов, Л.Т.Сапега и Д.В.Ползунова. - Опубл. 1980. БИ №24.

19. А.с. СССР 754661, Н 03 К 5/13. Устройство синхронизации. Ф.С.Власов, А.Т.Еремин, В.И.Позамантир и О.А.Райков. - Опубл. 1980. БИ №29.

20. А.с. СССР 790209, Н 03 К 5/13. Формирователь импульсов. А.С.Чередниченко, В.А.Евсеев, А.Н.Горбунов и Ю.А.Плужников. - Опубл. 1980. БИ №47.

21. А.с. СССР 790212, Н 03 К 5/13. Устройство синхронизации импульсов. С.В.Смирнов и В.В.Скрябин. - Опубл. 1980. БИ №47.

22. А.с. СССР 864528, Н 03 К 5/13. Устройство синхронизации импульсов. С.В.Смирнов и М.П.Смирнова. - Опубл. 1981. БИ №34.

23. А. с. СССР 864529, Н 03 К 5/13. Формирователь одиночных импульсов, синхронизированных тактовой частотой. П.П.Никонович, Б.П.Царев и Г.А.Хайтин. - Опубл. 1981. БИ №34.

24. А.с. СССР 898601, Н 03 К 5/05. Устройство тактовой синхронизации. М.М.Бекеша, Н.Н.Фролов и В.А.Фокин. - Опубл. 1982. БИ №2 (Прототип).

25. А.с. СССР 930614, Н 03 К 5/00. Устройство для синхронизации импульсов. Н.С.Бибик, А.Г.Касьянов, П.П.Никонович и Л.Я.Портянко. - Опубл. 1982. БИ №19.

26. А.с. СССР 1018215, Н 03 К 5/135. Формирователь импульсов. Н.А.Бадыштов, А.А.Сорокин, Г.Н.Шестаков и Е.Н.Старостенкова. - Опубл. 1983. БИ №18.

27. А.с. СССР 1019610, Н 03 К 5/13. Устройство для формирования синхронизированных импульсов. С.В.Смирнов, Ф.Г.Киндиренко и А.Ф.Толочко. - Опубл. 1983. БИ №19.

28. А.с. СССР 1050102, Н 03 К 5/01. Формирователь импульсов. В.В.Скрябин и С.В.Смирнов. 1983. БИ №39.

29. А.с. СССР 1061254, Н 03 К 5/01. Устройство для выделения одиночного импульса. Я.В.Коханый. - Опубл. 1983. БИ №46.

30. А.с. СССР 1144187, Н 03 К 5/01. Устройство для выделения одиночного импульса. И.А.Рогачевский, Б.М.Сирота и А.В.Шинкаренко. - Опубл. 1985. БИ №9.

31. А.с. СССР 1145471, Н 03 К 5/135. Устройство тактовой синхронизации. А.Л.Ратанов и Д.М.Манкевич. - Опубл. 1985. БИ №10.

32. А.с. СССР 1160550, Н 03 К 5/135. Формирователь одиночного импульса. Г.Ю.Козодаев и С.К.Харин. 1985. БИ №21.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 2005 |

|

RU2280947C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ АСИНХРОННОГО ЦИФРОВОГО СИГНАЛА | 2004 |

|

RU2279181C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 2005 |

|

RU2286007C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ ДВУХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2005 |

|

RU2290755C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ КОДОВОГО СИГНАЛА | 2007 |

|

RU2345479C1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

Устройство тактовой синхронизации цифрового сигнала относится к импульсной цифровой технике. Техническим результатом является повышение помехоустойчивости устройства и комплексного расширения его функциональных возможностей за счет формирования на выходах устройства синхронизированного сигнала и его тактового синхросигнала с заградительной фильтрацией как помехи входного синхронизируемого цифрового сигнала при длительности его нулевой или единичной фазы, не превышающей длительности периода входных тактовых импульсов. Для этого устройство содержит три триггера, вход Логической "1", тактовый вход, вход синхронизируемого цифрового сигнала и первый выход, кроме того, новым в устройстве является то, что оно дополнительно содержит элемент ИЛИ-НЕ, элемент Исключающее ИЛИ и второй выход, причем первый выход устройства является выходом третьего триггера и синхронизированного сигнала, а второй выход устройства является выходом тактового синхросигнала и соединен с выходом второго триггера, тактовым входом третьего триггера и вторым входом элемента ИЛИ-НЕ. 1 ил.

Устройство тактовой синхронизации цифрового сигнала, содержащее три триггера, прямой выход первого из которых соединен с информационным входом второго триггера, тактовый вход, соединенный с тактовыми входами первого и второго триггеров, вход синхронизируемого цифрового сигнала, вход Логической "1" и первый выход, отличающееся тем, что оно дополнительно содержит второй выход, элемент ИЛИ-НЕ, выход которого соединен с асинхронным инверсным входом сброса первого триггера, и элемент Исключающее ИЛИ, выход которого соединен с первым входом элемента ИЛИ-НЕ, причем вход Логической "1" устройства соединен с информационным входом и асинхронным инверсным входом установки первого триггера и асинхронными инверсными входами сброса и установки второго и третьего триггеров, вход синхронизируемого цифрового сигнала устройства является первым входом элемента Исключающее ИЛИ, второй вход которого соединен с информационным входом и инверсным выходом третьего триггера, прямой выход которого является первым выходом устройства, который является выходом синхронизированного сигнала, а второй выход устройства является выходом тактового синхросигнала и соединен с прямым выходом второго триггера, тактовым входом третьего триггера и вторым входом элемента ИЛИ-НЕ.

| Устройство тактовой синхронизации | 1980 |

|

SU898601A1 |

| УСТРОЙСТВО ДЛЯ ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 1992 |

|

RU2013015C1 |

| RU 2058059 C1, 10.04.1996 | |||

| Состав электродного покрытия для наплавки | 1974 |

|

SU502732A1 |

| US 4593207 A, 03.06.1986 | |||

| US 5252977 A, 12.10.1993. | |||

Авторы

Даты

2006-10-10—Публикация

2005-02-08—Подача