Изобретение относится к области вычислительной техники, предназначено для приема двухуровневого кодированного дифференциального сигнала двоичного последовательного самосинхронизирующегося кода с преобразованием в двухразрядный цифровой сигнал Z(1:0) и последующим помехоустойчивым выполнением полной функции синхронизации этого сигнала с помощью входной непрерывной последовательности тактовых импульсов IC за счет помехоустойчивого формирования выходного синхронизированного сигнала OZ приема бита кода и выходных синхросигналов битовой синхронизации OCZ, начала паузы ОРС и паузы OPZ, и может быть использовано в качестве синхронного помехоустойчивого формирователя синхронизированного сигнала OZ приема бита кода и синхросигналов OCZ, ОРС, OPZ для любого двухуровневого кода класса 1В2В, в частности манчестерского по ГОСТ 26765.52-87 (зарубежные стандарты MIL-STD-1533B и MIL-STD-1773), биимпульсного или Миллера по ГОСТ 27232-87 и т.п.

Двухуровневые коды 1В2В получили широкое распространение благодаря высокой помехозащищенности и простоте преобразования и выделения сигнала битовой синхронизации [1, с.152]. Любой двухуровневый код 1В2В является избыточным и получается в процессе преобразования абсолютного безызбыточного кода NRZ без возврата к нулю так, что в каждом битовом интервале Т передачи информации каждый бит "0" (или "1") кода NRZ преобразуется по соответствующему алгоритму в два бита кода 1В2В, каждый из которых имеет длительность Т/2 - см., например, [1, с.149-153: 6.7. Способы цифровой модуляции].

Предлагаемое устройство может использоваться как составная часть при построении различных цифровых устройств (декодеров, ретрансляторов, конвертеров интерфейсов с временной компрессией/декомпрессией для согласования низкочастотных интерфейсов через одну высокопроизводительную локальную вычислительную сеть - см. [1, с.83-84: 3.8. Конверторы интерфейсов]) для обмена информацией с помощью цифрового дифференциального (разностного) сигнала

двухуровневого кода 1В2В в системах проводной связи в сложной помеховой обстановке при значительных величинах синфазной помехи

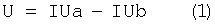

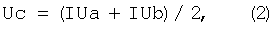

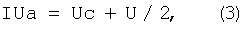

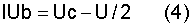

искажающей обе компоненты

сигнала U(1), т.е. при высоких значениях показателя помехоустойчивости

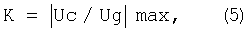

где

|X|max - оператор выделения максимального значения модуля величины Х=Uc/Ug;

IUa и IUb - соответственно первая и вторая компоненты сигнала U(1), измеряемые относительно общей шины (корпуса) устройства;

Ug=|U|min - модуль минимального информационного значения сигнала U(1).

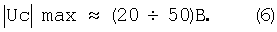

Известно [2, с.41], что практически никакие методы экранирования и разнесения проводов линий цифровой связи от энергетических проводов не могут гарантировать отсутствие в линии связи (ЛС) наводок (помех). Это означает, что полезный сигнал U(1) всегда существует совместно с помехами, и задача заключается в гарантированном, т.е. с определенным запасом устойчивости, выделении сигнала на фоне помех. С учетом реальной естественной помеховой обстановки в [2, с.41] считают, что условием бесперебойной работы аппаратуры является сигнал помехи в ЛС, не превышающий |Uc|≈10÷20 В. Однако в общем случае эта величина синфазной помехи для многих применений может быть явно заниженной [3, с.283]. Например, известен измерительный усилитель с допустимым уровнем синфазной помехи до 50 В [3, с.279, рис.7.7г]. На основании [2, с.41] и [3, с.283] определяем, что для сигнала U(1) кода 1В2В, описанного соотношениями (6)÷(12), для расчета показателя К (5) величину |Uc|max можно оценить величиной

В процессе ввода информации цифровой дифференциальный сигнал U (1) приемником-преобразователем первоначально преобразуется однозначно в цифровой сигнал, который в прямом коде Z(1:0)=Z1Z0 означает следующее:

пауза в передаче информации,

прием бита "0" кода 1В2В,

прием бита "1" кода 1В2В,

запрещенная комбинация,

причем запрещенная комбинация (10) возможна как переходная в течение некоторого времени из-за гистерезисной передаточной характеристики приемника-преобразователя сигнала U(1) при переключении с приема (8) или (9) соответственно на прием (9) или (8) при прямоугольной форме сигнала U(1).

Далее сигнал Z(1:0) вводится в цифровую систему (сложный асинхронный или синхронный автомат с памятью), которая функционирует обычно по непрерывной последовательности тактовых импульсов 1C единого системного тактового генератора, по отношению к частоте которого сигнал Z(1:0) является асинхронным и искаженным помехами. В общем случае следует также учитывать (см., например, [4]), что в предлагаемом устройстве (как любом микроэлектронном устройстве) можно выделить каналы связи для передачи сигналов, каждый из которых содержит источник сигнала, ЛС и приемник сигнала. Любой канал связи может быть как источником, так и приемником помех. В реальных условиях на каналы связи могут воздействовать несколько источников внешних индустриальных или естественных помех и внутренних помех с различными видами паразитных связей (емкостной, индуктивной, резистивной или комплексной).

Таким образом, синхронизируемый кодированный сигнал Z(1:0) маскируется помехами, и в общем случае задача его полной синхронизации должна решаться с учетом возможного искажения его различными помехами, в частности фазовыми помехами джитттером (jitter - дрожание) и вандером (wander - странствие), обусловленными, например, перекрестными помехами от других ЛС, пульсациями напряжений питания передатчика и приемника-преобразователя сигнала U(1), неблагоприятными кодовыми комбинациями при формировании сигнала U(1) линейным передатчиком, механической вибрацией, при которой некоторые радиоэлектронные элементы могут работать как преобразователи механической энергии в электрическую, дневными-ночными перепадами температуры (сверхнизкочастотным вандером) - см., например, [5, с.5].

В процессе ввода информации с помощью тактовых импульсов IC следует помехоустойчиво выполнять полную функция тактовой синхронизации сигнала Z(1:0) двухуровневого кода 1В2В, которая заключается в помехоустойчивом формировании синхронизированного сигнала OZ приема бита кода 1В2В и выходных синхросигналов битовой синхронизации OCZ, начала паузы ОРС и паузы OPZ.

Здесь следует отметить (см., например, [6], [7, с.251, с.252]), что в процессе ввода информации корректная синхронизация синхронизируемого сигнала Z(1:0), с помощью входных тактовых импульсов IC, по отношению к которым этот сигнал асинхронен, возможна при определении частоты 1/Tic тактовых импульсов IC исходя из условия

при выборе k≥4 с учетом быстродействия элементной базы устройства и реальных допусков на джиттер сигнала Z(1:0),

где

Tz - переменный в определенных пределах период синхронизируемого сигнала Z(1:0);

T1z и T2z - длительность нулевой и единичной фаз неискаженного синхронизируемого сигнала Z(1:0) при Z(1:0)=01 и Z(1:0)=10 соответственно;

Tic - длительность периода входного тактового сигнала IC;

T0ic и T1ic - длительность нулевой и единичной фаз тактового сигнала IC при IC=0 и IC=1 соответственно.

Известно также (см., например, [2, с.32-35], [8]), что при передаче сигнала U(1) по согласованной (при R=Ri) или несогласованной (при R<Ri для снижения энергетического уровня обмена информацией) ЛС существенное значение имеет форма U(1), трансформирующаяся в длительности переключения с приема (8) на прием (9) и наоборот, и длительности T1z и T2z, где R и Ri - волновое сопротивление ЛС и входное сопротивление приемника-преобразователя сигнала IUa (или IUb) соответственно. Практически при прямоугольной форме сигнала U(1) даже при R=Ri по каждому изменению сигнала U(1) в ЛС существует переходный процесс длительности Тпп [8, с.117], например при длине ЛС 15 м длительность Тпп≤75 нс. В этой связи для обеспечения наиболее помехоустойчивого ввода информации сигналом U(1) кода 1В2В необходимо использовать приемник-преобразователь с высоким входным сопротивлением, малой входной емкостью и предпочтительно с гистерезисной передаточной характеристикой [8, с.118], а сигнал U(1) целесообразно формировать трапецеидальным с длительностью фронта или среза, равной Т/4 [2, с.34, рис.2.3. трапециидальная форма импульсов], что обеспечивает максимальную пропускную способность ЛС.

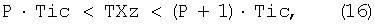

Принимая во внимание (7)-(11), для дальнейшего описания выполнение полной функции тактовой синхронизации сигнала Z(1:0) c помощью тактовых импульсов IC определим как формирование выходного синхронизированного сигнала OZ=0 (или OZ=1) приема бита кода 1В2В длительности

формирование выходного синхросигнала (синхронизирующего сигнала) битовой синхронизации OCZ длительности

при каждом обнаружении информационного перехода синхронизируемого сигнала Z(1:0) из состояния "00" в состояние "01" или "10", или из состояния "01" (или "10") в состояние "10" (или "01"), формирование выходного синхросигнала начала паузы ОРС длительности Topc=Tic при обнаружении перехода сигнала Z(1:0) из состояния "01" или "10" в состояние "00" и, после окончания синхросигнала ОРС, формирование выходного синхросигнала паузы OPZ длительности Topz, кратной целому числу периодов Tic,

где

T0oz или T1oz - длительность нулевой или единичной фазы сигнала OZ при OZ=0 или OZ=1 соответственно;

К - целое число, не меньшее "2".

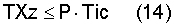

С учетом (11)-(13) длительность каждого изменения сигнала Z(1:0) обозначим через TXz, и в процессе синхронизации изменение сигнала Z(1:0), в зависимости от длительности TXz, определим как помеху при

как корректный информационный сигнал при

или как сигнал с неопределенным (искаженным) временным параметром

который в процессе обработки может быть отнесен к помехе (14) или к корректному сигналу (15),

где

Х - десятичное число "0", "1", "2" и "3", соответственно определяющее значение "00", "01", "10" и "11" сигнала Z(1:0);

Р - пороговое целое число, не меньшее "1", выбираемое с учетом (12).

Очевидно, что при искажении сигнала Z(1:0) всевозможными помехами, в том числе и переходным процессом длительностью Тпп по каждому изменению сигнала U(1), наличие интервала неопределенности типа (16) длительностью Tic принципиально неустранимо, так как обусловлено асинхронностью помех и сигнала Z(1:0) относительно импульсов IC.

Следует также сказать, что для удовлетворения показателя помехоустойчивости К (5) декодера ограничению (6) на входах его приемника-преобразователя целесообразно установить высокоомные делители - см., например, [2, с.67, рис.4.13]. Очевидно, что это приведет к снижению порога срабатывания приемника-преобразователя, т.е. к снижению помехоустойчивости формирования сигнала Z(1:0) при воздействии на приемник-преобразователь внешних и внутренних помех.

На основании изложенного можно сказать, что при построении современных цифровых систем обработки информации и управления и их составных частей проблема учета помех практически всегда актуальна вследствие наличия различных внешних и внутренних помех, снижения энергетического уровня информационных сигналов, усложнения систем и их составных частей и увеличения длины и числа внешних связей.

Таким образом, при вводе информации в цифровую систему возникает необходимость синхронизации сигнала Z(1:0) с учетом (7)-(16) и возможного искажения этого сигнала различными помехами, в их числе переходным процессом в ЛС длительностью Тпп по каждому изменению сигнала U(1) кода 1В2В.

Здесь следует отметить, что в асинхронной системе синхронизация (изменение состояния асинхронного автомата с памятью при установленных входных информационных сигналах) производится с помощью соответствующих синхроимпульсов (при формировании с помощью тактовых импульсов IC длительность синхроимпульса совпадает с длительностью T0ic, нулевой при IC=0, или длительность T1ic единичной фазы при IC=1 периода Tic=T0ic+T1ic тактовых импульсов IC), а в синхронной системе синхронизация (изменение состояния синхронного автомата с памятью при установленных входных информационных сигналах) осуществляется логически по функции "И", т.е. по фронтам (переходам из "0" в "1") или срезам (переходам из "1" в "0") тактовых импульсов IC и соответствующим синхросигналам, установленным до прихода фронта или среза IC, причем длительность каждого синхросигнала обычно кратна целому числу периодов тактовых импульсов IC.

В настоящее время и на длительную перспективу основным методом обработки информации в цифровых системах является синхронный метод тактирования по фронтам или срезам единого генератора тактовых импульсов с помощью синхросигналов - см., например, [9, с.121-123: 3.5. Введение в проблематику и методику проектирования автоматов с памятью].

На основании изложенного выше можно сказать, что создание устройства для приема и синхронизации двухуровневого кодированного сигнала U(1) кода 1В2В для ввода информации в синхронную цифровую систему с требуемыми характеристиками и учетом ограничения (6) и определений (7)-(16) при приемлемых аппаратурных затратах представляет актуальную техническую задачу, решение которой позволит в целом повысить качество разрабатываемых синхронных цифровых систем для ввода и обработки информации, являющихся составными частями современных информационно-измерительных комплексов.

Известно устройство [10], являющееся частью технического решения [10] и содержащее линейный блок (приемник-преобразователь), формирователь импульсов, вход сигнала U(1) кода 1В2В (в частности, манчестерского), являющийся входом линейного блока, выходы сигналов Z1 и Z0 кода Z(1:0), являющиеся выходами линейного блока и соединенные с первым и вторым входами формирователя импульсов соответственно, и импульсный выход короткого импульса CZ битовой синхронизации кода 1В2В, являющийся выходом формирователя импульсов, содержащего триггер, три элемента И-НЕ, первый вход сигнала Z1, соединенный с информационным входом триггера и первым входом первого элемента И-НЕ, второй вход которого соединен с инверсным выходом сигнала NTZ триггера, прямой выход сигнала TZ которого соединен с первым входом второго элемента И-НЕ при NTZ=!TZ (где "N=!" - оператор операции "НЕ" на языке ABEL), второй вход сигнала Z0, являющийся вторым входом второго элемента И-НЕ, и импульсный выход импульса CZ, соединенный с тактовым входом триггера и выходом третьего элемента И-НЕ, входы которого соединены с выходами первого и второго элементов И-НЕ.

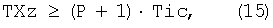

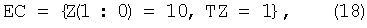

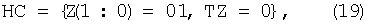

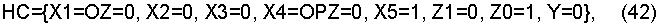

Функционирование устройства [10] как асинхронного автомата с памятью можно описать как последовательность его переходов из состояния паузы (СП)

в единичное состояние (ЕС)

из ЕС (18) в нулевое состояние (НС)

из НС (19) в ЕС (18), и из ЕС (18) или НС (19) в СП (17) при сбросе триггера в TZ=0 по сигналу сброса NR=(Z1#Z0)=0, где "#" - оператор операции "ИЛИ" на языке ABEL, причем каждый переход устройства [10] из СП (17) в ЕС (18) и из ЕС (18) (или НС (19)) в НС (19) (или ЕС (18)) осуществляется по фронту импульса CZ, который вырабатывает формирователь импульсов согласно логической формуле CZ=[(Z1&NTZ) # (Z0&TZ)], где "&" - оператор операции "И" на языке ABEL. Длительность импульса CZ можно оценить величиной Tcz=3·Тз, которая определяется задержкой фронта импульса CZ через триггер, первый (или второй) элемент И-НЕ и третий элемент И-НЕ, где Тз - средняя задержка распространения сигнала через любой элемент формирователя.

При помехоустойчивом формировании сигнала Z(1:0) в ЕС (18) или НС (19) триггер функционирует корректно и находится в состоянии TZ=Z1, и сигнал CZ формируется помехоустойчиво. Если в процессе формирования сигнала Z(1:0) появляется кратковременная помеха длительностью ≥Tcz, заключающаяся, например, при TZ=0 (или 1) в переходе сигнала Z(1:0) из состояния "01" (или "10") в переходное состояние "11", то устройство сформирует помеховый импульс CZ.

Основным недостатком устройства [10] является низкая помехоустойчивость, поскольку оно предназначено для формирования коротких импульсов CZ битовой синхронизации кода 1В2В только при помехоустойчивом информационном изменении сигнала Z(1:0) кода 1В2В.

Известно устройство [6], являющееся частью технического решения [6] и содержащее генератор импульсов, первый и второй триггеры, тактовые входы которых соединены к выходу тактовых импульсов IC генератора импульсов, элемент Исключающее ИЛИ, вход сигнала IZ бита кода 1В2В (в частности, манчестерского), являющегося информационным входом первого триггера, выход синхронизированного сигнала OZ бита кода 1В2В, соединенный с выходом первого триггера и информационным входом второго триггера, и выход синхросигнала битовой синхронизации OCZ, являющийся выходом элемента Исключающее ИЛИ, второй вход которого соединен с выходом сигнала Х2 второго триггера.

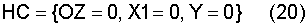

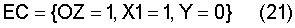

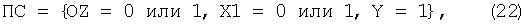

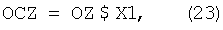

С учетом (11)-(16) при Р=1, в зависимости от значений длительностей T0iz при IZ=0 и T1iz при IZ=1, работу устройства [6] можно описать как последовательность переходов устройства из нулевого состояния (НС)

или единичного состояния (ЕС)

в переходное состояние (ПС)

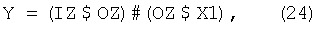

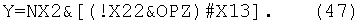

и из ПС (22) в ЕС (21) или НС (20) в процессе формирования синхросигнала битовой синхронизации OCZ по формуле

где Y - обобщенный признак переходного состояния устройства, определяемый формулой

где "$" и "#" - операторы операций "Исключающее ИЛИ" и "ИЛИ" на языке ABEL.

Если входной сигнал IZ формируется корректно согласно (15) (т.е. T0iz или Т1iz≥2·Tic), то переход устройства из НС (20) (или ЕС (21) в ЕС (21) (или НС (20)) осуществляется регулярно так, что при переключении сигнала IZ в "1" (или "0") устройство переходит в ПС (22), и по ближайшему фронту тактового сигнала первый триггер переключается в "1" (или "0"), элемент Исключающее ИЛИ устанавливает сигнал OCZ=1, а по фронту следующего импульса IC второй триггер переключается в "1" (или "0"), элемент Исключающее ИЛИ формирует сигнал OCZ=0, и устройство переходит из ПС (22) в ЕС (21) (или НС (20)).

Если входной сигнал IZ маскируется помехой (т.е. иногда формируется согласно (14) при T0iz или T1iz≤Tic), то переход устройства из НС (20) (или ЕС (21)) в ПС (22) и из ПС (22) обратно в НС (20) (или ЕС (21)) может осуществляться с формированием помехового синхросигнала OCZ=1 в течение 2·Tic. В этом случае при переключении сигнала IZ в "1" (или "0") устройство переходит в ПС (22), и если этот переход попадает в зону тактирования сигнала IC, то по ближайшему фронту этого сигнала первый триггер переключается в "1" (или "0"), элемент Исключающее ИЛИ устанавливает сигнал OCZ=1. Затем сигнал IZ возвращается в исходное состояние "0" (или "1"). Далее по фронту следующего импульса IC первый триггер возвращается в исходное состояние "0" (или "1"), а второй триггер переключается в "1" (или "0"), элемент Исключающее ИЛИ формирует сигнал OCZ=1, а по фронту следующего импульса IC второй триггер возвращается в "0" (или "1"), элемент Исключающее ИЛИ формирует сигнал OCZ=0, и устройство возвращается в исходное состояние НС (20) (или ЕС (21)).

Основным недостатком устройства [6] является низкая помехоустойчивость, поскольку оно предназначено для формирования синхронизированного сигнала OZ и синхросигнала битовой синхронизации OCZ только при помехоустойчивом изменении сигнала IZ=Z1 или IZ=TZ=Z1 согласно (15), где TZ - сигнал, формируемый, например, формирователем технического решения [10].

Из известных технических решений наиболее близким по технической сущности к предлагаемому является устройство [11], содержащее приемник-преобразователь, входы первой и второй компонент цифрового дифференциального сигнала (1), являющиеся первым и вторым входами приемника-преобразователя соответственно, элемент И, счетчик, три элемента ИЛИ, элемент И-НЕ, тактовый вход импульсов IC, являющийся первым входом элемента И-НЕ, кодовый вход кода порога Р[3:0] обнаружения паузы, являющийся кодовым входом счетчика, вход начального сброса, являющийся входом сброса счетчика, и пять выходов, первый из которых является выходом инверсного сигнала ONZ1 приема "1" кода и соединен с первым входом элемента И и первым выходом приемника-преобразователя, второй выход которого является выходом инверсного сигнала ONZO приема "0" кода и соединен с вторым выходом устройства и вторым входом элемента И, выход которого является выходом потенциального сигнала паузы OPZ=!(Z1#ZO) и третьим выходом устройства, который соединен с инверсным асинхронным входом записи счетчика, выходы старших разрядов кодового выхода которого соединены с входами первого элемента ИЛИ, выход которого соединен с первыми входами второго и третьего элементов ИЛИ, четвертый выход устройства является выходом инверсного синхроимпульса начала паузы ONCP и соединен с выходом второго элемента ИЛИ, второй вход которого соединен с вычитающим счетным входом счетчика и выходом элемента И-НЕ, второй вход которого соединен с пятым выходом устройства инверсного потенциального сигнала паузы ONPZ и выходом третьего элемента ИЛИ, второй вход которого соединен с выходом младшего разряда кодового выхода счетчика, причем приемник-преобразователь содержит два входа, два компаратора, первый и второй выходы, являющиеся выходами первого и второго компараторов соответственно, два ограничителя напряжений и четыре делителя напряжений, выходы первого и второго из которых соединены с первым и вторым входами первого ограничителя и с инвертирующим и неинвертирующим входами первого компаратора соответственно, инвертирующий и неинвертирующий входы второго компаратора соответственно соединены с выходами третьего и четвертого делителей и первым и вторым входами второго ограничителя, первый вход приемника-преобразователя соединен с первыми входами первого и четвертого делителей, первые входы второго и третьего делителей соединены со вторым входом приемника-преобразователя, вход отрицательного напряжения смещения которого соединен со вторыми входами первого и третьего делителей, общая шина (корпус) приемника-преобразователя соединена со вторыми входами второго и четвертого делителей, каждый из делителей содержит два резистора, первый вход, соединенный с первым выводом первого резистора, выход, соединенный с первым входом первого резистора и вторым входом второго резистора, и второй вход, соединенный со вторым выводом второго резистора, а каждый из ограничителей содержит два диода, первый вход, соединенный с анодом первого диода и катодом второго диода, и второй вход, соединенный с катодом первого диода и анодом второго диода.

Первый компаратор с первым и вторым делителями (или второй компаратор с третьим и четвертым делителями) образуют триггер Шмитта, а каждый из компараторов может быть выполнен, например, на основе интегрального компаратора с открытым коллекторным выходом (в частности, на интегральной микросхеме К554СА3) и двух резисторах так, что первые выводы обоих резисторов соединены с выходом интегрального компаратора, являющегося выходом первого (или второго компаратора), неинвертирующий и инвертирующий входы которого являются соответственно неинвертирующим и инвертирующим входами интегрального компаратора, неинвертирующий вход которого соединен со вторым выводом первого резистора, а второй вывод второго резистора соединен с шиной источника питания +5 В.

Показатель помехоустойчивости К (5) устройства [11] при Ug=7 В определяется параметрами приемника-преобразователя. В частности, при сопротивлении R1=10 кОм первого и сопротивлении R2=2 кОм второго резистора каждого делителя напряжений приемника-преобразователя показатель K≈11, т.е. декодер [10] по помехоустойчивости с запасом удовлетворяет ограничению (6). Легко видеть, что наличие в составе каждого компаратора устройства [11] входного делителя напряжения U(1) с коэффициентом передачи Кп=1/6 приводит к снижению порога срабатывания приемника-преобразователя, т.е. к снижению помехоустойчивости устройства [11] в течение паузы при воздействии на приемник-преобразователь внешних и внутренних помех.

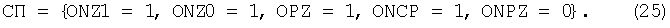

В течение паузы устройство [11] находится в состоянии паузы (СП)

При поступлении информации в коде 1В2В в течение каждого сообщения устройство [11] формирует двухразрядный асинхронный сигнал ONZ(1:0)≠11, сигналы ONCP=1, ONPZ=1 и сигнал OPZ=0, по которому в счетчик асинхронно записывается код порога Р[3:0] обнаружения паузы, а в начале поступления информации по сигналу OPZ=0 сигнал ONPZ асинхронно переключается в "1".

С наступлением паузы содержимое С[3:0] счетчика по срезу каждого тактового импульса IC начинает уменьшаться от начального значения С[3:0]=Р[3:0]=Р3Р2Р1Р0, и через время обнаружения начала паузы Т1ср

устройство [11] генерирует по 1С=1 синхроимпульс начала паузы ONCP=0, и после его окончания выставляет потенциальный инверсный сигнал паузы ONPZ=0, который не является синхросигналом, поскольку сбрасывается в ONPZ=1 асинхронно по OPZ=0.

Основным недостатком устройства [11] является значительная сложность при ограниченных функциональных возможностях (оно предназначено для работы в цифровой системе по асинхронному сигналу ONZ(1:0), синхроимпульсам ONCP начала паузы и потенциальному сигналу паузы ONPZ, который сбрасывается асинхронным сигналом OPZ=0, т.е. не является синхросигналом и с задержкой по началу логически дублирует сигнал OPZ), и низкая помехоустойчивость (из-за низкого порога срабатывания приемника-преобразователя) при возникновении внешних или внутренних помех в течение паузы или при передаче сигнала U(1) от передатчика на приемник-преобразователь по несогласованной ЛС при Ri>R, где Ri и R - входное сопротивление приемника-преобразователя сигнала IUa (или IUb) и волновое сопротивление ЛС соответственно.

Предлагаемым изобретением решается задача комплексного расширения функциональных возможностей устройства и повышения его помехоустойчивости с помощью непрерывной последовательности входных тактовых импульсов IC за счет помехоустойчивого формирования выходного синхронизированного сигнала OZ приема бита кода 1В2В и выходных синхросигналов битовой синхронизации OCZ, начала паузы ОРС и паузы OPZ с заградительной фильтрацией синхронизации цифрового сигнала Z(1:0) двухуровневого кода 1В2В как помехи при длительности каждого изменения этого сигнала, не превышающей пороговой длительности Р·Tic для Р≥2.

Для достижения этого технического результата в устройство для приема и синхронизации двухуровневого кодированного сигнала, содержащее приемник-преобразователь, входы первой и второй компонент дифференциального двухуровневого кодированного сигнала, являющиеся первым и вторым входами приемника-преобразователя соответственно, первые элементы И-НЕ и И, три элемента ИЛИ, тактовый вход, и четыре выхода, введены пять триггеров, второй элемент И-НЕ, два элемента Исключающее ИЛИ, три элемента ИЛИ-НЕ, двухвходовый асинхронный элемент задержки сигнала на его выходе относительно изменения сигнала на одном из двух входов и неизменном единичном сигнале на другом входе этого элемента, второй, третий и четвертый элементы И, тактируемый элемент задержки с задержкой на число тактов, равное или большее единицы, выход синхронизированного сигнала приема бита кода, являющийся первым выходом устройства и прямым выходом первого триггера, выход синхросигнала битовой синхронизации, являющийся вторым выходом устройства, который соединен с тактовым входом первого триггера, первыми входами первых элементов ИЛИ-НЕ и ИЛИ и выходом второго элемента ИЛИ-НЕ, первый вход которого соединен с инверсным выходом второго триггера и асинхронным инверсным входом сброса тактируемого элемента задержки, информационный вход которого соединен с прямым выходом третьего триггера, а информационный выход соединен с информационным входом второго триггера, прямой выход которого соединен с первыми входами первого элемента И и второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом третьего элемента И и информационным входом четвертого триггера, инверсный выход которого соединен с входом сброса пятого триггера, информационный вход которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с прямым выходом пятого триггера и вторым входом третьего элемента И, выход которого является выходом синхросигнала начала паузы и третьим выходом устройства, выход первого элемента И соединен с первым входом третьего элемента ИЛИ, информационный вход и вход сброса третьего триггера соединены с выходом третьего элемента ИЛИ-НЕ, первый вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом первого элемента Исключающее ИЛИ и первым входом асинхронного элемента задержки, выход которого соединен с вторым входом четвертого элемента И, третий вход которого соединен с выходом второго элемента Исключающее ИЛИ и вторым входом асинхронного элемента задержки, четвертый выход устройства является выходом синхросигнала паузы, который соединен с прямым выходом четвертого триггера, вторыми входами третьего элемента ИЛИ-НЕ и второго элемента ИЛИ и первыми входами первого и второго элементов И-НЕ, выходы которых соединены соответственно с входами сброса и установки первого триггера, первый выход приемника-преобразователя является выходом прямого сигнала приема бита "1" двухуровневого кодированного сигнала и соединен с вторыми входами первых элементов И-НЕ и ИЛИ-НЕ и первыми входами первого элемента Исключающее ИЛИ и второго элемента Исключающее ИЛИ, второй вход которого соединен с информационным входом и инверсным выходом первого триггера, второй выход приемника преобразователя является выходом прямого сигнала приема бита "0" двухуровневого кодированного сигнала и соединен с вторыми входами второго элемента И-НЕ и первого элемента Исключающее ИЛИ и третьим входом первого элемента ИЛИ-НЕ, выход которого соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с вторыми входами второго элемента ИЛИ-НЕ и первого и второго элементов И, тактовый вход устройства соединен с тактовыми входами триггеров с второго по пятый и тактовым входом тактируемого элемента задержки, причем входы установки и сброса всех триггеров устройства являются асинхронными и инверсными и не использованные из них соединены с шиной Логической "1" устройства.

Авторам неизвестны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение пяти триггеров, второго элемента И-НЕ, первого и второго элементов Исключающее ИЛИ, трех элементов ИЛИ-НЕ, второго, третьего и четвертого элементов И, асинхронного элемента задержки и тактируемого элемента задержки) предлагаемого устройства, которые (по сравнению с прототипом [11]) комплексно расширяют функциональные возможности предлагаемого декодера и повышают его помехоустойчивость с помощью непрерывной последовательности входных тактовых импульсов IC за счет помехоустойчивого формирования выходного синхронизированного сигнала OZ приема бита кода 1В2В и выходных синхросигналов битовой синхронизации OCZ, начала паузы ОРС и паузы OPZ с заградительной фильтрацией синхронизации цифрового сигнала Z(1:0) двухуровневого кода 1В2В как помехи при длительности любого изменении этого сигнала, не превышающей пороговой длительности P·Tic для Р≥2.

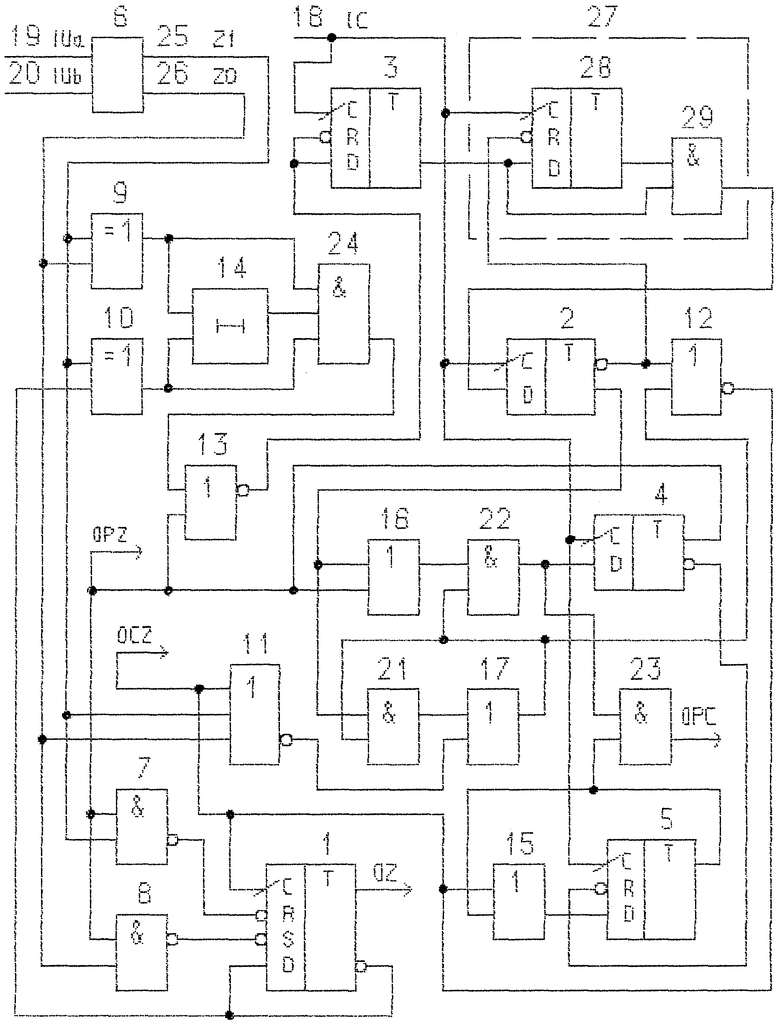

На чертеже приведена электрическая функциональная схема устройства для приема и синхронизации двухуровневого кодированного сигнала, содержащего триггеры с первого 1 по пятый 5, приемник-преобразователь 6, первый 7 и второй 8 элементы И-НЕ, первый 9 и второй 10 элементы Исключающее ИЛИ, элементы ИЛИ-НЕ с первого 11 по третий 13, двухвходовый асинхронный элемент 14 задержки сигнала на его выходе относительно изменения сигнала на одном из двух входов и неизменном единичном сигнале на другом входе элемента 14, элементы ИЛИ-НЕ с первого 15 по третий 17, тактовый вход 18, входы 19 и 20 первой и второй компонент дифференциального двухуровневого кодированного сигнала, являющиеся первым и вторым входами приемника-преобразователя 6 соответственно, элементы И с первого 21 по четвертый 24, первый 25 и второй 26 выходы приемника-преобразователя 6, тактируемый элемент 27 задержки с задержкой на число тактов, равное (Р-1) при PS2 (см. определения (14)-(16)), выход синхронизированного сигнала приема бита кода, являющийся первым выходом устройства и прямым выходом первого триггера 1, выход синхросигнала битовой синхронизации, являющийся вторым выходом устройства, который соединен с тактовым входом первого триггера 1, первыми входами первых элементов 11 ИЛИ-НЕ и 15 ИЛИ и выходом второго элемента 12 ИЛИ-НЕ, первый вход которого соединен с инверсным выходом второго триггера 2 и асинхронным инверсным входом сброса тактируемого элемента 27 задержки, информационный вход которого соединен с прямым выходом третьего триггера 3, а информационный выход соединен с информационным входом второго триггера 2, прямой выход которого соединен с первыми входами первого элемента 21 И и второго элемента 16 ИЛИ, выход которого соединен с первым входом второго элемента 22 И, выход которого соединен с первым входом третьего элемента 23 И и информационным входом четвертого триггера 4, инверсный выход которого соединен с входом сброса пятого триггера 5, информационный вход которого соединен с выходом первого элемента 15 ИЛИ, второй вход которого соединен с прямым выходом пятого триггера 5 и вторым входом третьего элемента 23 И, выход которого является выходом синхросигнала начала паузы и третьим выходом устройства, выход первого элемента 21 И соединен с первым входом третьего элемента 17 ИЛИ, информационный вход и вход сброса третьего триггера 3 соединены с выходом третьего элемента 13 ИЛИ-НЕ, первый вход которого соединен с выходом четвертого элемента 24 И, первый вход которого соединен с выходом первого элемента 9 Исключающее ИЛИ и первым входом асинхронного элемента 14 задержки, выход которого соединен с вторым входом четвертого элемента 24 И, третий вход которого соединен с выходом второго элемента 10 Исключающее ИЛИ и вторым входом асинхронного элемента 14 задержки, четвертый выход устройства является выходом синхросигнала паузы, который соединен с прямым выходом четвертого триггера 4, вторыми входами третьего элемента 13 ИЛИ-НЕ и второго элемента 16 ИЛИ и первыми входами первого 7 и второго 8 элементов И-НЕ, выходы которых соединены соответственно с входами сброса и установки первого триггера 1, первый выход 25 приемника-преобразователя 6 является выходом прямого сигнала приема бита "1" двухуровневого кодированного сигнала и соединен с вторыми входами первых элементов 7 И-НЕ и 11 ИЛИ-НЕ и первыми входами первого элемента 9 Исключающее ИЛИ и второго элемента 10 Исключающее ИЛИ, второй вход которого соединен с информационным входом и инверсным выходом первого триггера 1, второй выход 26 приемника-преобразователя 6 является выходом прямого сигнала приема бита "0" двухуровневого кодированного сигнала и соединен с вторыми входами второго элемента 8 И-НЕ и первого элемента 9 Исключающее ИЛИ и третьим входом первого элемента 11 ИЛИ-НЕ, выход которого соединен с вторым входом третьего элемента 17 ИЛИ, выход которого соединен с вторыми входами второго элемента 12 ИЛИ-НЕ и первого 21 и второго 22 элементов И, тактовый вход 18 устройства соединен с тактовыми входами триггеров с второго 2 по пятый 5 и тактовым входом тактируемого элемента 27 задержки, причем входы установки и сброса всех триггеров устройства являются асинхронными и инверсными, а не использованные из них соединены с шиной Логической "1" устройства (это на чертеже не показано).

В качестве приемника-преобразователя 6 предлагаемого устройства может быть использован приемник-преобразователь прототипа [11], дополненный первым и вторым элементами НЕ, входы которых соединены с выходами инверсных сигналов NZ1 и NZ0 первого и второго компараторов приемника-преобразователя прототипа соответственно, а выходы первого и второго элементов НЕ являются первым 25 и вторым 26 выходами сигналов Z1=X25 и Z0=X26 приемника-преобразователя 6 соответственно.

Возможный вариант асинхронного элемента 14 задержки содержит элемент И-НЕ, элемент НЕ, первый и второй входы, являющиеся входами элемента И-НЕ, и выход, являющийся выходом элемента НЕ, вход которого соединен с выходом элемента И-НЕ.

В общем случае возможный вариант реализации тактируемого элемента 27 задержки содержит триггеры, число которых равно (Р-1), элемент И, тактовый вход 18, соединенный с тактовыми входами всех триггеров элемента 27, вход сброса, соединенный с входами сброса всех триггеров элемента 27, информационный выход, являющийся выходом элемента И элемента 27, и информационный вход, являющийся информационным входом первого триггера элемента 27 и соединенный с одним из входов элемента И элемента 27, другие входы которого соединены с прямыми выходами всех триггеров элемента 27, соединенных между собой так, что информационный вход каждого последующего триггера, начиная со второго при (Р-1)≥2, соединен с прямым выходом предыдущего.

На чертеже приведена реализация тактируемого элемента 27 задержки при (Р-1)=1, который содержит триггер 28, элемент 29 И, тактовый вход 18, являющийся тактовым входом триггера 28, вход сброса, являющийся входом сброса триггера 28, информационный выход являющийся выходом элемента 29 И, и информационный вход, соединенный с информационным входом триггера 28 и одним из входов элемента 29 И, другой вход которого соединен с прямым выходом триггера 28.

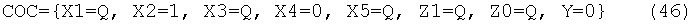

Обозначим через: Х1-Х5 и Х28 сигналы на прямых выходах триггеров 1-5 и 28 соответственно; NX1, NX2 и NX4 - сигналы на инверсных выходах триггеров 1, 2 и 4 соответственно; Х7-Х17 - сигналы на выходах элементов 7-17 соответственно; Х18=IC - сигнал на тактовом входе 18; Х21-Х24, Х27 и Х29 - сигналы на выходах элементов 21-24, 27 и 29 соответственно при Х27=Х29=(Х3&Х28); X25=Z1 и X26=Z0 - сигналы на первом 25 и втором 26 выходах приемника-декодера 6, определяющие цифровой сигнал Z(1:0)=Z1Z0=Х25Х26 (см. (7)-(10)).

Отметим также, что Х1=OZ - синхронизированный сигнал приема бита кода на первом выходе устройства, a X12=OCZ, X23=OCP и X4=OPZ - синхросигналы битовой синхронизации, начала паузы и паузы на втором, третьем и четвертом выходах устройства соответственно.

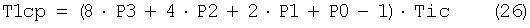

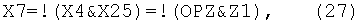

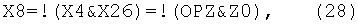

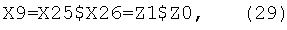

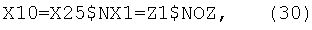

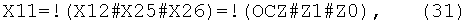

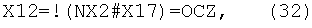

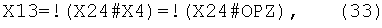

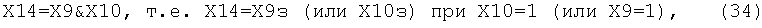

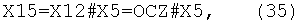

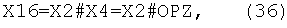

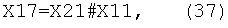

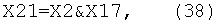

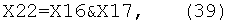

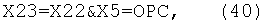

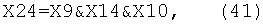

В процессе функционирования устройства при единичных сигналах на входах сброса и установки триггеры 1-5 и 28 срабатывают по фронтам сигналов, действующих на их тактовых входах, а указанные выше логические переменные Х7-Х17 и Х21-Х24 формируются комбинационно по формулам

где

"&", "!=N", "$" и "#" - на языке ABEL операторы операций "И", "НЕ", "Исключающее ИЛИ" и "ИЛИ" соответственно;

Х9з (или Х10з) - сигнал, при Х10=1 (или Х9=1) повторяющий сигнал Х9 (или Х10) с средней задержкой 2·Тз через элементы И-НЕ и НЕ, образующих элемент 14 при Тз, являющейся средней задержкой любого из элементов И-НЕ или НЕ.

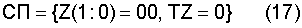

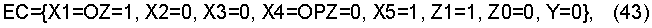

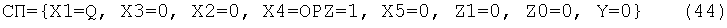

С учетом изложенного выше функционирование предлагаемого устройства как автомата с памятью логично описать как последовательность переходов из нулевого состояния (НС)

или единичного состояния (ЕС)

или из состояния паузы (СП)

в переходное состояние синхронизации (ПСС)

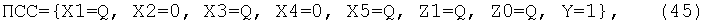

из ПСС (45) в одно из исходных состояний (42)-(44) или состояние опроса синхронизации (СОС)

длительностью Tic при Х2=1 и NX2=0, где Q - двоичная переменная, равная "0" или "1", а введенная переменная Y является признаком ПСС (45) и определяется логической формулой

В зависимости от исходного значения сигнала Х17=Х11 в момент перехода устройства в СОС (46) оно в течение длительности Tic этого состояния по Х2=1 и NX2=0 функционирует так, что при исходном Х17=Х11=1 вырабатывает синхросигналы Х12=0, Х17=Х21=Х2=1 и Х23=Х5=ОРС, а при исходном Х17=Х11=0 - синхросигналы X12=OCZ=1, X17=X11=!X12=NX2=0 и Х23=0. Таким образом, в момент начала каждого СОС (46) при Х17=1 (или Х17=0) по сигналу Х2=1 (или NX2=0) формируется сигнал Х21=1 (или Х12=1), который по цепи обратной связи поступает на первый вход элемента 17 ИЛИ (или на второй вход элемента 17 через элемент 11 ИЛИ-НЕ по первому входу), формирующего сигнал Х17=Х2=1 (или Х17=NX2=0). Это блокирует изменение сигнала Х17 при возможном изменении сигнала Z(1:0) в течение СОС (46), окончание которого отмечается сбросом триггера 2 в Х2=0 и NX2=1 по очередному фронту IC при Х27=Х28=Х29=0 и переходом устройства в одно из соответствующих состояний (42)-(45).

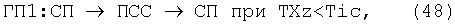

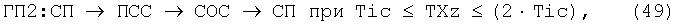

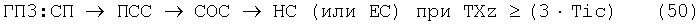

Пусть устройство исходно находится в СП (44), тогда при переходе Z(1:0) из "00" в "01" (или "10") работа предлагаемого устройства, в зависимости от длительности TXz изменения сигнала Z(1:0) и положения его относительно фронтов тактового сигнала IC, описывается как переход из одного состояния в другое в виде одного из трех графов переходов (ГП1), (ГП2) и (ГП3)

так, что в каждом случае функционирования по (48)-(50) каждый переход сигнала Z(1:0) из "00" в "01" (или в "10") отмечается установкой (или сбросом) триггера 1 в Х1=1 (или Х1=0) по Х8=0 (или Х7=0), сбросом сигнала Х10 в Х10=0 при Z1=NX1 и сигнала Х22 в Х22=0 при Х22=Х17=Х11=0, переводящем устройство в начало ПСС (45) при Х1=1 (или Х1=0"), X4=OPZ=1, X9=1, Х13=0, Х24=Х10=Х14=0 и Х22=0, разрешающем сброс триггера 4 в Х4=0 ближайшему фронту тактового сигнала IC=Х18.

В случае (48), если сигнал Z(1:0) как помеха "01" (или "10") не попадает в зону синхронизации триггера 4 по IC (т.е. оканчивается раньше ближайшего фронта сигнала IC), то с возвратом цифрового сигнала Z(1:0) в исходное состояние "00" устройство из ПСС (45) возвращается в СП (44), а если помеха попадает в зону синхронизации триггера 4, то устройство функционирует согласно ГП2 (49).

В случае (49) воздействие на устройство сигнала Z(1:0) как помехи "01" (или "10") регулярно попадает в зону синхронизации триггера 4 по IC. В этом случае при Х22=0 по первому ближайшему фронту 1C триггер 4 сбрасывается в Х4=0, элемент 13 формирует сигнал Х13=1. Далее при Х13=1 по второму фронту сигнала IC триггер 3 устанавливается в Х3=1. Но затем в течение рассматриваемого текущего отрезка времени 2·Tic сигнал Z(1:0) как помеха "01" (или "10") оканчивается раньше установки триггера 28 в Х28=1. После возврата сигнала Z(1:0) в исходное состояние "00" сигнал Х11 переключается в Х11=1, а сигнал Х13 не изменится, поскольку сигналы Х9 и Х10 практически одновременно переключатся в противоположные состояния "0" и "1" при Х24=Х14=0. Затем по третьему фронту сигнала IC триггер 28 устанавливается в Х28=1, элемент 27 вырабатывает сигнал Х27=1. Далее по четвертому фронту сигнала IC триггер 2 устанавливается в Х2=1 при Х17=Х11=1, устройство оказывается в СОС (46) при Х17=Х2=1, и по пятому фронту сигнала 1C оно возвращается в исходное состояние СП (44).

В случае функционирования согласно (50) устройство по первым трем фронтам сигнала IC функционирует согласно (49), но по четвертому фронту сигнала IC устройство переходит в СОС (46) при Z(1:0)=01 (или Z(1:0)=10), Х4=0, Х17=Х11=0, и в течение Tic формирует синхросигналы NX2=0, X12=1, Х15=Х12=1, X17=NX2=0. По NX2=0 элемент 27 сбрасывается (формирует сигнал Х27=0), по фронту синхросигнала битовой синхронизации X12=OPZ=1 триггер 1 переключается из "1" в "0" (или из "0" в "1"), элемент 10 формирует сигнал Х10=1, и через время 4·Тз<Tic элемент 13 вырабатывает сигнал Х13=0, сбрасывающий триггер 3 в Х3=0. Далее по пятому фронту сигнала 1C триггер 2 сбрасывается в Х2=0, триггер 5 устанавливается в Х5=1. После этого состояние устройства определится значением сигнала Z(1:0) так, что при Z(1:0)=01 (или Z(1:0)=10) устройство переходит в НС (42) (или ЕС (43)), а в любом другом случае устройство оказывается в ПСС (45).

Если устройство находится в СП (44), то появление на выходах 25 и 26 сигнала Z(1:0)=01 (или "10") с неопределенным временным параметром TXz (16) приводит к функционированию устройства по ГП (49) или ГП (50) следующим образом. В рассматриваемом случае триггер 4 сбрасывается в Х4=0 по первому фронту сигнала 1C через время dT после перехода устройства в ПСС (45).

Дальнейшая работа устройства определится длительностью времени (TXz-dT) сигнала Х11=0 так, что устройство функционирует при (TXz-dT)<2·Tic согласно ГП2 (49), а при (TXz-dT)>2·Tic согласно ГПЗ (50), что было описано ранее.

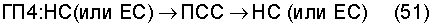

Если устройство находится в состоянии НС (42) (или ЕС (43)), то переход сигнала Z(1:0) из "01" (или "10") в любое другое состояние "00", "11", "10" (или "01") на время TXz≤2·Tic воспринимается как помеховое, обуславливающее регулярное функционирование устройства согласно четвертому графу переходов (ГП4)

так, что переход сигнала Z(1:0) из "01" или ("10") в любое другое состояние приводит к переходу сигнала Х24 из "1" в "0" по Х9=0 при Z1=Z0 или по Х10=0 при Z1=NX1. Это вызывает при Х4=0 и Х24=0 переход сигнала Х13 из "0" в "1",т.е. устройство оказывается в ПСС (45). Если сигнал Х13=1 как помеха оканчивается раньше ближайшего фронта тактового сигнала IC, то с возвратом цифрового сигнала Z(1:0) в исходное состояние "01" (или "10") устройство из ПСС (45) возвращается в НС (42) (или ЕС (43)). В случае, если воздействие на устройство сигнала Х13=1 как помехи попадает в зону синхронизации триггера 3 по IC, то по первому ближайшему фронту IC триггер 3 устанавливается в Х3=1. Если помеха далее попадает в зону синхронизации по IC элемента 27 при Х3=Х13=1, то по второму фронту сигнала IC триггер 28 и элемент 27 устанавливаются в состояния соответственно Х28=1 и Х27=1. Но затем в течение рассматриваемого текущего отрезка времени 2·Tic сигнал Х13=1 как помеха оканчивается раньше появления третьего фронта сигнала 1C. Поэтому с возвратом сигнала Z(1:0) в исходное состояние "01" (или "10") до прихода третьего фронта сигнала IC сигнал Х13 переключается в Х13=0, сбрасывает триггер 3 в Х3=0, и устройство возвращается в исходное состояние НС (42) (или ЕС (43)).

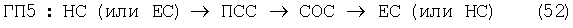

Если устройство находится в состоянии НС (42) (или ЕС (43)), то изменение сигнала Z(1:0)=01 (или "10") в течение времени TXz≥3·Tic (например, сначала, в течение T6z≤2·Tic из-за гистерезисной характеристики приемника-преобразователя 6, на значение "11" (или "00") при прямоугольной (или трапецеидальной) форме сигнала U(1), а затем на значение "10" (или "01")) обуславливает регулярное функционирование устройства по пятому графу переходов (ГП5)

так, что переход сигнала Z(1:0) из "01" или ("10") в любое другое состояние приводит к переключению сигнала Х24 из "1" в "0" по Х9=0 при Z1=Z0 или по Х10=0 при Z1=NX1, что вызывает переход устройства в ПСС (45), так как при Х4=Х24=0 сигнал Х13=1. Далее при Х13=1 по первому ближайшему фронту IC триггер 3 устанавливается в Х3=1, при Х3=Х13=1 по второму фронту сигнала IC триггер 28 и элемент 27 устанавливаются соответственно в состояния Х28=1 и Х27=1. Затем перед приходом третьего фронта IC на выходах 25 и 26 устанавливается сигнал "10" (или "01") приема бита "1" (или "0"), на выходах элементов 17 и 22 вырабатываются соответственно сигналы Х17=Х11=0 и Х22=Х17=0. При Z(1:0)=10 (или Z(1:0)=01), X4=0 и Х22=Х17=Х11=0 по третьему фронту IC устройство переходит в СОС (46), и в течение Tic формирует синхросигналы NX2=0, X12=1 и X17=NX2=0. По NX2=0 элемент 27 сбрасывается (формирует сигнал Х27=0), по фронту синхросигнала битовой синхронизации X12=OPZ=1 триггер 1 переключается из "0" в "1" (или из "1" в "0"), элемент 10 формирует сигнал Х10=1 при Х9=1, и через время 4·Тз<Tic элемент 13 вырабатывает сигнал Х13=0, сбрасывающий триггер 3 в Х3=0. Далее по четвертому фронту сигнала IC триггер 2 сбрасывается в Х2=0. После этого состояние устройства определится значением сигнала Z(1:0) так, что при Z(1:0)=10 (или Z(1:0)=01) устройство переходит в ЕС (43) (или НС (42)), а в любом другом случае устройство оказывается в ПСС (45).

Если устройство находится в состоянии НС (42) (или ЕС (43)), то появление на выходах 25 и 26 сигнала Z(1:0)=10 (или "01") с неопределенным временным параметром TXz (16) обуславливает переключение сигнала Z(1:0) так, что сначала (в течение времени T6z≤2·Tic из-за гистерезисной характеристики приемника-преобразователя 6) этот сигнал равен "11" (или "00") при прямоугольной (или трапецеидальной) форме сигнала U(1), а затем Z(1:0) переключается в состояние "10" (или "01"). В рассматриваемом случае переход сигнала Z(1:0) из "01" или ("10") в любое другое состояние приводит к переключению сигнала Х24 из "1" в "0" по Х9=0 при Z1=Z0 или по Х10=0 при Z1=NX1 так, что вызывает переход устройства в ПСС (45), поскольку при Х4=Х21=0 сигнал Х13=1. Далее при Х13=1 через время dT после перехода устройства в ПСС (45) по первому ближайшему фронту IC триггер 3 устанавливается в Х3=1. При Х3=Х13=1 по второму фронту сигнала 1C триггер 28 и элемент 27 устанавливаются соответственно в состояния Х28=1 и Х27=1. Дальнейшее работа устройства определится длительностью времени (TXz-Tic-dT) сигнала Х13=1 так, что устройство при (TXz-Tic-dT)<Tic согласно (51) возвращается в исходное состояние НС (42) (или ЕС (43), а при (TXz-Tic-dT)>Tic функционирует согласно (52), что было описано ранее.

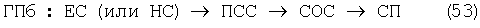

Если устройство находится в состоянии НС (42) (или ЕС (43)), то переход сигнала Z(1:0)=01 (или "10") в состояние "00" на время TXz≥3·Tic вызывает регулярное функционирование устройства по шестому графу переходов (ГП6)

так, что переход сигнала Z(1:0) из "01" или ("10") в состояние "00" приводит к переключению сигнала Х24 из "1" в "0" по Х9=0 при Z1=Z0, что вызывает переход устройства в ПСС (45), так как при Х4=Х24=0 сигнал Х13=1. Далее при Х13=1 по первому ближайшему фронту IC триггер 3 устанавливается в Х3=1. При Х3=Х13=1 по второму фронту сигнала IC триггер 28 и элемент 27 устанавливаются соответственно в состояния Х28=1 и Х27=1. Перед приходом третьего фронта IC на выходах элементов 11 и 17 вырабатываются соответственно сигналы Х11=1 и Х17=Х11=1. При Х5=1, Х11=1 и Х17=1 по третьему фронту IC устройство переходит в СОС (46), и в течение Tic формирует и сигналы NX2=0, X2=1, Х16=Х2=1, Х21=1, Х22=1, и синхросигнал Х23=Х5=ОРС=1 при Х17=Х2=1. Далее по четвертому фронту сигнала 1C триггер 2 сбрасывается в Х2=0, триггер 4 устанавливается в X4=OPZ=1. По NX4=0 триггер 5 сбрасывается в Х5=0, а по Х4=1 элемент 13 вырабатывает сигнал Х13=0, сбрасывающий триггер 3 в Х3=0. После этого состояние устройства определится значением сигнала Z(1:0) так, что при Z(1:0)=00 устройство переходит в СП (44), а при Z(1:0)≠00 устройство оказывается в ПСС (45).

Если устройство находится в состоянии НС (42) (или ЕС (43)), то появление на выходах 25 и 26 сигнала Z(1:0)=00 с неопределенным временным параметром TXz (16) приводит к функционированию устройства следующим образом. В данном случае переход сигнала Z(1:0) из "01" или ("10") в состояние "00" приводит к переключению сигнала Х24 из "1" в "0" на время TXz (16) по Х9=0 при Z1=Z0. Это вызывает переход устройства в ПСС (45), поскольку при Х4=Х24=0 сигнал Х13=1. Далее при Х13=1 через время dT после перехода устройства в ПСС (45) по первому ближайшему фронту IC триггер 3 устанавливается в Х3=1. При ХЗ=Х13=1 по второму фронту сигнала IC триггер 28 и элемент 27 устанавливаются соответственно в состояния Х28=1 и Х27=1. Дальнейшая работа устройства определится длительностью времени (TXz-Tic-dT) сигнала Х13=1 так, что устройство при (TXz-Tic-dT)<Tic возвращается в исходное состояние НС (42) (или ЕС (43) согласно ГП4 (51), а при (TXz-Tic-dT)>Tic функционирует согласно ГП6 (53), что было описано ранее.

Таким образом, с учетом (7)-(16) при Р≥2 в целом функционирование предлагаемого устройства во времени как автомата с памятью представляет собой цепочку переходов из одного состояния в другое в виде последовательности или чередования соответствующих шести графов переходов ГП1-ГП6 по допустимым изменениям сигнала Z(1:0) в течение TXz с регулярной заградительной фильтрацией синхронизации каждого изменения этого сигнала как помехи при TXz≤2·Tic (14), регулярным переходом устройства в другое состояние при TXz≥3·Tic (15) и неустойчивым функционированием при 2·Tic<TXz<3·Tic (16), т.е. с возвратом в исходное состояние или переходом в другое состояние.

Непосредственно из описаний прототипа [11] и данного устройства следует, что благодаря существенным признакам предлагаемое устройство помехоустойчивее прототипа и по сравнению с ним имеет значительно расширенные функциональные возможности за счет помехоустойчивого формирования с помощью входных тактовых импульсов IC выходного синхронизированного сигнала OZ приема бита кода 1В2В и выходных синхросигналов битовой синхронизации OCZ, начала паузы ОРС и паузы с заградительной фильтрацией синхронизации цифрового сигнала Z(1:0) двухуровневого кода 1В2В как помехи при длительности каждого изменения этого сигнала, не превышающей пороговую длительность Р·Tic для Р≥2.

Литература

1. Лагутенко О.И. Современные модемы. М.: Эко-Тренз, 2002. - 344 с.

2. Основы организации систем цифровых связей в сложных иформационно-измерительных комплексах. В.А.Ацюковский, В.Г.Бобров, А.Л.Невдяева и др. - М.: Энергоатомиздат, 2001. - 96 с.: ил. (Б-ка энергетика).

3. Гальперин М.В. Электронная техника: Учебник. - М.: ФОРУМ: ИНФРА-М, 2003. - 304 с.: ил. - (Серия "Профессиональное образование").

4. Микроэлектронные устройства автоматики: Учебн. Пособие для вузов / А.А.Сазонов, А.Ю.Лукичев, В.Т.Николаев и др.; Под ред. А.А.Сазонова. - М.: Энергоатомиздат, 1991. - 384 с.: ил. - 512 с.: ил. "С.298-304, 5.3. Паразитные связи".

5. С.М.Сухман, А.В.Бернов, Б.В.Шевкопляс. Синхронизация в телекоммуникационных системах. Анализ инженерных решений. - М.: Эко-Трендз, 2002. - 272 с.: ил.

6. А.с. СССР 1524181, Н 03 М 5/00, 5/14. Устройство для декодирования манчестерского кода. О.Д.Алексеенко, С.И.Алмаев, М.Г.Долгих, Э.П.Ващилин и Т.И.Смоленская. - Опубл. 1989. БИ №43.

7. Потемкин И. С. Функциональные узлы цифровой автоматики. - М.: Энергоатомиздат, 1988. 320 с.: ил, с.244-252: ГЛАВА 8. Схемы приема внешних сигналов.

8. Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник. - 2-е изд., перераб. и доп. 1990. 512 с.: ил. "С.116-122. 4.4. Принципы работы с согласованными линиями связи".

9. Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ-Петербург, 2001. - 528 с.: ил.

10. А.с. СССР 1495999, Н 03 М 5/12. Устройство для декодирования манчестерского кода. С.Н.Алмаев, Е.Б.Барановский и Э.П.Ващилин. - Опубл. 1989. Бюл. №27.

11. Патент РФ №2203520, Н 03 М 5/16. Устройство для приема и преобразования цифрового дифференциального сигнала. Киселев Е.Ф., Зуев А.И. - Опубл. 2003. БИ №12 (Прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ КОДОВОГО СИГНАЛА | 2007 |

|

RU2345479C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ АСИНХРОННОГО ЦИФРОВОГО СИГНАЛА | 2004 |

|

RU2279181C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 2005 |

|

RU2286007C1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 2005 |

|

RU2285333C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 2005 |

|

RU2280947C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

Изобретение относится к области вычислительной техники для приема дифференциального двухуровневого кодированного сигнала двоичного последовательного самосинхронизирующегося кода с преобразованием в двухразрядный цифровой сигнал и последующим помехоустойчивым выполнением полной функции синхронизации этого сигнала с помощью входной непрерывной последовательности тактовых импульсов. Технический результат заключается в повышении помехоустойчивости за счет помехоустойчивого формирования выходного синхронизированного сигнала и выходных синхросигналов битовой синхронизации, начала паузы и паузы с заградительной фильтрацией, синхронизации двухразрядного цифрового сигнала двухуровневого кода 1В2В как помехи при длительности каждого изменения этого сигнала, не превышающей пороговой длительности P·Tic для Р≥2, где Р - пороговое число, Tic - длительность периода тактовых импульсов. Устройство содержит приемник-преобразователь (6), входы (19, 20) первой и второй компонент дифференциального двухуровневого кодированного сигнала, триггеры (1-5), элементы И-НЕ (7, 8), И (21-24), ИЛИ (15-17), ИЛИ-НЕ (11-13), элементы Исключающее ИЛИ (9-10), асинхронный элемент задержки (14) и тактируемый элемент задержки (27), тактовый вход (18) и четыре выхода. 1 ил.

Устройство для приема и синхронизации двухуровневого кодированного сигнала, содержащее приемник-преобразователь, входы первой и второй компонент дифференциального двухуровневого кодированного сигнала, являющиеся первым и вторым входами приемника-преобразователя соответственно, первые элементы И-НЕ и И, три элемента ИЛИ, тактовый вход и четыре выхода, отличающееся тем, что оно дополнительно содержит пять триггеров, второй элемент И-НЕ, два элемента Исключающее ИЛИ, три элемента ИЛИ-НЕ, двухвходовый асинхронный элемент задержки сигнала на его выходе относительно изменения сигнала на одном из двух входов и неизменном единичном сигнале на другом входе этого элемента, второй, третий и четвертый элементы И, тактируемый элемент задержки с задержкой на число тактов, равное или большее единицы, выход синхронизированного сигнала приема бита кода, являющийся первым выходом устройства и прямым выходом первого триггера, выход синхросигнала битовой синхронизации, являющийся вторым выходом устройства, который соединен с тактовым входом первого триггера, первыми входами первых элементов ИЛИ-НЕ и ИЛИ и выходом второго элемента ИЛИ-НЕ, первый вход которого соединен с инверсным выходом второго триггера и асинхронным инверсным входом сброса тактируемого элемента задержки, информационный вход которого соединен с прямым выходом третьего триггера, а информационный выход соединен с информационным входом второго триггера, прямой выход которого соединен с первыми входами первого элемента И и второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом третьего элемента И и информационным входом четвертого триггера, инверсный выход которого соединен с входом сброса пятого триггера, информационный вход которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с прямым выходом пятого триггера и вторым входом третьего элемента И, выход которого является выходом синхросигнала начала паузы и третьим выходом устройства, выход первого элемента И соединен с первым входом третьего элемента ИЛИ, информационный вход и вход сброса третьего триггера соединены с выходом третьего элемента ИЛИ-НЕ, первый вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом первого элемента Исключающее ИЛИ и первым входом асинхронного элемента задержки, выход которого соединен с вторым входом четвертого элемента И, третий вход которого соединен с выходом второго элемента Исключающее ИЛИ и вторым входом асинхронного элемента задержки, четвертый выход устройства является выходом синхросигнала паузы, который соединен с прямым выходом четвертого триггера, вторыми входами третьего элемента ИЛИ-НЕ и второго элемента ИЛИ и первыми входами первого и второго элементов И-НЕ, выходы которых соединены соответственно с входами сброса и установки первого триггера, первый выход приемника-преобразователя является выходом прямого сигнала приема бита "1" двухуровневого кодированного сигнала и соединен с вторыми входами первых элементов И-НЕ и ИЛИ-НЕ и первыми входами первого элемента Исключающее ИЛИ и второго элемента Исключающее ИЛИ, второй вход которого соединен с информационным входом и инверсным выходом первого триггера, второй выход приемника преобразователя является выходом прямого сигнала приема бита "0" двухуровневого кодированного сигнала и соединен с вторыми входами второго элемента И-НЕ и первого элемента Исключающее ИЛИ и третьим входом первого элемента ИЛИ-НЕ, выход которого соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с вторыми входами второго элемента ИЛИ-НЕ и первого и второго элементов И, тактовый вход устройства соединен с тактовыми входами триггеров с второго по пятый и тактовым входом тактируемого элемента задержки, причем входы установки и сброса всех триггеров устройства являются асинхронными и инверсными и неиспользованные из них соединены с шиной Логической "1" устройства.

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| Устройство для декодирования манчестерского кода | 1987 |

|

SU1495999A1 |

| Устройство для декодирования манчестерского кода | 1988 |

|

SU1524181A1 |

| US 5748123 A, 05.05.1998 | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

Авторы

Даты

2006-12-27—Публикация

2005-05-27—Подача