Изобретение относится к импульсной цифровой технике, предназначено для выполнения с помощью входной непрерывной последовательности тактовых импульсов полной функции синхронизации входного одноразрядного или двухразрядного прямого или инверсного асинхронного цифрового сигнала (формирования одноразрядного синхронизированного сигнала и его синхросигнала) и может быть использовано при построении любых синхронных автоматов с памятью для ввода асинхронных команд или данных в двоичном последовательном самосинхронизирующемся коде (ДПСК), в частности может использоваться в качестве декодера трехуровневого кода RZ с возвратом к нулю по ГОСТ 18977-79 и РТМ 1495-75 или в качестве формирователя синхронизированного сигнала последовательного кода и его синхросигнала для любого двухуровневого ДПСК, например манчестерского по ГОСТ 26765.52-87 (зарубежные стандарты MIL-STD-1533B и MIL-STD-1773), биимпульсного или Миллера по ГОСТ 27232-87 и т.п.

Полная функция синхронизации входного одноразрядного IX или двухразрядного IX[1:0] асинхронного цифрового сигнала с помощью входной непрерывной последовательности тактовых импульсов IC с периодом следования TIC заключается в формировании выходного одноразрядного синхронизированного сигнала ОХ и его синхросигнала (синхронизирующего сигнала) OCX длительности ТОСХ=TIC при каждом изменении синхронизируемого сигнала IX или IX[1:0].

После приемника цифрового дифференциального сигнала любого из указанных выше ДПСК однозначно формируется его двухразрядный цифровой сигнал, который в прямом коде IX[1:0]=IX1 IX0 означает следующее:

возврат к нулю или пауза в коде RZ и пауза в любом другом ДПСК,

прием бита двоичного «0» в любом ДПСК,

прием бита двоичной «1» в любом ДПСК,

запрещенная комбинация в любом ДПСК, но возможная, кроме кода RZ, как переходная в течение нескольких TIC из-за гистерезисной характеристики приемника цифрового дифференциального сигнала при переключении с приема (2) или (3) на прием (3) или (2) соответственно.

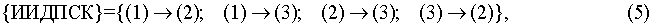

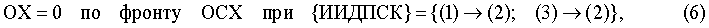

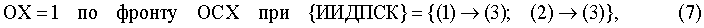

С учетом (1)÷(3) функция полной синхронизации асинхронного сигнала IX[1:0] заключается в формировании с помощью тактовых импульсов IC единичного синхросигнала OCX длительности ТОСХ=TIC при каждом информационном изменении ДПСК (ИИДПСК) сигнала IX[1:0], определяемого множеством

и запоминании синхронизированного сигнала ОХ по фронту OCX (переходу OCX из «0» в «1») согласно выражениям

при длительности ТОХ сигнала ОХ=0 (или ОХ=1), определяемой соотношением

где К - целое число не меньшее двух.

Из (1)÷(8) легко видеть, что в результате выполнения функции полной синхронизации асинхронного сигнала IX[1:0] любого ДПСК, описанного значениями (1)÷(4), формируется синхросигнал OCX длительности ТОСХ=TIC при каждом асинхронном информационном изменении сигнала IX[1:0] (содержится во множестве (5)) и синхронизированный по OCX битовый выходной сигнал ОХ=0 (или 1) длительности ТОХ (8), являющийся при приеме кода RZ последовательным двоичным кодом вводимой информации (т.е. функция полной синхронизации сигнала IX[1:0] кода RZ полностью эквивалентна операции декодирования этого кода в сигнал ОХ последовательного двоичного кода информации, каждый бит которой тактируется синхросигналом OCX битовой синхронизации), а при приеме любого другого ДПСК сигнал ОХ представляет синхронизированный по OCX одноразрядный ДПСК с исключением влияния на его формирование возможного кратковременного перехода IX[1:0] в запрещенное состояние (4).

Известно (см., например, [1, с.135-137], [2, с.119-120], [3, с.205-207]), что при построении любой цифровой системы (сложного асинхронного или синхронного автомата с памятью) постоянно возникает необходимость синхронизировать входные асинхронные сигналы системы с работой ее составных частей, функционирующих по тактовым импульсам единого системного тактового генератора. В этой связи в цифровой технике задача синхронизации асинхронных сигналов является традиционной, и известно большое число разнообразных устройств для синхронизации цифровых асинхронных сигналов по тактовым импульсам, например [1, с.135, рис.4.10б], [2, с.120, рис.3.19], [3, с.206, рис.6.26], [4, с.265, рис.14-3], [5] из технической литературы и [6]÷[29] по патентной информации, которые работают по входным тактовым импульсам IC и входному асинхронному сигналу IX.

Основным недостатком любого из указанных выше устройств синхронизации является ограниченность функциональных возможностей, поскольку каждое из них синхронизирует только одноразрядный асинхронный сигнал IX и явно не ориентировано на выполнение полной функции синхронизации сигнала IX для ввода данных в синхронный автомат с памятью.

Здесь следует отметить, что в асинхронной системе синхронизация (изменение состояния асинхронного автомата с памятью при установленных входных информационных сигналах) производится с помощью соответствующих синхроимпульсов (при формировании синхроимпульса с помощью IC его длительность совпадает с длительностью НТ нулевой (т.е. при IC=0) или длительностью ЕТ единичной (т.е. при IC=1) фазы периода TIC=НТ+ЕТ тактовых импульсов IC), а в синхронной системе синхронизация (изменение состояния синхронного автомата с памятью при установленных входных информационных сигналах) осуществляется логически по функции «И», т.е. по фронтам (переходам из «0» в «1») или срезам (переходам из «1» в «0») тактовых импульсов IC и соответствующим синхросигналам, установленным до прихода фронта или среза IC, причем длительность каждого синхросигнала обычно кратна числу периодов TIC.

Кроме того, в настоящее время и на длительную перспективу основным методом обработки информации в цифровых системах является синхронный метод тактирования по фронтам или срезам единого генератора тактовых импульсов с помощью синхросигналов - см., например [2, с.121-123: 3.5. Введение в проблематику и методику проектирования автоматом с памятью].

Отметим также, что после приема цифрового дифференциального сигнала ПДСК на выходе приемника двухразрядный цифровой сигнал может быть сформирован в прямом или инверсном коде (см., например, соответственно, технические решения [30] и [31] приемников цифровых дифференциальных сигналов ПДСК).

На основании изложенного выше можно сказать, что создание простого устройства для синхронизации асинхронного цифрового сигнала, реализующего полную функцию синхронизации одноразрядного IX или двухразрядного IX[1:0] прямого или инверсного асинхронного цифрового сигнала для ввода информации в синхронный автомат с памятью является актуальной технической проблемой.

Рассмотрим несколько известных простых технических решений устройств синхронизации, которые можно использовать для выполнения части полной функции синхронизации асинхронного сигнала IX, заключающейся в формировании с помощью тактовых импульсов IC синхросигнала OCX длительности ТОСХ=TIC по каждому изменению асинхронного сигнала IX и синхронизированного сигнала ОХ, длительность которого в общем случае можно определить выражением

где k - целое число не меньшее единицы.

Известно устройство [5], содержащее первый и второй триггеры, элемент И, входы сигнала IX и Логической «1», соединенные соответственно с тактовым и информационным входами первого триггера, выход синхросигнала ОС1, соединенный с выходом второго триггера, асинхронным входом сброса первого триггера и первым входом элемента И, тактовый вход сигнала IC, соединенный с вторым входом элемента И и тактовым входом второго триггера, информационный вход которого соединен с выходом сигнала Х1 первого триггера, и выход синхроимпульса ОС2=ОС1&IC, являющийся выходом элемента И, где «&» - оператор логической операции «И».

В исходном состоянии первый и второй триггеры находятся в состояниях Х1=0 и ОС1=0 соответственно. Из исходного состояния по каждому фронту сигнала IX первый триггер переключается в состояние Х1=1. При Х1=1 по ближайшему фронту IC второй триггер переключается в состояние ОС1=1, сбрасывает первый триггер в состояние Х1=0, разрешает элементу И формирование синхроимпульса ОС2=1 по IC=1, а по следующему фронту IC второй триггер сбрасывается в состояние ОС2=0 и возвращает устройство [5] в исходное состояние: Х1=0, ОС1=0.

Легко видеть, что по каждому фронту асинхронного сигнала IX устройство [5] формирует синхросигнал ОС1=1 в течение TIC и синхроимпульс ОС2=1 в течение ЕТ единичной фазы IC, причем ОС1 частично подобен синхросигналу OCX при выполнении функции полной синхронизации сигнала IX.

Основным недостатком устройства [5] является ограниченность его функциональных возможностей, поскольку оно предназначено для формирования синхроимпульсов ОС2 как командных, а синхросигнал ОСХ=ОС1 формируется в устройстве попутно только по фронту сигнала IX.

Известно устройство [21], содержащее три триггера, элемент И-НЕ, вход синхронизируемого сигнала IX, соединенный с входом сброса и информационным входом первого триггера, прямой выход которого соединен с информационным входом второго триггера, прямой выход которого соединен с первым входом элемента И-НЕ и информационным входом и входом сброса третьего триггера, тактовый вход, соединенный с тактовыми входами первого и второго триггеров и вторым входом элемента И-НЕ, и выход инверсного синхроимпульса NOZ, соединенный с выходом элемента И-НЕ и тактовым входом третьего триггера, инверсный выход которого соединен с третьим входом элемента И-НЕ, причем входы сброса первого и третьего триггеров являются асинхронными и инверсными.

Обозначив сигналы на выходах первого, второго и третьего триггеров соответственно через Х1, Х2 и NX3 (где NX3=!X3 - инверсное значение Х3), функционирование устройства [21] можно описать следующим образом.

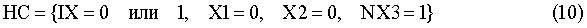

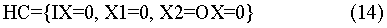

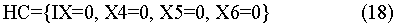

В зависимости от значения сигнала IX работу устройства [21] можно описать как последовательность переходов устройства из нулевого состояния (НС)

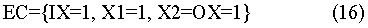

в единичное состояние (ЕС)

и наоборот из ЕС (10) в НС (11).

Переход из НС (10) в ЕС (11) инициируется переключением IX из «0» в «1», и при IX=1 по ближайшему фронту тактового сигнала IC первый триггер устанавливается в Х1=1 и дальнейшее функционирование устройства [21] определяется одним из двух случаев поведения сигнала IX в течение текущего периода TIC.

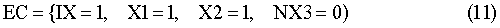

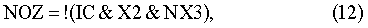

В первом случае при IX=1 по следующему фронту сигнала IC второй триггер устанавливается в Х2=1, и по следующему значению IC=1, независимо от значения IX, элемент И-НЕ генерирует выходной синхроимпульс NOZ=!IC=0 согласно логическому выражению

где «!=N» и «&» - операторы логических операций соответственно «НЕ» и «И» на языке ABEL.

По фронту сигнала NOZ=0 третий триггер устанавливается (формирует сигнал NX3=0), и устройство переходит в ЕС (11), в котором сигналом NX3=0 запрещена работа элемента И-НЕ по третьему входу.

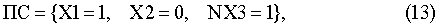

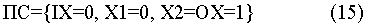

Во втором случае, если сигнал IX переключится из «1» в «0» и асинхронно сбросит первый триггер в течение текущего периода TIC (т.е. до первого фронта IC после установки Х1=1), то устройство [21] из промежуточного состояния (ПС)

асинхронно перейдет в НС (10) и проигнорирует как помеху изменение сигнала IX(t) во времени IX(t)=0→1→0 при IX(t)=1 в течение ЕТХ≤TIC.

Переход из ЕС (11) в НС (10) происходит по переключению IX из «1» в «0» так, что по IX=0 первый триггер асинхронно сбрасывается в Х1=0. При Х1=0 по ближайшему фронту тактового сигнала IC второй триггер переключается в Х2=0, асинхронно сбрасывает третий триггер в NX3=1 и устройство переходит в НС (10).

Таким образом, устройство [21] по каждому фронту изменения асинхронного сигнала IX(t)=0→1→0 при IX(t)=1 в течение ЕТХ>TIC генерирует выходной импульс NOZ (13) и в процессе перехода по графу НС (10)→ЕС (11)→НС (10) попутно формирует синхронизированный сигнал Х2=ОХ при условии (9).

Основным недостатком устройства [21] является ограниченность его функциональных возможностей (устройство синхросигнал OCX не формирует, а синхронизированный сигнал ОХ=Х2 вырабатывает попутно), поскольку оно предназначено для помехоустойчивого формирования синхроимпульса NOZ (13) с игнорированием как помех импульсов IX(t)=1 при длительности ЕТХ<TIC.

Известно устройство [28], содержащее два триггера, вход синхронизируемого сигнала IX, соединенный с входом установки первого триггера, тактовый вход сигнала IC, являющийся тактовым входом второго триггера, информационный вход которого соединен с выходом первого триггера, и выход синхронизированного сигнала ОХ, соединенный с выходом второго триггера и входом сброса первого триггера, который является асинхронным RS триггером с приоритетным входом установки S, т.е. при IX=1 первый триггер фиксируется в состоянии Х1=1 независимо от состояния второго триггера, сигнал которого Х2=ОХ действует на входе сброса R первого триггера, сброс которого при IX=0 осуществляется по Х2=ОХ=1.

В зависимости от значений длительностей НТХ и ЕТХ, значений сигнала IX соответственно при IX=0 и IX=1 работу устройства [28] можно описать как последовательность переходов из нулевого состояния (НС)

в промежуточное состояние (ПС)

или в единичное состояние (ЕС)

и наоборот из ПС (15) в НС (14), или из ЕС (16) в ПС (15), а затем в НС (14).

Первый триггер устройства [28] по сигналам IX и ОХ=Х2 функционирует так, что по каждому переходу IX из «0» в «1» он асинхронно устанавливается в Х1=1 за время Ts независимо от значения сигнала ОХ=Х2, а при Х1=1, Х2=1 и IX=1 этот триггер по каждому переходу IX из «1» в «0» асинхронно сбрасывается в X1=0 за время Tr≈Ts≪TIC, где Ts (или Tr) - минимальная длительность ЕТХ (или НТХ) сигнала IX=1 (или IX=0), необходимая для установки (или сброса) первого триггера в X1=1 (или X1=0).

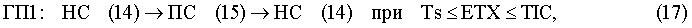

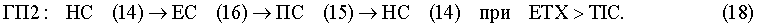

С учетом сказанного выше работу устройства [28] можно описать как цепочку переходов из одного состояния в другое в виде последовательности или чередования двух следующих графов переходов (ГП1) и (ГП2):

В первом случае (17) переход устройства из НС (14) в ПС (15) осуществляется переключением IX из «0» в «1» так, что первый триггер устанавливается в Х1=1 через время Ts. При Х1=1 по ближайшему фронту тактового сигнала IC второй триггер устанавливается в Х2=ОХ=1. Далее при переключении IX из «1» в «0» по Х2=ОХ=1 первый триггер через время Tr асинхронно сбрасывается в Х1=0 и устройство оказывается в ПС (15), из которого по следующему фронту сигнала IC оно переходит в НС (14).

Во втором случае (18) переход устройства из НС (14) в ЕС (15) осуществляется переключением IX из «0» в «1» так, что первый триггер устанавливается в Х1=1 через время Ts. При Х1=1 по ближайшему фронту тактового сигнала IC второй триггер устанавливается в Х2=ОХ=1, и при IX=1 устройство оказывается в ЕС (16). Далее по переключению IX из «1» в «0» через время Tr первый триггер асинхронно сбрасывается в Х1=0, и устройство оказывается в ПС (15), из которого по следующему фронту сигнала IC оно переходит в НС (14).

Таким образом, особенностью функционирования устройства [28] является то, что оно отрабатывает (ловит) короткие импульсы IX=1 при функционировании согласно ГП1 (17).

Интересно отметить, что при Ts≤ЕТХ<TIC специфика устройства [28] практически противоположна специфике устройства [21].

Основным недостатком устройства [28] является ограниченность его функциональных возможностей (оно синхросигнал OCX не формирует), поскольку предназначено для формирования синхронизированного сигнала ОХ=Х2 с обеспечением условий синхронизации сигнала IX(t) при длительности ЕТХ, удовлетворяющей ограничению Ts≤EJX.

На основе рассмотренных выше простейших устройств [5] и [21] (или [28]) можно построить устройство с функцией предлагаемого. Однако такое техническое решение будет сложным (иметь большое число элементов и связей между ними), что обусловлено узкой специализацией его составных частей.

Из известных технических решений наиболее близким к предлагаемому по сложности и количеству выходов является устройство [24], содержащее элемент НЕ, два элемента И-НЕ, три триггера, два элемента И-И-ИЛИ, сигнальный вход синхронизируемого сигнала IX, соединенный с первым входом первого элемента И-НЕ и связанный через элемент НЕ с первым входом второго элемента И-НЕ, выход которого соединен с асинхронным инверсным входом сброса первого триггера, асинхронный инверсный вход установки которого соединен с выходом первого элемента И-НЕ, тактовый вход тактовых импульсов IC, соединенный с тактовыми входами второго и третьего триггеров, первый выход синхроимпульса ОС1, являющийся выходом первого элемента И-И-ИЛИ, первые входы элементов И которого соединены с прямым выходом первого триггера и информационными входами второго и третьего триггеров, и второй выход синхроимпульса ОС2, являющийся выходом второго элемента И-И-ИЛИ, первые входы которых соединены с инверсным выходом первого триггера, инверсный выход второго триггера соединен с вторым входом первого элемента И-НЕ и вторыми входами первых элементов И обоих элементов И-И-ИЛИ, третьи входы первых элементов И которых соединены с вторым входом второго элемента И-НЕ и прямым выходом третьего триггера, инверсный выход которого соединен с третьим входом первого элемента И-НЕ и вторыми входами вторых элементов И обоих элементов И-И-ИЛИ, третьи входы вторых элементов И которых соединены с третьим входом второго элемента И-НЕ и прямым выходом второго триггера.

В процессе функционирования устройства [24] второй триггер переключается по фронту сигнала IC (переходу из «0» в «1»), а третий триггер переключается по срезу сигнала IC (переходу из «0» в «1»).

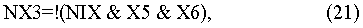

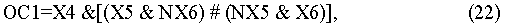

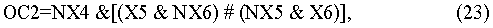

Обозначим через NX1, NX2 и NX3 инверсные сигналы, формируемые соответственно на выходах элемента НЕ, первого и второго элементов И-НЕ; Х4, Х5, Х6 и NX4=!X4, NX5=!X5, NX6=!X6 прямые и инверсные сигналы, формируемые первым (Х4 и NX4), вторым (Х5 и NX5) и третьим (Х6 и NX6) триггерами соответственно.

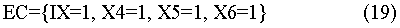

С использованием принятых обозначений функционирование устройства [24] в процессе перехода из нулевого состояния (НС)

в единичное состояние (ЕС)

и наоборот из ЕС (19) в НС (18) можно описать с помощью следующих логических выражений

где «!=N», «&» и «#» - в языке ABEL операторы операций НЕ, И и ИЛИ соответственно.

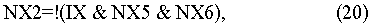

В установившемся НС (18) (или ЕС (19)) сигналы NX2=NX3=1, а переход в другое состояние инициируется переключением сигнала IX в состояние IX=1 (или IX=0), при котором первый (или второй) элемент И-НЕ согласно (20) (или (21)) формирует сигнал NX2=0 (или NX3=0), устанавливающий (или сбрасывающий) первый триггер в состояние Х4=1 (или Х4=0). Далее при Х4=1 (или Х4=0) по первому ближайшему фронту или срезу сигнала IC устанавливается (или сбрасывается) соответственно третий или четвертый триггер и согласно (22) (или (23)) формируется синхроимпульс ОС1=1 (или ОС2=1), который заканчивается установкой (или сбросом) третьего или четвертого триггера по очередному фронту или срезу сигнала IC, чем и отмечается при IX=1 (или IX=0) переход устройства в состояние ЕС (19) (или НС (18)).

Таким образом, каждый переход устройства [24] из НС (18) (или ЕС (19)) в ЕС (19) (или НС (18)) отмечается формированием единичного выходного синхроимпульса ОС1 (22) (или ОС2 (23)), длительность которого определяется временным расстоянием ЕТ между ближайшими фронтом и срезом или НТ между ближайшим срезом и фронтом входной непрерывной последовательности тактовых импульсов IC. Кроме того, второй триггер попутно формирует синхронизированный сигнал Х5=ОХ полной функции синхронизации входного асинхронного сигнала IX.

С точки зрения применения для построения систем с синхронным принципом работы основным недостатком устройства [24] является то, что оно при значительной сложности имеет ограниченные функциональные возможности (например, синхросигнал OCX не формируется, на временной оси синхроимпульс ОС1 или ОС2 вырабатывается в течение НТ при IC=0 или в течение ЕТ при IC=1, и отсутствует возможность выполнения полной функции синхронизации двухразрядного асинхронного сигнала IX[1:0]), что обусловлено формированием выходных синхроимпульсов ОС1 (22) и ОС2 (23) как командных для управления системой с асинхронным принципом работы, например, в качестве старт и стоп импульсов в измерителе длительности асинхронного сигнала IX=1.

Предлагаемым изобретением решается задача комплексного расширения функциональных возможностей устройства без увеличения его сложности (без увеличения как количества элементов в устройстве, так и общего количества связей между его элементами) за счет формирования в устройстве синхронизированного сигнала и его синхросигнала для прямого или инверсного одноразрядного или двухразрядного входного асинхронного цифрового сигнала путем соответствующего подключения его с помощью трех сигнальных входов, два из которых введены для этого дополнительно.

Для достижения этого технического результата в устройство для синхронизации асинхронного цифрового сигнала, содержащее три триггера, элемент НЕ, тактовый вход, два выхода и первый сигнальный вход, дополнительно введены четвертый триггер, элемент ИЛИ, два элемента Исключающее ИЛИ, второй и третий сигнальные входы и вход сигнала Логической «1», соединенный с входами сброса и установки первого и второго триггеров и с входами установки и информационными входами третьего и четвертого триггеров, тактовый вход устройства является тактовым входом первого триггера, первый выход устройства является выходом синхросигнала устройства и выходом первого триггера, который соединен с тактовым входом второго триггера и через элемент НЕ связан с входами сброса третьего и четвертого триггеров, тактовые входы которых соединены соответственно с выходами первого и второго элементов Исключающее ИЛИ, первые входы которых соединены с первым и вторым сигнальными входами устройства соответственно, третий сигнальный вход устройства соединен со вторыми входами обоих элементов Исключающее ИЛИ, второй выход устройства является выходом синхронизированного сигнала устройства и выходом второго триггера, информационный вход которого соединен с выходом третьего триггера и первым входом элемента ИЛИ, выход четвертого триггера соединен с вторым входом элемента ИЛИ, выход которого соединен с информационным входом первого триггера, причем все триггеры одинаковы, их входы сброса и установки являются асинхронными и инверсными и каждый из них срабатывает по фронту сигнала на его тактовом входе.

Автору не известны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение четвертого триггера, элемента ИЛИ, двух элементов Исключающее ИЛИ, входа Логической «1» и второго и третьего сигнальных входов) предлагаемого устройства, которые (по сравнению с прототипом [24]) без увеличения сложности устройства комплексно расширяют его функциональные возможности за счет обеспечения формирования устройством синхронизированного сигнала и его синхросигнала для прямого или инверсного одноразрядного или двухразрядного входного асинхронного цифрового сигнала путем соответствующего подключения его с помощью трех сигнальных входов.

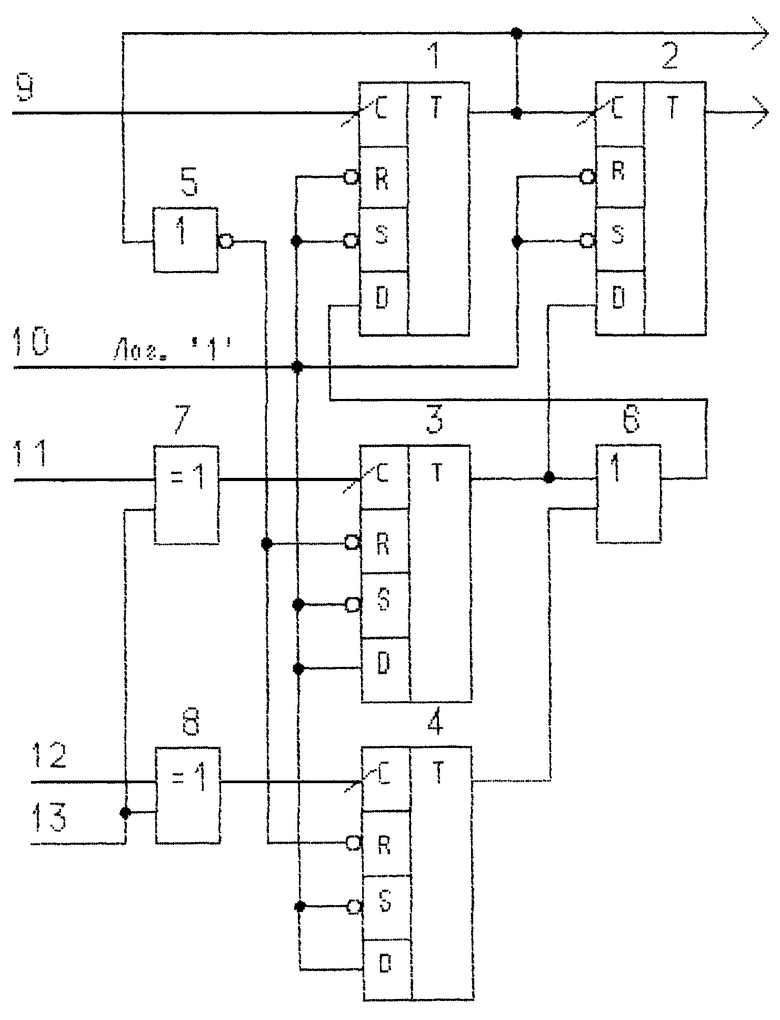

На чертеже приведена функциональная электрическая схема устройства для синхронизации асинхронного цифрового сигнала, содержащего триггеры с первого 1 по четвертый 4, элемент 5 НЕ, элемент 6 ИЛИ, первый 7 и второй 8 элементы Исключающее ИЛИ, тактовый вход 9, являющийся тактовым входом первого триггера 1, вход 10 сигнала Логической «1», соединенный с входами сброса и установки первого 1 и второго 2 триггеров и с входами установки и информационными входами третьего 3 и четвертого 4 триггеров, первый 11 и второй 12 сигнальные входы, соединенные с первыми входами первого 7 и второго 8 элементов Исключающее ИЛИ соответственно, третий сигнальный вход 13, соединенный со вторыми входами первого 7 и второго 8 элементов Исключающее ИЛИ, выходы которых соединены с тактовыми входами третьего 3 и четвертого 4 триггеров соответственно, выход синхросигнала, соединенный с выходом первого триггера 1 и тактовым входом второго триггера 2 и связанный через элемент 5 НЕ с входами сброса третьего 3 и четвертого 4 триггеров, и выход синхронизированного сигнала, являющийся выходом второго триггера 2, информационный вход которого соединен с первым входом элемента 6 ИЛИ и выходом третьего триггера 3, выход четвертого триггера 4 соединен с вторым входом элемента 6 ИЛИ, выход которого соединен с информационным входом первого триггера 1, причем входы сброса и установки триггеров 1÷4 являются асинхронными и инверсными и каждый из триггеров 1÷4 срабатывает по фронту сигнала на его тактовом входе.

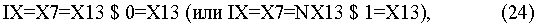

Обозначим через Х1÷Х4 значения сигналов на выходах триггеров 1÷4 при Х1=ОСХ, Х2=ОХ, NX5=!X1 - инверсное значение сигнала на выходе элемента 5, Х6÷Х8 значения сигналов на выходах элементов 6÷8 и Х11÷Х13 прямые (или NX11÷NX13 инверсные) значения сигналов на входах 11÷13.

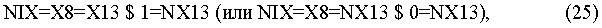

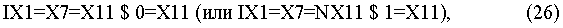

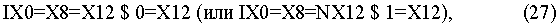

В зависимости от спецификации сигналов на входах 11÷13 предлагаемое устройство можно использовать для преобразования в выходной синхронизированный сигнал ОХ=Х2 и его синхросигнал ОСХ=Х1 асинхронного одноразрядного прямого Х13 при Х11=0, Х12=1 (или инверсного NX13 при Х11=1, Х12=0) сигнала за счет функционирования элементов 7 и 8 согласно выражений

или асинхронного двухразрядного прямого IX[1:0]=IX1 IX0=Х11 Х12 при Х13=0 (или инверсного NIX[1:0]=NIX1 NIX0=NX11 NX12 при Х13=1) сигнала за счет функционирования элементов 7 и 8 согласно выражений

где $ - оператор операции Исключающее ИЛИ на языке ABEL;

IX=X7 и NIX=!IX=X8 - соответственно прямое и инверсное значения асинхронного одноразрядного синхронизируемого прямого сигнала Х13 при Х11=0, Х12=1 (или инверсного сигнала NX13 при Х11=1, Х12=0);

IX[1:0]=Х7 Х8 - асинхронный двухразрядный сигнал, определенный двухразрядным прямым

IX[1:0]=Х11 Х12 при Х13=0

или инверсным

NIX[1:0]=NX11 NХ12 при Х13=1

синхронизируемым сигналом.

Формально функция полной синхронизации асинхронного сигнала

Х7Х8=IX1 IXO=IX[1:0]

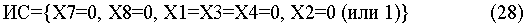

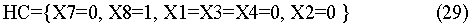

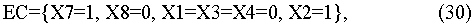

для трехуровневого кода RZ или любого двухуровневого ДПСК полностью определена с помощью выражений (1)÷(8) с учетом запрещенной комбинации (4), а данное устройство реализует эту функцию в процессе перехода из исходного состояния (ИС)

в нулевое состояние (НС)

или в единичное состояние (ЕС)

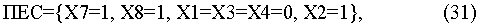

а из НС (29) (или ЕС (30)) в ИС (28), или из (НС) (29) в переходное единичное состояние (ПЕС)

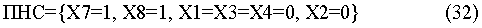

с последующим асинхронным переходом в ЕС (30), или из ЕС (30) в переходное нулевое состояние (ПНС)

с последующим асинхронным переходом в НС (29).

С учетом изложенного опишем функционирование устройства при синхронизации сигнала Х7 Х8=IX[1:0]=IX1 IX0 (определен соотношениями (1)÷(4)) сначала для трехуровневого кода RZ с возвратом к нулю, а затем для любого двухуровневого ДПСК (манчестерского, Миллера и т.п.), в котором будет содержаться практически и описание синхронизации одноразрядного сигнала при Х7=Х и Х8=NIX.

В коде RZ в каждом битовом интервале Т=Т1+Т2 приема ПДСК при Т1=Т2=Т/2 в активной части информационного полупериода Т1 код IX[1:0]=Х7Х8=01 при приеме «0» (или код IX[1:0]=Х7Х8=10 при приеме «1»), а в течение полупериода Т2 возврата к нулю или в течение паузы Тп=(4÷40)Т код IX[1:0]=Х7Х8=00 и устройство находится в ИС (28).

Из ИС (28) при приеме в коде RZ бита «1» (или «0») сигнал IX1=Х7 (или IX0=Х8) переключается на время Т1 в «1» и фронтом устанавливает триггер 3 (или 4) в Х3=1 (или Х4=1), элемент 6 ИЛИ формирует сигнал Х6=(Х3#Х4)=1, по которому триггер 1 по ближайшему фронту тактовых импульсов Х9=IC устанавливается в Х1=ОСХ=1 и фронтом записывает в триггер 2 значение Х3=1 (или Х3=0), совпадающее с принимаемым в коде RZ битом «1» (или «0»). После этого триггер 3 (или 4) по сигналу NX5=!X1=0 сбрасывается в «0», элемент 6 ИЛИ выставляет сигнал Х6=0, и по следующему фронту Х9 триггер 1 сбрасывается в Х1=0, и устройство переходит в ЕС (30) (или НС (29). Далее по истечении времени Т1 сигнал Х7 (или Х8) переключается в «0» и устройство возвращается в ИС (28). Легко видеть, что каждый раз при приеме в коде RZ бита «1» или «0» устройство формирует синхросигнал Х1=ОСХ длительности ТОСХ=TIC, по фронту которого в триггер 2 записывается «1» или «0», т.е. триггер 2 формирует синхронизированный сигнал Х2=ОХ, представляющий собой последовательный двоичный код (ПДК) принимаемой в коде RZ информации.

Таким образом, при обработке асинхронного цифрового сигнала IX[1:0]=Х7Х8 кода RZ предлагаемое устройство является декодером этого кода, так как синхронизированный сигнал Х2=ОХ представляет собой ПДК, каждый бит которого сопровождается синхросигналом Х1=ОСХ битовой синхронизации.

В процессе обработки сигнала IX[1:0]=Х7 Х8 любого двухуровневого ПДСК устройство может находиться в любом из пяти состояний (28)-(32), причем ИС (28) является паузой в передаче информации.

Если устройство находится в ИС (28), то в начале передачи устанавливается в «1» Х8 (или Х7) перевода устройства в НС (29) (или ЕС (30)) так, что по фронту Х8=1 (или Х7=1) триггер 4 (или 3) устанавливается в Х4=1 (или Х3=1), элемент 6 ИЛИ формирует сигнал Х6=1, и по ближайшему фронту тактового сигнала Х9 триггер 1 устанавливается в Х1=1, а по фронту Х1=1 триггер 2 переключается в Х2=0 (или Х2=1). После переключения триггера 2 по сигналу Х5=!Х1=0 триггер 4 (или 3) сбрасывается в Х4=0 (или Х3=0), элемент 6 ИЛИ формирует сигнал Х6=0, и по следующему фронту Х9 триггер 1 сбрасывается в Х1=0, и устройство оказывается в НС (29) (или ЕС (30)). Далее при наличии информации устройство будет непрерывно переходить из НС (29) по фронту сигнала Х7=1 в ПЕС (31) с последующим асинхронным переходом в ЕС (30) по срезу сигнала Х8=0 и, наоборот, по фронту сигнала Х8=1 в ПНС (29) с последующим асинхронным переходом в НС (29) по срезу сигнала Х7=0. В процессе каждого такого перехода формируется синхросигнал Х1=ОСХ, по фронту которого в триггер 2 заносится новое значение Х3, которое противоположно предыдущему состоянию триггера 2.

Таким образом, при обработке асинхронного цифрового сигнала IX[1:0]=Х7 Х8 любого двухуровневого ПДСК предлагаемое устройство является формирователем синхронизированного сигнала этого кода, так как синхронизированный сигнал Х2=ОХ представляет собой сам ПДСК, каждое изменение которого тактируется синхросигналом Х1=ОСХ.

Функционирование устройства в процессе синхронизации одноразрядного сигнала при Х7=IX и X8=NIX заключается в переходе устройства из НС (29) в ЕС (30) по переключению сигнала Х7 из «0» в «1» с исключением перехода в ПЕС (31) (т.е. с одновременным переключением сигнала Х8 из «1» в «0») и, наоборот, в переходе устройства из ЕС (30) в НС (29) по переключении сигнала Х8 из «0» в «1» с исключением перехода в ПНС (32) (т.е. с одновременным переключением сигнала Х7 из «0» в «1»).

В последнем случае выполняемая данным устройством функция (формирование Х1=ОСХ и Х2=ОХ по изменениям сигнала IX), при удвоенной частоте тактовых импульсов IC (по сравнению с прототипом [24]), эквивалентна функции формирования в прототипе выходного синхроимпульса ОС1 (22) (или ОС2 (23)) по фронту (или срезу) сигнала IX, поскольку по аргументам OCX и ОХ в синхронном автомате с памятью для ввода соответствующей команды легко сформировать синхросигнал (ОСХ&ОХ) (или ОСХ&(!ОХ)), который по быстродействию и функции аналогичен ОС1 (22) (или ОС2 (23)).

Сравнение предлагаемого устройства с прототипом [24] показывает, что по аппаратурным затратам они практически эквивалентны (содержат по восемь элементов), но количество связей в предлагаемом устройстве меньше, поскольку все триггеры одинаковы, каждый из них имеет только прямой выход, логические элементы имеют не более двух входов, а в прототипе все триггеры различны и используются многовходовые элементы: каждый из двух элементов И-НЕ и И-И-ИЛИ имеет по три и шесть входов соответственно.

Непосредственно из описания прототипа [24] и данного устройства для синхронизации асинхронного цифрового сигнала следует, что по сравнению с прототипом предлагаемое устройство благодаря его существенным признакам не сложнее прототипа, но по сравнению с ним обладает значительно расширенными функциональными возможностями за счет обеспечения формирования на выходах устройства синхронизированного сигнала и его синхросигнала для прямого или инверсного одноразрядного или двухразрядного входного асинхронного цифрового сигнала путем соответствующего подключения его с помощью трех сигнальных входов.

Благодаря существенным признакам предлагаемое устройство может быть использовано при построении любых синхронных автоматов с памятью для ввода асинхронных команд или данных в ряде ДПСК, в частности может использоваться в качестве декодера трехуровневого кода RZ с возвратом к нулю или в качестве формирователя синхронизированного сигнала последовательного кода ОХ=Х2 и его синхросигнала ОСХ=Х1 для любого двухуровневого ДПСК, например манчестерского, Миллера и т.п.

Литература

1. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. - М.: Мир, 2001. 379 с. ил.

2. Угрюмов Е.П. Цифровая схемотехника. СПб.: БХВ-Петербург, 2001. 528 с. ил.

3. Бойко Е.П. и др. Схемотехника электронных систем. Цифровые устройства. - СПб.: БХВ-Петербург, 2004. 512 с. ил.

4. Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной технике. - Л.: Энергоатомиздат. Ленингр. отд-ние. 1986. 280 с.: ил. «Импульсные устройства на микросхемах», с.202-276.

5. Гутников B.C. Интегральная электроника в измерительных устройствах. 1988. 304 с.: ил. (С.177, Рис.6.8. Схема устройства синхронизации).

6. А.с. СССР 544114, Н 03 К 5/13. Устройство для синхронизации импульсов В.И.Ильин и Г.Л.Силин. Опубл. 1977. БИ №3.

7. А.с. СССР 552687, Н 03 К 5/13. Формирователь одиночных импульсов, синхронизированных тактовой частотой. Г.Л.Силин, В.И.Ильин, С.М.Пахомов и ГА.Зуев. Опубл. 1977. БИ №12.

8. А.с. СССР 645249, Н 03 К 5/01. Устройство для выделения импульса из непрерывной импульсной последовательности. И.Л.Абросимов. - Опубл. 1979. БИ№4.

9. А.с. СССР 661753, Н 03 К 5/153. Устройство для синхронизации импульсов. А.С.Чередниченко, Е.А.Евсеев и А.Н.Горбунов. Опубл. 1979. БИ №17.

10. А.с. СССР 680160, Н 03 К 5/13. Устройство для синхронизации импульсов. В.И.Ильин, Л.П.Князева и ГЛ.Силин. Опубл. 1979. БИ №30.

11. А.с. СССР 716144, Н 03 К 5/13, Н 03 К 5/01. Синхронизирующее устройство. Е.В.Стриженов и Т.В.Алтунов. Опубл. 1980. Бюл. №6.

12. А.с. СССР 703900, Н 03 К 5/13. Устройство синхронизации. Н.А.Кукин. Опубл. 1979. БИ №46.

13. А.с. СССР 739721, Н 03 К 5/13. Устройство для синхронизации импульсов Н.Н.Макаров и М.Я.Эйнгорин. Опубл. 1980. БИ №21.

14. А.с. СССР 741440, Н 03 К 5/13. Устройство для синхронизации импульсов. В.Э.Вершков и М.П.Шервуд. Опубл. 1980. БИ №22.

15. А.с. СССР 744947, Н 03 К 5/13. Устройство для синхронизации импульсов. Л.Н.Герасимов, Л.Т.Сапега и Д.В.Ползунова. Опубл. 1980. БИ №24.

16. А.с. СССР 754661, Н 03 К 5/13. Устройство синхронизации. Ф.С.Власов, А.Т.Еремин, В.И.Позамантир и О.А.Райков. Опубл. 1980. БИ №29.

17. А.с. СССР 790209, Н 03 К 5/13. Формирователь импульсов. А.С.Чередниченко, В.А.Евсеев и А.Н.Горбунов и Ю.А.Плужников. Опубл. 1980. БИ №47.

18. А.с СССР 790212, Н 03 К 5/13. Устройство синхронизации импульсов. С.В.Смирнов и В.В.Скрябин. Опубл. 1980. БИ №47.

19. А.с. СССР 864528, Н 03 К 5/13. Устройство синхронизации импульсов. С.В.Смирнов и М.П.Смирнова. Опубл. 1981. БИ №34.

20. А.с. СССР 864529, Н 03 К 5/13. Формирователь одиночных импульсов, синхронизированных тактовой частотой. П.П.Никонович, Б.П.Царев и ГА. Хайтин. Опубл. 1981. БИ №34.

21. А.с. СССР 898601, Н 03 К 5/05. Устройство тактовой синхронизации. / М.М.Бекеша, Н.Н.Фролов и В.А.Фокин. Опубл. 1982. БИ №2.

22. А.с. СССР 930614, Н 03 К 5/00. Устройство для синхронизации импульсов. Н.С.Бибик, А.Г.Касьянов, П.П.Никонович и Л.Я.Портянко. Опубл. 1982. БИ №19.

23. А.с. СССР 1018215, Н 03 К 5/135, Формирователь импульсов. Н.А.Бадыштов, А.А.Сорокин, Г.Н.Шестаков и Е.Н.Старостенкова. Опубл. 1983. БИ №18.

24. А.с. СССР 1019610, Н 03 К 5/13. Устройство для формирования синхронизированных импульсов. С.В.Смирнов, Ф.Г.Киндиренко и А.Ф.Толочко. Опубл. 1983. БИ №19 (Прототип).

25. А.с. СССР 1050102, Н 03 К 5/01. Формирователь импульсов. В.В.Скрябин и С.В.Смирнов. 1983. БИ №39.

26. А.с. СССР 1061254, Н 03 К 5/01. Устройство для выделения одиночного импульса. Я.В.Коханый. Опубл. 1983. БИ №46.

27. А.с. СССР 1144187, Н 03 К 5/01. Устройство для выделения одиночного импульса. И.А.Рогачевский, Б.М.Сирота и А.В.Шинкаренко. Опубл. 1985. БИ №9.

28. А.с. СССР 1145471, Н 03 К 5/135. Устройство тактовой синхронизации. А.Л.Ратанов и Д.М.Манкевич. Опубл. 1985. БИ №10.

29. А.с. СССР 1160550, Н 03 К 5/135. Формирователь одиночного импульса. Г.Ю.Козодаев и С.К.Харин. 1985. БИ №21.

30. Патент РФ на изобретение 2190927, Н 03 К 17/16, G 06 F 13/00, 3/00. Коммутатор цифровых дифференциальных сигналов. Киселев Е.Ф., Зуев А.И. Опубл. 2002. БИ №28.

31. Патент РФ на изобретение 2203520, Н 03 М 5/16. Устройство для приема и преобразования цифрового дифференциального сигнала. Киселев Е.Ф., Зуев А.И. Опубл. 2003. БИ №12.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 2005 |

|

RU2280947C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 2005 |

|

RU2285333C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ КОДОВОГО СИГНАЛА | 2007 |

|

RU2345479C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ ЦИФРОВОГО СИГНАЛА | 2005 |

|

RU2286007C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ ДВУХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2005 |

|

RU2290755C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| Фазовый синхронизатор | 1987 |

|

SU1443147A1 |

Устройство для синхронизации асинхронного цифрового сигнала относится к импульсной цифровой технике, предназначено для выполнения с помощью входной непрерывной последовательности тактовых импульсов полной функции синхронизации входного одноразрядного или двухразрядного прямого или инверсного входного асинхронного цифрового сигнала (формирования одноразрядного синхронизированного сигнала и его синхросигнала) и может быть использовано при построении любых синхронных автоматов с памятью для ввода асинхронных команд или данных в двоичном последовательном самосинхронизирующемся коде (ДПСК), в частности может использоваться в качестве декодера трехуровневого кода RZ с возвратом к нулю или в качестве формирователя синхронизированного сигнала последовательного кода и его синхросигнала для любого двухуровневого ДПСК, например манчестерского, Миллера и т.п. Технический результат - комплексное расширение функциональных возможностей устройства за счет формирования на выходах устройства синхронизированного сигнала и его синхросигнала для прямого или инверсного одноразрядного или двухразрядного входного асинхронного цифрового сигнала путем соответствующего подключения его с помощью трех сигнальных входов. Устройство содержит три триггера, элемент НЕ, тактовый вход, первый сигнальный вход и два выхода, а также дополнительно содержит четвертый триггер, элемент ИЛИ, два элемента Исключающее ИЛИ, второй и третий сигнальные входы и вход сигнала Логической "1", причем первый выход устройства является выходом синхросигнала и соединен с выходом первого триггера и тактовым входом второго триггера, выход которого является выходом синхронизированного сигнала и вторым выходом устройства. 1 ил.

Устройство для синхронизации асинхронного цифрового сигнала, содержащее три триггера, элемент НЕ, тактовый вход, два выхода и первый сигнальный вход, отличающееся тем, что оно дополнительно содержит четвертый триггер, элемент ИЛИ, два элемента Исключающее ИЛИ, второй и третий сигнальные входы и вход сигнала Логической "1", соединенный с входами сброса и установки первого и второго триггеров и входами установки и информационными входами третьего и четвертого триггеров, тактовый вход первого триггера является тактовым входом устройства, первый выход которого является выходом синхросигнала и выходом первого триггера, соединенного с тактовым входом второго триггера и связанного через элемент НЕ с входами сброса третьего и четвертого триггеров, тактовые входы которых соответственно соединены с выходами первого и второго элементов Исключающее ИЛИ, первые входы которых соединены с первым и вторым сигнальными входами устройства соответственно, третий сигнальный вход устройства соединен со вторыми входами обоих элементов Исключающее ИЛИ, второй выход устройства является выходом синхронизированного сигнала и выходом второго триггера, информационный вход которого соединен с выходом третьего триггера и первым входом элемента ИЛИ, выход четвертого триггера соединен со вторым входом элемента ИЛИ, выход которого соединен с информационным входом первого триггера, причем все триггеры одинаковы, и их входы сброса и установки являются асинхронными и инверсными.

| Устройство для формирования синхронизированных импульсов | 1981 |

|

SU1019610A1 |

| Формирователь одиночного импульса | 1983 |

|

SU1160550A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| Устройство для выделения одиночного импульса | 1983 |

|

SU1144187A1 |

| Устройство для синхронизации импульсов | 1979 |

|

SU864528A1 |

| Формирователь одиночных импульсов,синхронизированных тактовой частотой | 1979 |

|

SU864529A2 |

| КРЫЛО МАХОЛЕТА И СПОСОБ УПРАВЛЕНИЯ ДВИЖЕНИЕМ КРЫЛА | 1998 |

|

RU2162428C2 |

Авторы

Даты

2006-06-27—Публикация

2004-12-28—Подача