Изобретение относится к вычислительной технике и автоматике и может быть использовано, в частности, при обработке сигналов частотных датчиков и программировании запоминающих устройств.

Цель изобретения - расширение функциональных возможностей умножителя за счет обеспечения возможности изменения длительности выходных импульсов путем регулировки длительности входных сигналов.

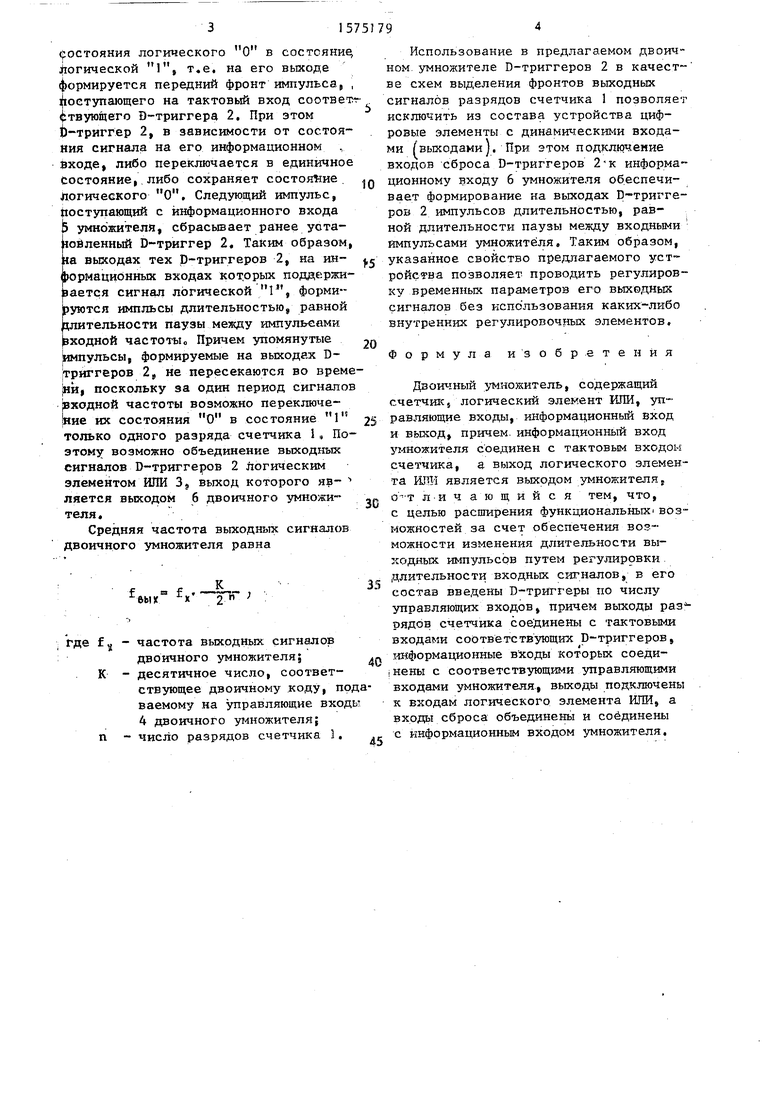

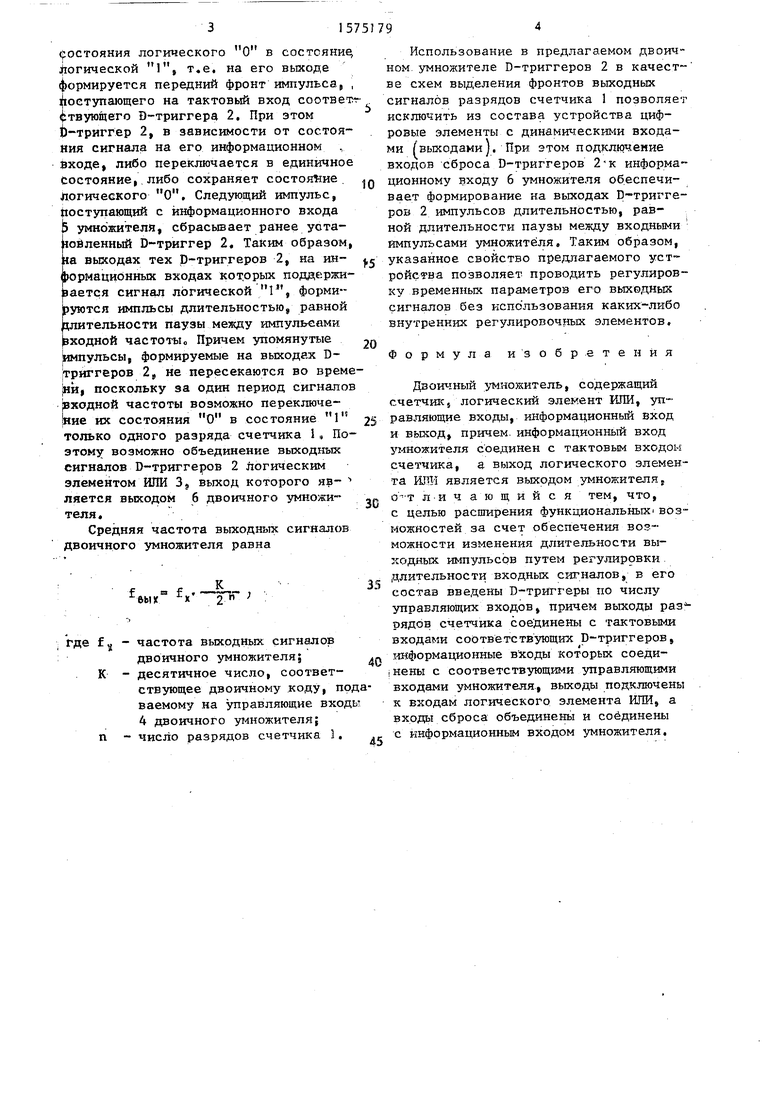

На чертеже приведена логическая схема двоичного умножителя.

Двоичный умножитель содержит счет - чик I, D-триггеры 2, логический элемент ИЛИ 3, управляющие входы 4, информационный вход 5 и выход 6.

Информационный вход 5 двоичного умножителя соединен с тактовым входам

счетчика 1 и с входами сброса D-трш геров 2. Выходы разрядов счетчика 1 подключены к тактовым входам соответствующих D-триггеров 2, информационные входы которых соединены с управляющими входами 4 умножителя. Выходы D-триг геров 2 объединяются логическим элементом ИЛИ 3, выход которого является выходом 6 двоичного умножителя.

Устройство работает следующим образом.

На управляющие входы 4 двоичного умножителя подается информация о коэффициенте умножения, на информационный вход 5 - сигналы умножаемой частоты, которые подсчитываются счетчиком I по заднему фронту каждого импульса. В момент прихода очередного заднего фронта входного импульса один из разрядов счетчика 1 переходит из

СД J СП

1

со

315

достояния логического 0м в состояние логической 1, т.е. на его выходе формируется передний фронт импульса, , поступающего на тактовый вход соответ- бтвующего В-триггера 2. При этом Й-триггер 2, в зависимости от состояния сигнала на его информационном входе, либо переключается в единичное Состояние, либо сохраняет состояние Логического О. Следующий импульс, поступающий с информационного входа Ь умножителя, сбрасывает ранее уста- овленный D-триггер 2. Таким образом, ha выходах тех D-трнггеров 2, на ин

t

ормационных входах которых поддерживается сигнал логической 1я, формируются импльсы длительностью, равной длительности паузы между импульсами входной частотыо Причем упомянутые импульсы, формируемые на выходах D- тряггеров 2, не пересекаются во времени, поскольку за один период сигналов рходной частоты возможно переключе- Ьше их состояния О в состояние 1 только одного разряда счетчика 1. Поэтому возможно объединение выходных сигналов D-триггеров 2 логическим элементом ИЛИ 3, выход которого яв- ляется выходом 6 двоичного умножителя.

Средняя частота выходных сигналов двоичного умножителя равна

6ЫХ

Ј 8 - частота выходных сигналов

двоичного умножителя; К - десятичное число, соответствующее двоичному коду, подаваемому на управляющие входь- 4 двоичного умножителя;

п - число разрядов счетчика 1.

5

0

5

0

5

0

5

Использование в предлагаемом двоичном умножителе D-триггеров 2 в качест- ве схем выделения фронтов выходных сигналов разрядов счетчика 1 позволяет исключить из состава устройства цифровые элементы с динамическими входами Iвыходами), При этом подключение входов сброса D-триггеров 2-к информа- ционному входу 6 умножителя обеспечивает формирование на выходах D-триггеров 2 импульсов длительностью, равной длительности паузы между входными импульсами умножителя. Таким образом, указанное свойство предлагаемого устройства позволяет проводить регулировку временных параметров его выходных сигналов без использования каких-либо внутренних регулировочных элементов.

Формула изобретения

Двоичный умножитель, содержащий счетчик, логический элемент ИЛИ, управляющие входы, информационный вход и выход, причем информационный вход умножителя соединен с тактовым входоп счетчика, а выход логического элемента ЩЩ является выходом умножителя, обличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения во можности изменения длительности выходных импульсов путем регулировки длительности входных сигналов, в его состав введены D-триггеры по числу управляющих входов, причем выходы рядов счетчика соединены с тактовыми входами соответствующих D-триггеров, информационные входы которых соеди- iнены с соответствующими управляющими входами умножителя, выходы подключены к входам логического элемента ИЛИ, а входы сброса объединены и соединены с информационным входом умножителя.

Составитель С.Сушко Редактор Н.Киштулннец Текред Л.Сердюкова Корректор О.Ципле

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| Селектор импульсов заданной кодовой комбинации | 1987 |

|

SU1457169A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при обработке сигналов частотных датчиков. Целью изобретения является расширение функциональных возможностей двоичного умножителя за счет изменения длительности выходных импульсов путем регулировки длительности входных сигналов. Умножитель содержит счетчик, D-триггеры и логический элемент ИЛИ, причем информационный вход умножителя соединен с тактовым входом счетчика и со входом сброса D-триггеров, тактовые входы которых - к управляющим входам задания коэффициента умножения, а выходы D-триггеров объединяются логическим элементом ИЛИ. Длительность выходных сигналов в предложенном двоичном умножителе равна длительности паузы между его входными импульса. 1 ил.

Заказ 1785

Тираж 565

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ C( 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Данчеев В.ГГ | |||

| Цифро-частотные вычислительные устройства, - М.: Энергия, J976, с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

Авторы

Даты

1990-06-30—Публикация

1985-10-25—Подача