Изобретение относится к автоматике и вычислительной технике и может быть использовано для разработки микросхем троичной логики, позволяющей повысить производительность устройств, унифицированных с микросхемами двоичной логики.

Известны базовые логические элементы (ЛЭ) двоичной логики, такие как "инвертор" (он же элемент отрицания "НЕ"). Наиболее распространенным таким ЛЭ является, например, инвертор, выполненный по ТТЛ-технологии [1] - "Популярные цифровые микросхемы, Челябинск, "Металлургия", 1988. Он содержит (Рис.1.4, с.12, [1]) общую шину, шину источника положительного напряжения питания, входную и выходную шины, четыре резистора, один диод и пять транзисторов ТТЛ, собранные по схеме ЛЭ "НЕ". Этот инвертор не может выполнять функцию ЛЭ "НЕ" в троичной логике и имеет повышенное потребление энергии.

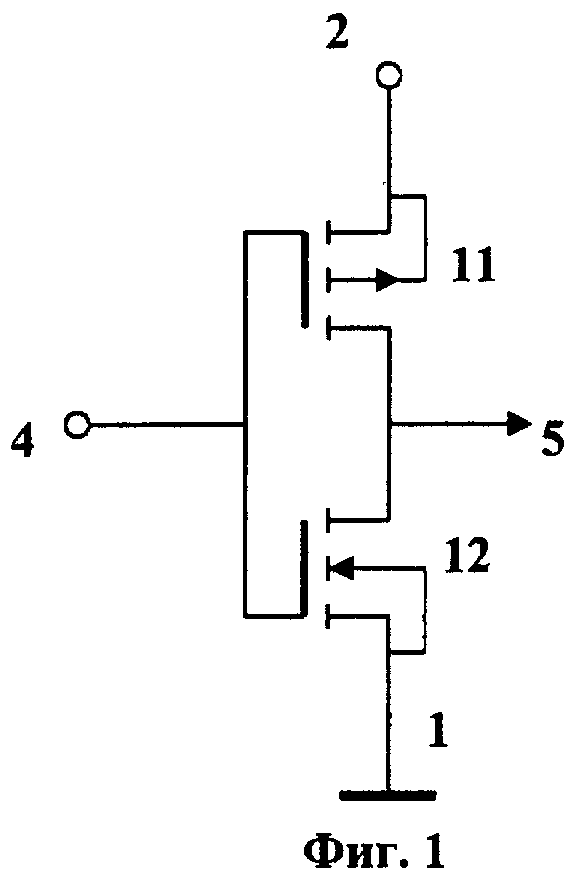

За прототип изобретения принят базовый ЛЭ "НЕ", выполненный по КМОП-технологии (Рис.2.4 с.194, [1]). Базовый ЛЭ (Фиг.1) содержит два последовательно соединенных МОП-транзистора 11 и 12, включенные между шиной 2 источника питания и общей шиной 1. Первый транзистор 11 с каналом р-проводимости, а второй транзистор 12 с каналом n-проводимости. Затворы транзисторов 11 и 12 соединены между собой и подключены к входной шине 4. Если на вход ЛЭ подано напряжение высокого уровня (состояние 1), то первый транзистор 11 закрывается, а второй 12 открывается и на выходе ЛЭ будет напряжение низкого уровня (состояние 0).

Известно также, что последовательное преобразование сигнала двумя ЛЭ "НЕ" в двоичной логике (двойное отрицание) приводит к получению исходного сигнала, что иллюстрирует таблица истинности 1.

В двоичной логике используют однополярные сигналы алфавита {0,1} положительной логики или {0,-1} отрицательной логики.

В троичной логике используют биполярные сигналы алфавита {-1,0,1}, и базовыми логическими элементами "Отрицание" в троичной логике могут быть такие элементы, как:

- "1НЕ" или первое отрицание;

- "2НЕ" или второе отрицание.

Функция "1HE" (первое отрицание) представляется таблицей истинности 2:

Функция "2НЕ" (второе отрицание) представлена таблицей истинности 3:

Известные логические элементы двоичной логики не реализуют функции троичной логики. Техническим результатом изобретения является увеличение производительности устройств логики при их использовании в вычислительной технике по сравнению с аналогичными устройствами двоичной логики.

Предложены и описываются два варианта новых устройства троичной логики, обеспечивающие новые логические функции, связанные одним изобретательским замыслом.

Первый вариант исполнения изобретения

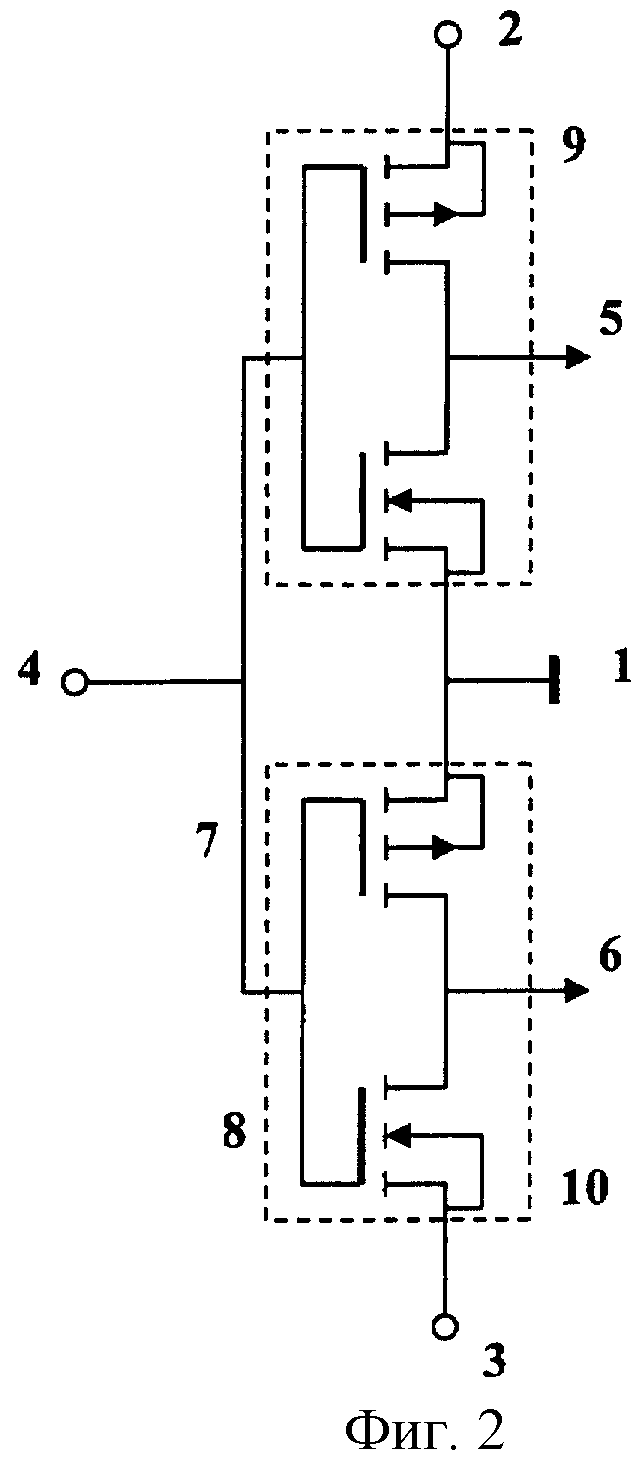

Новый элемент троичной логики - ЛЭ "1 НЕ" создан на основе двух базовых ЛЭ "НЕ" двоичной логики. На Фиг.2 показана схема нового ЛЭ, выполненного по КМОП технологии, а на Фиг.1 - схема базового ЛЭ двоичной логики "НЕ" (инвертор).

Базовый ЛЭ содержит общую шину 1, шину 2 источника питания, входную шину 4, выходную шину 5 и два МОП-транзистора 11 и 12. Причем первый транзистор 11 с каналом р-проводимости, а второй 12 - с каналом n-проводимости. Транзисторы соединены последовательно и подключены к шине питания 2 и к общей шине 1. Затворы транзисторов соединены между собой и подключены к входной шине 4. Если на вход ЛЭ подано напряжение высокого уровня (состояние 1), то первый транзистор закрывается, а второй открывается и на выходе ЛЭ будет напряжение низкого уровня (состояние 0). Когда на входе напряжение низкого уровня (состояние 0), первый транзистор 11 открывается, а второй 12 - закрывается, и на выходе ЛЭ оказывается напряжение высокого уровня (состояние 1). При подаче на вход отрицательного напряжения (-1) состояние транзисторов не изменяется по сравнению с состоянием, которое было при низком напряжении на входе.

Таким образом, двоичный ЛЭ "НЕ" при биполярных напряжениях на входе работает в соответствии с таблицей истинности 4:

Новый логический элемент "1НЕ" (Фиг.2) содержит общую шину 1, шины 2 и 3 источников положительного и отрицательного напряжения, входную шину 4 и две выходные шины первую 5 (выход не отрицательных напряжений) и вторую 6 (выход не положительных напряжений) и два одинаковых элемента 9 и 10 двоичной логики "НЕ". Первый ЛЭ 9 включен в схему в обычном для двоичной логики режиме - между шиной 2 источника положительного напряжения и общей шиной 1 и работает в соответствие с таблицей истинности (Таблица 4). Второй ЛЭ 10 подключен клеммой для напряжения питания к общей шине 1, а клеммой для подключения общей шины подключен к шине 3 источника отрицательного напряжения питания. Входы логических элементов соединены и подключены к входной шине 4.

Второй логический элемент 10 в этой схеме работает следующим образом. Если на вход ЛЭ подано отрицательное напряжение высокого уровня (состояние -1), то первый транзистор 7 открывается, а второй транзистор 8 закрывается и на выходе 6 ЛЭ будет напряжение низкого уровня (состояние 0). Когда на входе напряжение низкого уровня (состояние 0), первый транзистор 7 закрывается, второй транзистор 8 открывается, и на выходе ЛЭ присутствует отрицательное напряжение высокого уровня (-1). При подаче на вход положительного напряжения (1) состояние транзисторов 7 и 8 не изменяется по сравнению с состоянием, которое было при низком напряжении на входе. Таким образом, второй двоичный ЛЭ "НЕ" при биполярных напряжениях на входе работает в соответствии с таблицей истинности 5:

В целом, новый элемент троичной логики "1НЕ" (первое отрицание) выполняет функцию в соответствии с таблицей истинности 6.

Общими элементами прототипа изобретения и устройства по первому варианту исполнения изобретения являются логический элемент двоичной логики - инвертор, общая шина, шина источника положительного напряжения питания, входная шина и одна выходная шина, к которой подключен выход инвертора.

Практически новое логическое устройство "Отрицание" - "1НЕ" может быть выполнено на логических элементах двоичной логики - инвертор серии, например, К561, выпускаемой промышленностью.

Второй вариант исполнения изобретения

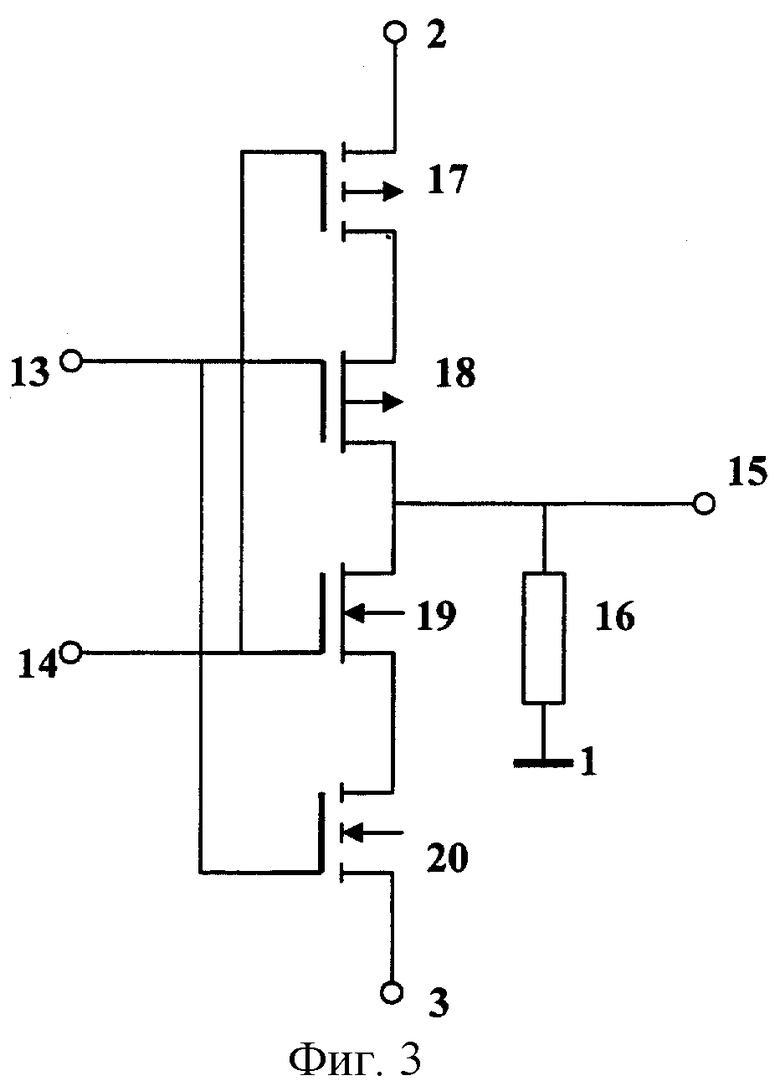

Второй вариант нового базового логического элемента троичной логики "2НЕ" (второе отрицание) может быть выполнен с использованием МОП-транзисторов, как показано на Фиг.3. Новый элемент содержит общую шину 1, шины 2 и 3 источников положительного и отрицательного напряжения, две входных шины 13 и 14, выходную шину 15, нагрузку 16 и четыре МОП транзистора 17, 18, 19, 20, соединенные между собой последовательно. Первый 17 и второй 18 транзисторы с каналом р-проводимости, третий 19 и четвертый 20 с каналом n-проводимости. При этом пороговые напряжения транзисторов такие, что каналы первого 17 и четвертого 20 транзисторов закрыты при нулевом напряжении на затворах, а у второго 18 и третьего 19 транзисторов каналы открыты при нулевом напряжении на затворах. Первый 17 и второй 18 транзисторы соединены последовательно и включены между шиной 2 положительного напряжения питания и выходной шиной 15. Третий 19 и четвертый 20 транзисторы соединены последовательно и включены между выходной шиной 15 и шиной 3 отрицательного напряжения питания. Затворы первого 17 и третьего 19 транзисторов соединены между собой и подключены к второй входной шине 14, а затворы второго 18 и четвертого 20 транзисторов соединены между собой и подключены к первой входной шине 13. Следует отметить, что первый вход 13 предназначен для приема не отрицательных сигналов, а второй вход 14 - для приема не положительных сигналов.

Новое устройство работает следующим образом. Если на первый вход 13 подается напряжение низкого уровня, а на второй вход 14 отрицательное напряжение высокого уровня, то первый транзистор 17 открывается и через открытый второй транзистор 18 положительное напряжение шины 2 передается на выходную шину 15 и выделяется на элементе нагрузки 16. При этом цепь от шины 3 источника отрицательного напряжения к выходной шине разомкнута, так как третий транзистор 19 запирается при отрицательном напряжении на затворе и четвертый транзистор 20 закрыт при низком уровне напряжения на затворе.

Если на первый входа 13 подается положительное напряжение высокого уровня, а на второй вход 14 отрицательное напряжение высокого уровня, то разомкнуты обе цепи: от шины 2 источника положительного напряжения к выходной шине 15 и от шины 3 источника отрицательного напряжения к выходной шине 15, так как второй 18 и третий 19 транзисторы закрыты. При этом выходная шина 15 находится под потенциалом общей шины 1 благодаря связи через нагрузку.

Если на первый вход 13 подается положительное напряжение высокого уровня, а на второй вход 14 напряжение низкого уровня, то четвертый транзистор 20 открывается и через открытый третий транзистор 19 отрицательное напряжение от шины 3 передается на выходную шину 15 и выделяется на нагрузке 16. При этом цепь от шины 2 источника положительного напряжения к выходной шине 15 разомкнута, так как второй транзистор 18 запирается при положительном напряжении на затворе и первый транзистор 17 закрыт при низком уровне напряжения на затворе.

Новый ЛЭ троичной логики "2НЕ" работает в соответствии с таблицей истинности 7:

Следует отметить состояние ЛЭ, когда оба входа находятся при низком уровне напряжений. В этом случае первый 17 и четвертый 20 транзисторы закрыты, и выходная шина 15 находится под потенциалом общей шины 1 из-за связи ее через нагрузку 16.

При выполнении ЛЭ "2НЕ" с резистором в качестве нагрузки 16 у него повышенное потребление энергии и пониженное быстродействие по сравнению с элементами двоичной логики. Так, при логических состояниях, когда открыта любая из цепей между источниками питания и выходной шиной через резистор нагрузки постоянно протекает ток. Уменьшить величину тока путем увеличения сопротивления резистора не удается, так как при этом снижается быстродействие из-за увеличения постоянной времени разряда емкости нагрузки через резистор. Этот недостаток устраняется при использовании в качестве нагрузки нового устройства с управляемой проводимостью (Фиг.4).

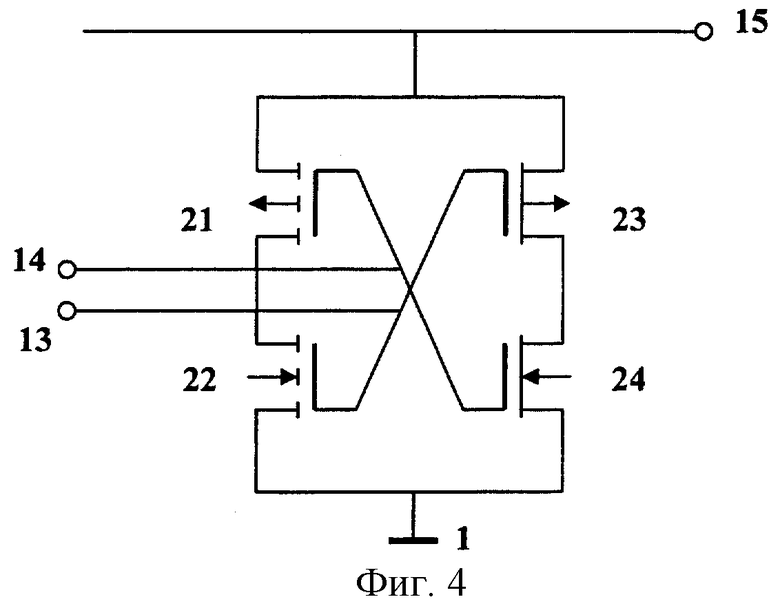

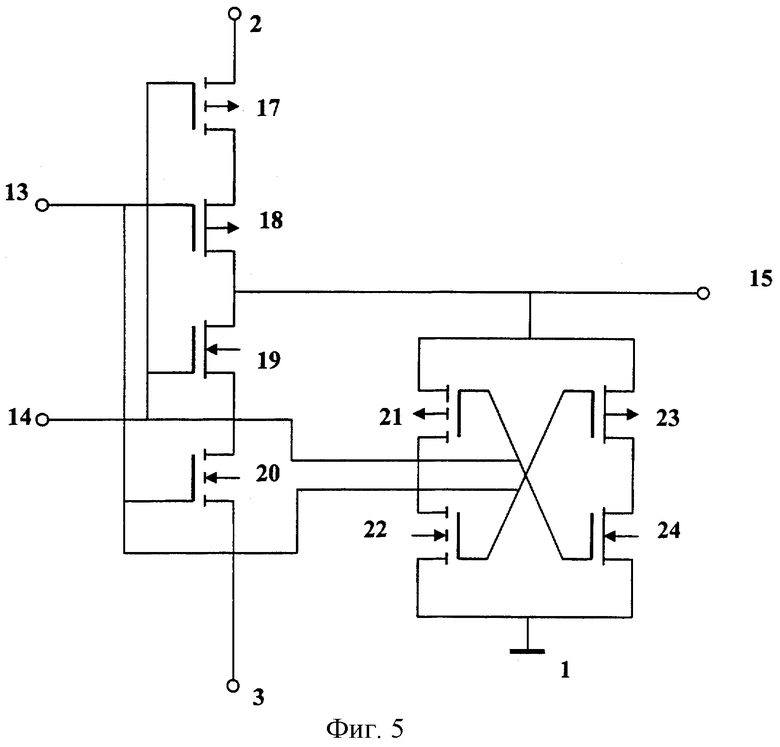

Электрическая схема такого устройства показана на Фиг.5. Элемент нагрузки содержит четыре МДП-транзистора 21, 22, 23 и 24. Первый 21 и третий 23 транзисторы с каналами р-проводимости, а второй 22 и четвертый 24 с каналами n-проводимости. Первый 21 и второй 22 транзисторы соединены последовательно и включены между выходной шиной и общей шиной. Третий 23 и четвертый 24 транзисторы также соединены последовательно и включены между выходной шиной 15 и общей шиной 1. При этом пороговые напряжения первого и второго транзисторов такие, что их каналы зарыты при нулевом напряжении на затворах, а у третьего и четвертого транзисторов каналы открыты при нулевом напряжении на затворах.

Затворы первого 21 и четвертого 24 транзисторов соединены между собой и подключены к второй входной шине 14, затворы второго 22 и третьего 23 транзисторов соединены между собой и подключены к первой входной шине 13.

Элемент нагрузки работает следующим образом. Когда на входах ЛЭ "2НЕ" присутствует напряжение низкого уровня, третий и четвертый транзисторы открыты, и элемент нагрузки имеет высокую проводимость, обеспечивая быстрый разряд емкости нагрузки. При этом цепи от шин 2 и 3 источников питания к выходной шине 15 разомкнуты и потребление энергии минимально, как в ЛЭ двоичной логики.

Если на обоих входах присутствуют напряжения высокого уровня: на первом входе 13 положительного напряжения, а на втором входе 14 отрицательного напряжения, то первый 21 и второй 22 транзисторы открываются, и элемент нагрузки имеет высокую проводимость, обеспечивая быстрый разряд емкости нагрузки. При этом цепи от источников питания к выходной шине 15 разомкнуты и потребление энергии минимально.

Если высокий уровень напряжения имеет место только на одной из входных шин положительного напряжения на первой 13 или отрицательного на второй 14, то один из транзисторов третий 23 или четвертый 24 соответственно закрывается и вся правая цепь (транзисторы 23 и 24) становится высокоомной. При этом в левой цепи (транзисторы 21 и 22) открывается только один из транзисторов, и вся цепь остается высокоомной. Таким образом, в целом элемент нагрузки в этих логических состояниях имеет большое сопротивление, чем обеспечивается минимальное потребление энергии при открытых цепях от источников питания к выходной шине 13.

Общими элементами прототипа изобретения и устройства по второму варианту исполнения изобретения являются общая шина, шина источника положительного напряжения питания, одна входная шина, выходная шина и нагрузка.

Практически логическое устройство "2НЕ" может быть выполнено на транзисторах, выпускаемых промышленностью:

- транзистор 8 - IRF9640;

- транзистор 9 - IRF9510;

- транзистор 10 - IRF120;

- транзистор 11 - IRFP244;

- транзистор 12 - ZVP4424A;

- транзистор 13 - ZVN4424A;

- транзистор 14 - IRF9140;

- транзистор 15 - IRF710.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ УСТРОЙСТВО "И" | 2004 |

|

RU2281605C2 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО "ИЛИ" | 2004 |

|

RU2278469C1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА ВО МНОГОЗНАЧНЫЙ КОД (ВАРИАНТЫ) | 1997 |

|

RU2109400C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ЭЛЕМЕНТ | 2020 |

|

RU2729887C1 |

| ТРОИЧНЫЙ К-МОП-С ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕ" | 2011 |

|

RU2481701C2 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ЭЛЕМЕНТ "МИНИМУМ" | 2020 |

|

RU2727145C1 |

Изобретение относится к автоматике и вычислительной технике. Технический результат заключается в упрощении инвертора троичной логики. Устройство "Отрицание" (фиг.2) содержит последовательно соединенные между шинами источников положительного (2) и отрицательного (3) напряжений питания логические элементы (ЛЭ) (9, 10) двоичной логики - инверторы (ЛЭ - "НЕ"), входы которых соединены с входной шиной (4), а выходы - соответственно с первой (5) и второй (6) выходными шинами. Упрощение достигается тем, что точка соединения выводов питания обоих ЛЭ (9, 10) подключена к общей шине, поэтому по напряжениям на двух выходных шинах (5, 6) можно судить о трех потенциальных значениях входного троичного сигнала. 2 н. и 1 з.п. ф-лы, 5 ил., 7 табл.

| Устройство для изготовления пружин | 1988 |

|

SU1563821A2 |

| КМДП-инвертор | 1986 |

|

SU1370735A1 |

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

Авторы

Даты

2006-11-20—Публикация

2004-11-01—Подача