Изобретение относится к автоматике и вычислительной технике и может быть использовано для разработки микросхем троичной логики, позволяющей повысить производительность устройств, унифицированных с микросхемами двоичной логики.

Известны базовые логические элементы (ЛЭ) двоичной логики, такие как: «ИЛИ-НЕ». Наиболее распространенным аналогами являются, например, ЛЭ, выполненные по ТТЛ-технологии [1] - Шило В.Л. Популярные цифровые микросхемы, Челябинск, «Металлургия», 1988. Он содержит (с.37, Рис. 1.21. [1]): общую шину, шину источника положительного напряжения питания, входную и выходную шины, пять резисторов, один диод и шесть транзисторов, соединенные по схеме ЛЭ «ИЛИ-НЕ». Этот ЛЭ не может выполнять функцию «ИЛИ» в троичной логике и имеет повышенное потребление энергии.

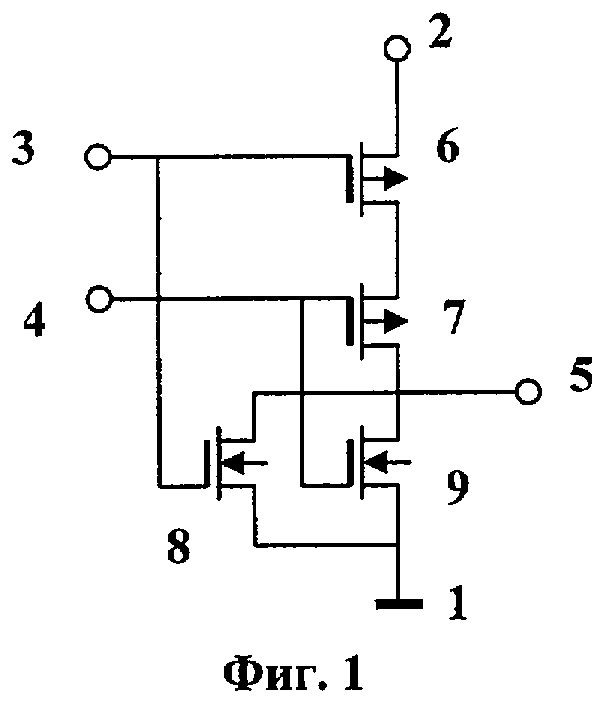

За прототип изобретения принят базовый ЛЭ «ИЛИ-НЕ», выполненный по КМОП-технологии (Рис. 2.10, с.203, [1]). На Фиг.1 показана электрическая схема двоичного ЛЭ «ИЛИ-НЕ», выполненного по КМОП-технологии. ЛЭ содержит: общую шину 1, шину 2 источника положительного напряжения, первую 3 и вторую 4 входные шины и четыре МОП-транзистора 6, 7, 8 и 9. Первый 6 и второй 7 транзисторы с каналом р-проводимости, третий 8 и четвертый 9 с каналом n-проводимости.

В схеме ЛЭ «ИЛИ-НЕ» транзисторы с каналом р-проводимости (транзисторы 6 и 7) соединены последовательно и подключены к шине питания 2 с одной стороны и к выходной шине 5 - с другой. Транзисторы 8 и 9 n-проводимости соединены параллельно и подключены к выходной шине 5 и общей шине 1. ЛЭ работает следующим образом. Если на обоих входах присутствуют напряжения низкого уровня, то оба транзистора р-проводимости открыты, транзисторы n-проводимости закрыты, и на выходной шине будет напряжение высокого уровня. При всех других комбинациях напряжений на входных шинах один из транзисторов р-проводимости или оба эти транзистора будут закрыты, а транзисторы n-проводимости (по одному или оба) открыты, и на выходной шине будет напряжение низкого уровня. Таким образом, этот элемент выполняет функцию «ИЛИ» с отрицанием в соответствии с таблицей истинности 1.

В двоичной логике используют однополярные сигналы алфавита {0, 1} положительной логики, или {0,-1} отрицательной двоичной логики.

В троичной логике используют биполярные сигналы алфавита {-1, 0, 1}. Базовым логическим элементом «ИЛИ» в троичной логике может быть элемент, который выполняет функцию в соответствии с таблицей истинности 2.

Логические элементы двоичной логики не реализуют функции троичной логики. Техническим результатом изобретения является увеличение производительности устройств логики, при их использовании в вычислительной технике, по сравнению с аналогичными устройствами двоичной логики.

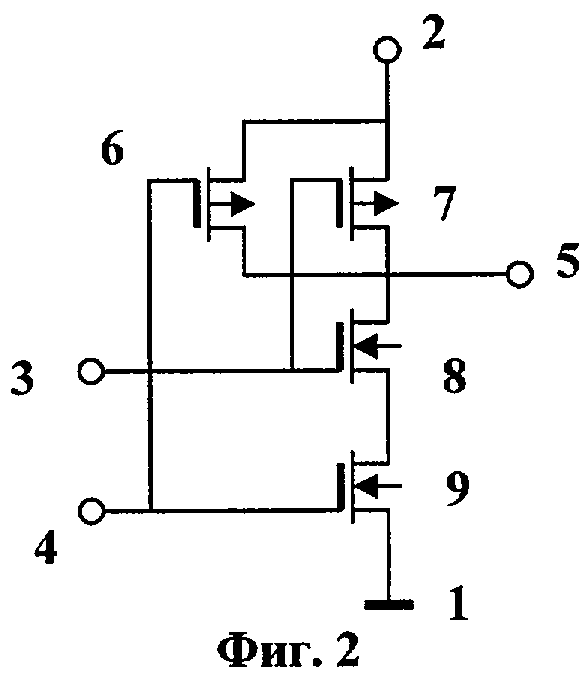

Используя ЛЭ «ИЛИ-НЕ» и ЛЭ «И-НЕ» двоичной логики, можно реализовать функцию троичной логики «ИЛИ». ЛЭ «И-НЕ» (Фиг.2) содержит: общую шину 1, шину 2 источника положительного напряжения, первую 3 и вторую 4 входные шины и четыре МОП-транзистора 6, 7, 8 и 9. Первый 6 и второй 7 транзисторы с каналом р-проводимости, третий 8 и четвертый 9 - с каналом n-проводимости. Транзисторы 6 и 7 соединены параллельно и подключены к шине питания 2 с одной стороны и к выходной шине 5 - с другой. Транзисторы 8 и 9 соединены последовательно и подключены к выходной шине 5 и общей шине.

ЛЭ работает следующим образом. Если на обоих входах присутствуют напряжения высокого уровня, то оба транзистора р-проводимости закрыты, транзисторы n-проводимости открыты, и на выходной шине 5 будет напряжение низкого уровня. При всех других комбинациях напряжений на входных шинах один из транзисторов р-проводимости или оба эти транзистора будут открыты, а транзисторы n-проводимости (по одному или оба) закрыты, и на выходной шине будет напряжение высокого уровня. Таким образом, этот элемент выполняет функцию «И» с отрицанием в соответствии с таблицей истинности 3.

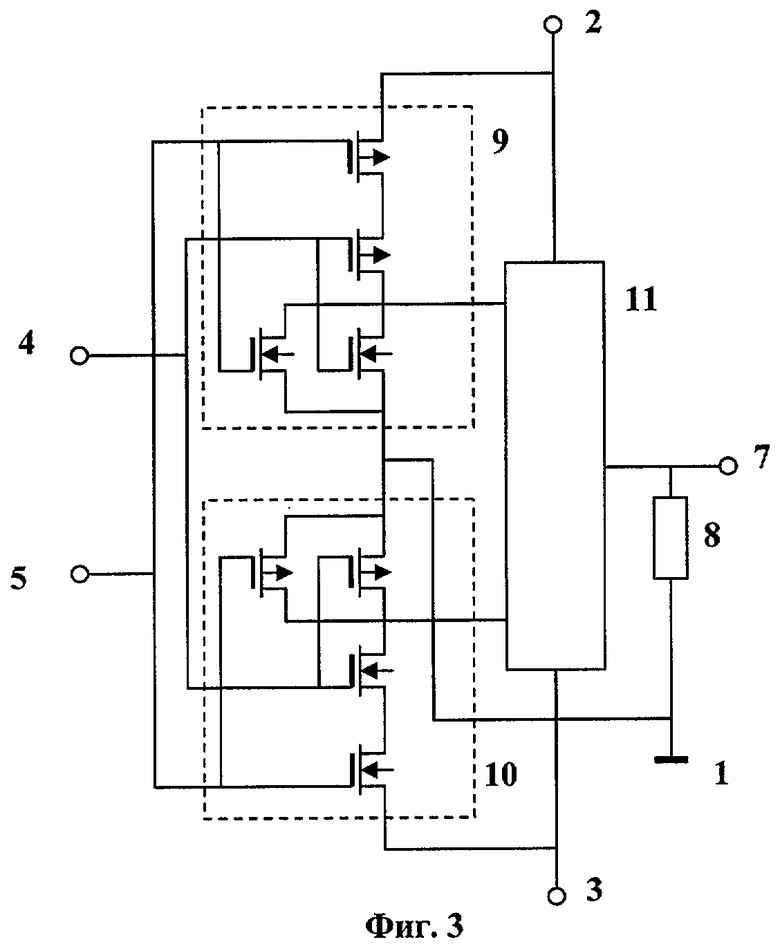

Устройство для реализации функции троичной логики «ИЛИ» (Фиг.3) содержит: общую шину 1, шину 2 источника положительного напряжения, шину 3 источника отрицательного напряжения, первую 4 и вторую 5 входные шины, ЛЭ «ИЛИ-НЕ» 9 и ЛЭ «И-НЕ» 10, оба ЛЭ двоичной положительной логики, которые выполнены по КМОП-технологии, и элемент объединения сигналов 11. При этом первый ЛЭ 9 подключен к шине 2 положительного напряжения питания и к общей шине 1, а второй логический элемент 10 подключен к общей шине клеммой для подключения питания и к шине 3 отрицательного напряжения питания клеммой для подключения общей шины. Одноименные входы первого 9 и второго 10 ЛЭ соединены между собой и подключены к входным шинам 4 и 5. Выход первого ЛЭ 9 подключен к первому входу элемента объединения сигналов 11, выход второго ЛЭ 10 подключен ко второму входу элемента 11, выход элемента 11 подключен к выходной шине 7 и нагрузке 8.

Первый ЛЭ 9, при не отрицательных сигналах на входах, работает так же, как в двоичной логике. На напряжения отрицательной полярности этот элемент реагирует, как на напряжения низкого уровня. Таким образом, при биполярных сигналах на входах ЛЭ 9 работает в соответствии с таблицей истинности 4.

Второй логический элемент 10 работает следующим образом. При не отрицательных напряжениях на входных шинах транзисторы р-проводимости заперты, а транзисторы n-проводимости открыты, и напряжение источника отрицательного напряжения передается на выход этого ЛЭ. Если на одной или на двух входных шинах присутствует отрицательное напряжение, то один или оба транзистора с каналом р-проводимости открыты, и выход ЛЭ находится под напряжением низкого уровня. При этом один или оба транзистора n-проводимости закрыты. Таким образом, при биполярных сигналах на входах ЛЭ 10 работает в соответствии с таблицей истинности 5.

Если в качестве элемента объединения 11 использовать суммирующий операционный усилитель, то логические состояния определяются простым суммированием уровней сигналов с выходов первого и второго ЛЭ в соответствии с таблицей истинности 6.

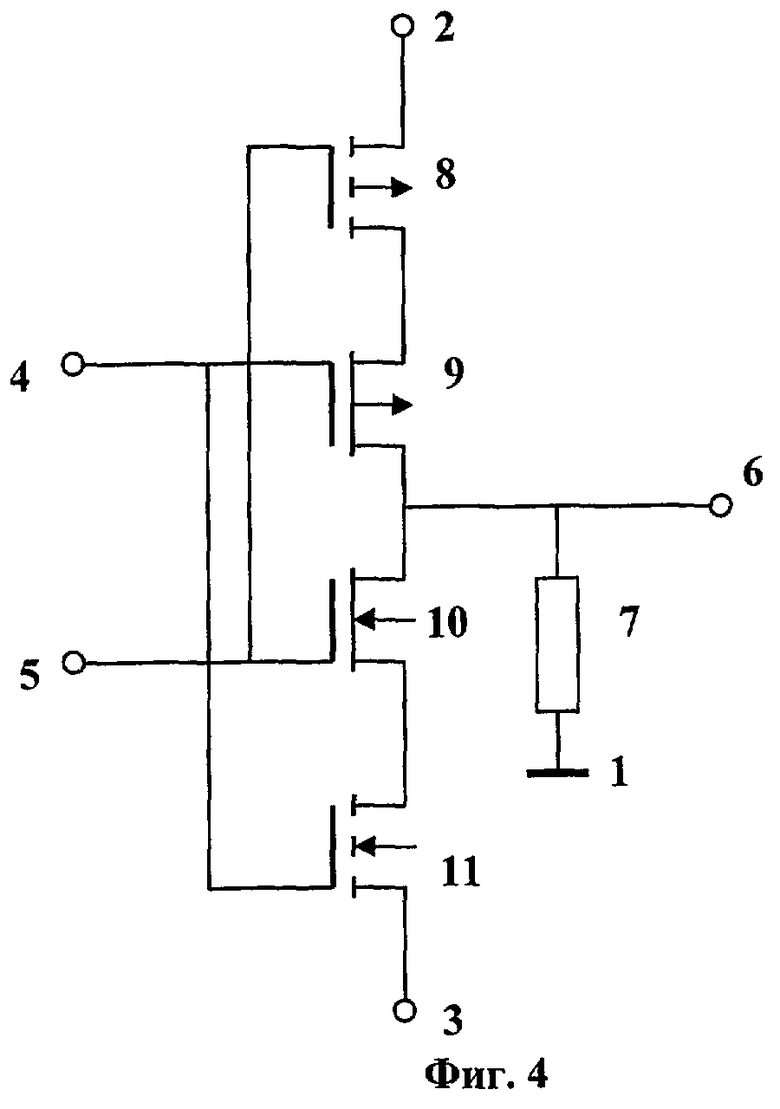

Суммирующий операционный усилитель - сложное и энергоемкое устройство, поэтому целесообразно вместо него использовать новый ЛЭ «2НЕ» (второе отрицание) троичной логики. Этот элемент может быть выполнен с использованием МОП-транзисторов, как показано на Фиг.4. ЛЭ «2НЕ» содержит: общую шину 1, шины 2 и 3 источников положительного и отрицательного напряжения, две входных шины 4 и 5, выходную шину 6, нагрузку 7 и четыре МОП-транзистора 8, 9, 10 и 11, соединенные между собой последовательно. Первый 8 и второй 9 транзисторы с каналом р-проводимости, третий 10 и четвертый 11 - с каналом n-проводимости. При этом пороговые напряжения транзисторов такие, что каналы первого 8 и четвертого 11 транзисторов закрыты при нулевом напряжении на затворах, а у второго 9 и третьего 10 транзистора каналы открыты при нулевом напряжении на затворах. Первый 8 и второй 9 транзисторы соединены последовательно и включены между шиной 2 положительного напряжения питания и выходной шиной 6. Третий 10 и четвертый 11 транзисторы соединены последовательно и включены между выходной шиной 6 и шиной 3 отрицательного напряжения питания. Затворы первого 8 и третьего 10 транзисторов соединены между собой и подключены ко второй входной шине 5, а затворы второго 9 и четвертого 11 транзисторов соединены между собой и подключены к первой входной шине 4. Следует отметить, что первый вход 4 предназначен для приема не отрицательных сигналов, а второй вход 5 - для приема не положительных сигналов.

Это устройство работает следующим образом. Если на первый вход 4 подается напряжение низкого уровня, а на второй вход 5 - отрицательное напряжение высокого уровня, первый транзистор 8 открывается, и через открытый второй транзистор 9 положительное напряжение шины 2 передается на выходную шину 6 и выделяется на элементе нагрузки 7. При этом цепь от шины 3 источника отрицательного напряжения к выходной шине разомкнута, так как третий транзистор 10 запирается при отрицательном напряжении на затворе, и четвертый транзистор 11 закрыт при низком уровне напряжения на затворе.

Если на первый вход 4 подается положительное напряжение высокого уровня и на второй вход 5 отрицательное напряжение высокого уровня, то разомкнуты обе цепи: от источника положительного напряжения (шина 2) к выходной шине 6 и от источника отрицательного напряжения (шина 3) к выходной шине 6, так как второй 8 и третий 9 транзисторы закрыты. При этом выходная шина находится под потенциалом общей шины 1 через связь с нагрузкой 7.

Если на первый вход 4 подается положительное напряжение высокого уровня, а на второй вход 5 - напряжение низкого уровня, то четвертый транзистор 11 открывается, и через открытый третий транзистор 10 отрицательное напряжение от шины 3 передается на выходную шину 6 и выделяется на нагрузке 7. При этом цепь от шины 2 источника положительного напряжения к выходной шине 6 разомкнута, так как второй транзистор 9 запирается при положительном напряжении на затворе, и первый транзистор 8 закрыт при низком уровне напряжения на затворе. ЛЭ троичной логики «2НЕ» работает в соответствии с таблицей истинности 7:

Следует отметить состояние ЛЭ (Фиг.4), когда оба входа 4 и 5 находятся при низком уровне напряжений. В этом случае первый 8 и четвертый 11 транзисторы закрыты, и выходная шина 6 находится под потенциалом общей шины 1 из-за ее связи с нагрузкой 7.

При выполнении ЛЭ «2НЕ» с резистором в качестве нагрузки 7 у него повышенное потребление энергии и пониженное быстродействие по сравнению с элементами двоичной логики. Так, при логических состояниях, когда открыта любая из цепей между источниками питания и выходной шиной, через резистор нагрузки постоянно протекает ток. Уменьшить величину тока путем увеличения сопротивления резистора не удается, так как при этом снижается быстродействие из-за увеличения постоянной времени разряда емкости нагрузки через резистор. Этот недостаток устраняется при использовании в качестве нагрузки нового устройства с управляемой проводимостью.

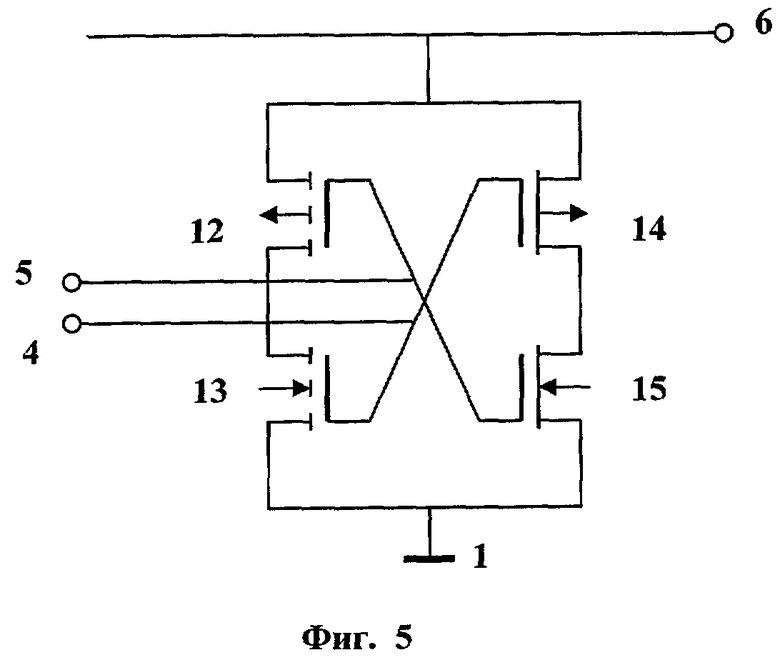

Электрическая схема такого устройства показана на Фиг.5. Элемент нагрузки содержит четыре МДП-транзистора 12, 13, 14 и 15. Первый 12 и третий 14 транзисторы, с каналами р-проводимости, а второй 13 и четвертый 15, с каналами n-проводимости. Первый 12 и второй 13 транзисторы соединены последовательно и включены между выходной шиной и общей шиной. Третий 14 и четвертый 15 транзисторы также соединены последовательно и включены между выходной шиной 6 и общей шиной 1. При этом пороговые напряжения первого и второго транзисторов такие, что их каналы зарыты при нулевом напряжении на затворах, а у третьего и четвертого транзисторов каналы открыты при нулевом напряжении на затворах.

Затворы первого 12 и четвертого 15 транзисторов соединены между собой и подключены ко второй входной шине 5, затворы второго 13 и третьего 14 транзисторов соединены между собой и подключены к первой входной шине. 4.

Элемент нагрузки работает следующим образом. Когда на входах ЛЭ «2НЕ» присутствует напряжение низкого уровня, третий и четвертый транзисторы открыты, и элемент нагрузки имеет высокую проводимость, обеспечивая быстрый разряд емкости нагрузки. При этом цепи от шин 2 и 3 источников питания к выходной шине 6 разомкнуты, и потребление энергии минимально, как в ЛЭ двоичной логики.

Если на обоих входах присутствуют напряжения высокого уровня: на первом входе 4 положительного напряжения, а на втором входе 5 отрицательного напряжения, то первый 12 и второй 13 транзисторы открываются, и элемент нагрузки имеет высокую проводимость, обеспечивая быстрый разряд емкости нагрузки. При этом цепи от источников питания к выходной шине 6 разомкнуты, и потребление энергии минимально.

Если высокий уровень напряжения имеет место только на одной из входных шин положительного напряжения на первой 4 или отрицательного на второй 5, то один из транзисторов третий 14 или четвертый 15, соответственно, закрывается, и вся правая цепь (транзисторы 14 и 15) становится высокоомной. При этом в левой цепи (транзисторы 12 и 13) открывается только один из транзисторов, и вся цепь остается высокоомной. Таким образом, в целом элемент нагрузки в этих логических состояниях имеет большое сопротивление, чем обеспечивается минимальное потребление энергии при открытых цепях от источников питания к выходной шине 4.

Общими элементами прототипа изобретения и устройства являются логический элемент «ИЛИ-НЕ» положительной двоичной логики, выполненный по КМОП-технологии, общая шина, первая и вторая входные шины, шина положительного напряжения питания.

Практически логическое устройство «ИЛИ» может быть выполнено на ЛЭ «ИЛИ-НЕ» и ЛЭ «И-НЕ» двоичной логики, например, серии 561, выпускаемой промышленностью.

Логическое устройство «2НЕ», входящее в состав устройства троичной логики «ИЛИ», может быть выполнено на транзисторах, выпускаемых промышленностью:

- транзистор 8 - IRF9640;

- транзистор 9 - IRF9510;

- транзистор 10 - IRF120;

- транзистор 11 - IRFP244;

- транзистор 12 - ZVP4424A;

- транзистор 13 - ZVN4424A;

- транзистор 14 - IRF9140;

- транзистор 15 - IRF710.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ УСТРОЙСТВО "И" | 2004 |

|

RU2281605C2 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО "ОТРИЦАНИЕ" (ВАРИАНТЫ) | 2004 |

|

RU2287895C2 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ЭЛЕМЕНТ | 2020 |

|

RU2729887C1 |

| КМОП КНИ ИНТЕГРАЛЬНАЯ МИКРОСХЕМА С ПОВЫШЕННОЙ РАДИАЦИОННОЙ СТОЙКОСТЬЮ | 2013 |

|

RU2545325C1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ЭЛЕМЕНТ "МИНИМУМ" | 2020 |

|

RU2727145C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ПАРАЛЛЕЛЬНЫЙ ТРОИЧНЫЙ КОМПАРАТОР | 2020 |

|

RU2723672C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для разработки микросхем троичной логики. Техническим результатом является повышение производительности устройства. Устройство содержит элемент двоичной положительной логики «ИЛИ-НЕ», элемент двоичной положительной логики «И-НЕ», выполненные по КМОП технологии, общую шину, шину источника положительного напряжения, шину источника отрицательного напряжения, две входные шины, элемент объединения сигналов. 2 з.п. ф-лы, 5 ил., 7 табл.

| ШИЛО В.Л | |||

| Популярные цифровые микросхемы | |||

| - Челябинск: Металлургия, 1988, с.203, рис.2.10 | |||

| М-ЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1994 |

|

RU2079970C1 |

| Троичный дизъюнктор на МДП-транзисторах | 1987 |

|

SU1707757A1 |

| Трехзначный элемент дизъюнкции | 1982 |

|

SU1018251A1 |

| US 4107549 A, 15.08.1978 | |||

| СПОСОБ ИЗГОТОВЛЕНИЯ ФРИКЦИОННОГО ИЗДЕЛИЯ С НАКЛАДКАМИ ИЗ МЕТАЛЛОКЕРАМИКИ НА ОСНОВЕ МЕДИ | 1997 |

|

RU2114719C1 |

Авторы

Даты

2006-06-20—Публикация

2004-11-01—Подача